UNIVERSIDAD DE BUENOS AIRES

FACULTAD DE CIENCIAS EXACTAS Y NATURALES

DEPARTAMENTO DE COMPUTACIÓN

# Optimización de cómputo QM/MM empleando arquitecturas masivamente paralelas

Tesis presentada para optar al título de

Licenciado en Ciencias de la Computación

Manuel Ferrería y Juan Pablo Darago

Director: Dr. Esteban Mocskos

Codirector: Dr. Mariano Camilo González Lebrero

Buenos Aires, 2015

## RESUMEN

Este trabajo se enfoca en acelerar cálculos de estructura electrónica mediante el uso de arquitecturas de procesadores especializados en cómputo masivos. Se partió de LIO, una implementación ya existente de los algoritmos dados por la Teoría de los Funcionales de la Densidad (DFT) que ya hacía uso de placas de video para cómputo general (GPGPU). Este programa se adaptó para hacer uso de las prestaciones ofrecidas por multiprocesadores, GPUs modernas, y para el coprocesador numérico Xeon Phi de Intel.

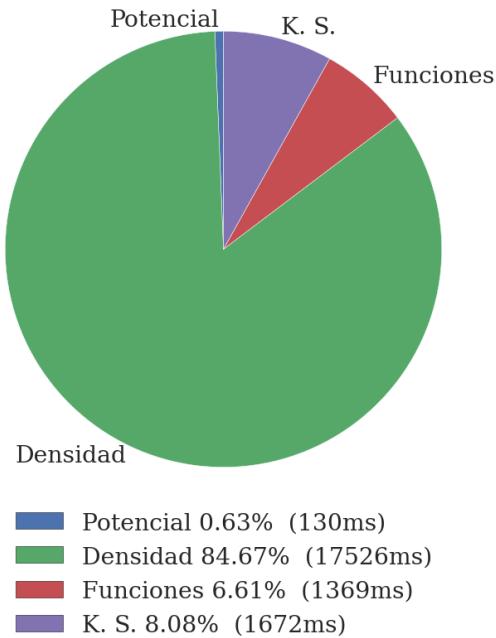

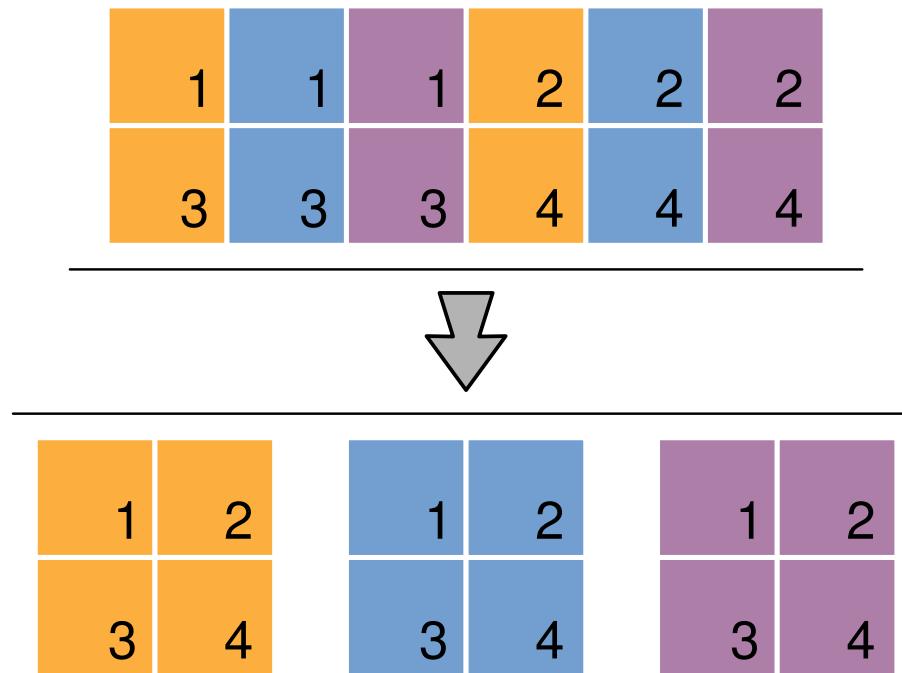

Las mejoras se enfocaron en la sección de código más computacionalmente intensiva: el cálculo de la energía de intercambio y correlación. En GPU se buscó cambiar la estrategia de paralelización en la estructura del cómputo y aprovechar la mayor cantidad de memoria de las placas para almacenar más resultados intermedios. La implementación en CPU y Xeon Phi es compartida, aprovechando las prestaciones del compilador para explotar vectorización y paralelismo de manera portable. Se estudió el uso de algoritmos de partición de trabajo y balance de cargas para mantener una división equilibrada de trabajo entre unidades de cómputo, notando el impacto de estas decisiones en la escalabilidad de la implementación.

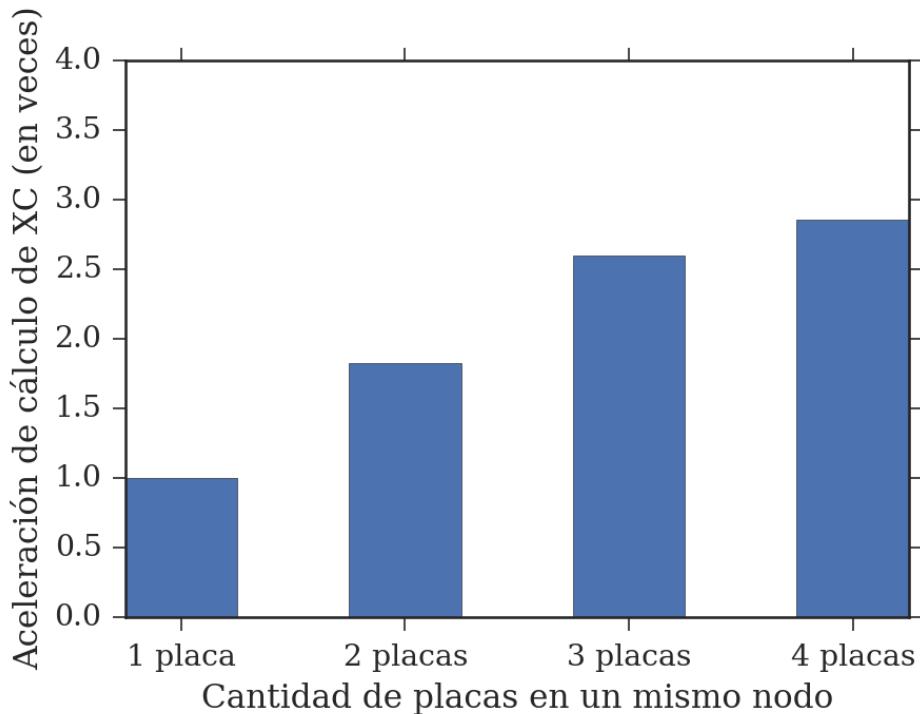

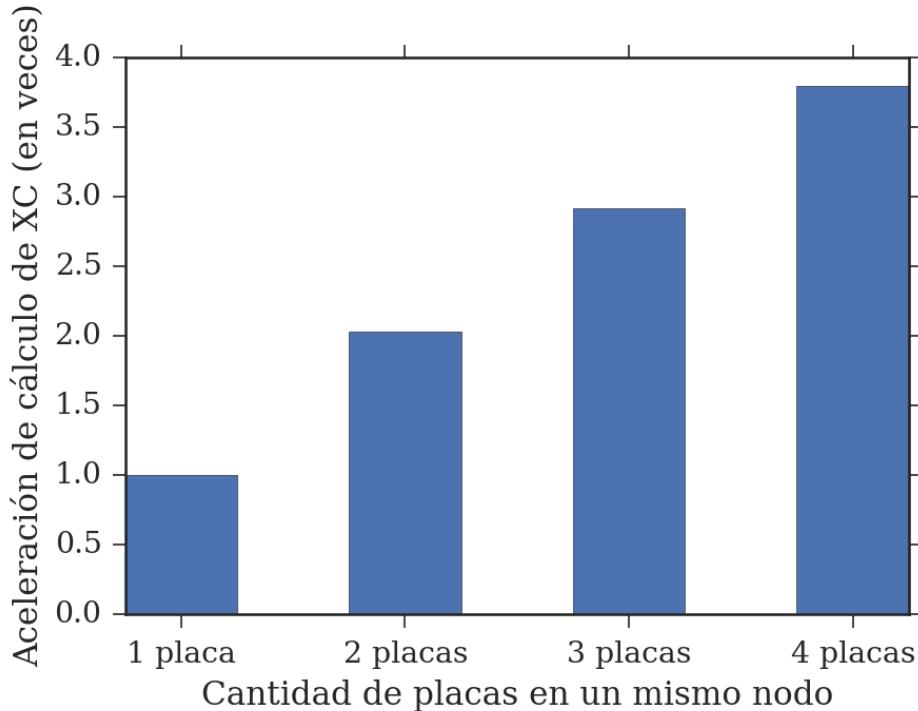

Las mejoras logradas en el rendimiento de la implementación son de 8 veces por sobre la original en GPU, y de 22 veces en el caso de CPU, para los casos de prueba y configuraciones de *hardware* usados. Los resultados en Xeon Phi resultan comparativamente inferiores a los obtenidos con las otras arquitecturas pero se lograron identificar puntos claves del coprocesador que permitirán continuar con la tarea de optimización. En GPU se implementó y estudio, además, el uso de múltiples placas de video en una misma plataforma, escalando linealmente en función de la cantidad de los dispositivos usados para algunos casos.

Adicionalmente, se observó que las implementaciones en CPU y GPU tienen un rendimiento complementario con respecto a las tareas necesarias para el cálculo de la energía de intercambio y correlación. Esto lleva a pensar que puede lograrse mejoras muy significativas con una implementación híbrida CPU-GPU, usando el *hardware* ya disponible.

Por último, se realizó una comparativa de las arquitecturas estudiadas desde un punto de vista pragmático en el diseño de *clusters* de cómputo. Se espera que las técnicas expuestas en este trabajo sirvan como guía para optimizar aplicaciones de índole similar mediante el uso de estas arquitecturas, y para decidir de manera informada entre las mismas según la clase de problema a resolver.

**Palabras claves:** QM/MM, DFT, Xeon Phi, CUDA, HPC, *scheduling*.

## ABSTRACT

The present work is focused on accelerating electronic structure calculations using massively parallel processor architectures. As a starting point, an existent implementation of the algorithms derived from the Density Functional Theory (DFT), LIO, was studied. LIO employs General Purpose Graphics Processing Unit (GPGPU) for several computations. This software was adapted to use specific features offered by multiprocessors, modern GPUs and the numerical coprocessor Intel Xeon Phi.

The optimization efforts were put on the most time-consuming sections, the exchange-correlation calculations. In GPU the goal was to improve parallelism in the structure of the code and store more temporary results, previously discarded due to insufficient device memory. The CPU and Xeon Phi implementation is shared, exploiting vectorization and parallelization techniques portably, present in modern compilers. The use of work splitting and load balancing algorithms is also studied, in order to keep a balanced work partition between compute units. The impact of different approaches regarding the scalability of the implementation is observed.

The improvements obtained in the performance of the application are up to 8 times over the original in GPU, and over 22 times in the case of the CPU in the hardware employed. The results in Xeon Phi are comparatively inferior to other architectures although key points in the coprocessor architecture were identified to encourage further optimizations. An implementation to employ multiple GPUs in a single system was developed, obtaining linear speedups in some of the studied configurations.

Furthermore, it was noted that CPU and GPU have complementary performance regarding the necessary steps needed to perform the exchange-correlation calculation. This points towards potentially significant improvements regarding a hybrid CPU-GPU implementation, using already available resources.

Finally, a comparison was made between the architectures from the pragmatic point of view of building a compute cluster. Hopefully, the techniques presented in this work can lead to the optimization of similar applications in the usage of these architectures, and help make an educated decision between them according to the problem at hand.

**Keywords:** QM/MM, DFT, Xeon Phi, CUDA, *scheduling*.

## AGRADECIMIENTOS

A Nano y Esteban, por su dedicación a este trabajo, su guía, su paciencia y la buena onda en momentos de crisis o de pánico.

A Manuel, por todos los proyectos que hicimos, los éxitos que tuvimos, los fracasos que enseñaron y por los desastres que haremos en el futuro.

A mi mamá Cecilia y a mi hermano Ignacio, por estar ahí para mí por más que vaya, vuelva, cambie, discuta, pelee, cuelgue o me haya desconcentrado.

A mi papá, Adrián, por creer en mi desde chico e impulsarme a dar lo mejor.

A todos los compañeros y amigos del LSC: A David por sus dibujos y sus locuras, a Maxi por sus consejos y por prenderse al nihilismo académico, a Ema, Nacho y Nahuel por no dejarse desconcentrar por mis cualquiereadas, a Ceci por bancarlas tan estoicamente, y a Seba Galimba por ser la figura cuando lo veíamos venir a la oficina.

Al DC, porque con sus gentes y sus pasillos supo ser el lugar donde crecí como programador, como científico y como persona.

A mis amigos de GGA y GARG: Pato, Tebex, Darío, Doc, Juli, Tavo, Marco y Nico, por los tres meses que (¿sobre?) vivimos juntos, las anecdotas, y por las descarriladas que vendrán.

A mis amigos de la facu: Diego, Pablo A., Juli S., Rodra, Luigi, Guille, Marto, Mati B., Lucho, Javo, Nacho, Ivan B., Peter, Marian, Fede L., Ivan S., Agus G., Rober, Leandro L., Lis, Juan H. y a todos y todas los que estuvieron ahí por mí en estos años de educación universitaria.

A mis amigos Brian, Lebe, Nico Bolo y Fede Brumfman, que me conocieron cuando era una persona totalmente distinta y que compartieron ya una vida conmigo.

A Esteban, por permitirnos interrumpirlo una ilimitada cantidad de veces en cada paso de este trabajo y por conseguir todos los recursos para poder hacer investigación de punta.

A Nano, por el valioso tiempo brindado y las reiteradas explicaciones de química hasta que la pudimos entender.

A Juan Pablo, por el trabajo conjunto a lo largo de estos años, culminando con un gran esfuerzo satisfactorio.

A Ana y Alfonso, mis padres, por el apoyo emocional, intelectual, económico y moral a lo largo de la carrera. Imposible hubiera sido sin ustedes.

A Mariana, mi hermana, por haber sido un oído de todas las cosas que se me han ocurrido durante la carrera, aunque no hubiese entendido ni medio.

A Gonzalo y Maximilian, por haber convertido la etapa más estresante en la más divertida de mi vida.

A David y Maxi, por la amistad y la enorme cantidad de ideas aportadas directa e indirectamente a este trabajo.

Al DC, por haberme brindado una educación de primera categoría y permitirme colaborar mínimamente con ella haciendo mi parte como ayudante de la mejor materia de la carrera.

A mis amigos, Guillermo, Daniela, Matías, Luciano, Javier, Nacho, Luis, Guille, Fernando, Leandro, Federico L., Marco, Andrés, Nicolás, Federico T., Laura, Wanda, y a todo los que no nombré mas por desmemoriado que por desagradecido.

A SIASA, Intel y Nvidia por los recursos computacionales brindados, imprescindibles para poder hacer un estudio serio usando tecnologia de punta.

## Índice general

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 1.. Introducción . . . . .                                                | 1  |

| 1.1. Modelos Cuánticos (QM) . . . . .                                     | 1  |

| 1.2. Cómputo de alto rendimiento . . . . .                                | 4  |

| 2.. Arquitecturas en profundidad . . . . .                                | 7  |

| 2.1. CPU . . . . .                                                        | 7  |

| 2.1.1. Tipos de paralelismo . . . . .                                     | 7  |

| 2.1.2. Pipeline y Ejecución fuera de orden . . . . .                      | 8  |

| 2.1.3. Extensiones vectoriales . . . . .                                  | 9  |

| 2.1.4. Caches . . . . .                                                   | 9  |

| 2.1.5. Multiprocesadores . . . . .                                        | 10 |

| 2.2. CUDA . . . . .                                                       | 12 |

| 2.2.1. Introducción . . . . .                                             | 12 |

| 2.2.2. Organización de procesadores . . . . .                             | 14 |

| 2.2.3. Organización de la memoria . . . . .                               | 17 |

| 2.2.4. Esquema de paralelismo . . . . .                                   | 19 |

| 2.2.5. Diferencias entre Tesla, Fermi, Kepler . . . . .                   | 20 |

| 2.2.6. CUDA, Herramientas de desarrollo, profiling, exploración . . . . . | 21 |

| 2.2.7. Requerimientos de un problema para GPGPU . . . . .                 | 22 |

| 2.2.8. Diferencia entre CPU y GPU - Procesadores especulativos . . . . .  | 23 |

| 2.2.9. Idoneidad para la tarea . . . . .                                  | 24 |

| 2.3. Xeon Phi . . . . .                                                   | 24 |

| 2.3.1. Introducción . . . . .                                             | 24 |

| 2.3.2. Microarquitectura general . . . . .                                | 25 |

| 2.3.3. Pipeline . . . . .                                                 | 25 |

| 2.3.4. Estructura de cache . . . . .                                      | 26 |

| 2.3.5. Arquitectura del set de instrucciones . . . . .                    | 27 |

| 2.3.6. Organización de la memoria . . . . .                               | 28 |

| 2.3.7. Conexión Host - Coprocesador . . . . .                             | 28 |

| 2.3.8. Modos de ejecución . . . . .                                       | 29 |

| 2.3.9. Herramientas de desarrollo y profiling . . . . .                   | 29 |

| 2.3.10. Idoneidad para la tarea . . . . .                                 | 30 |

| 3.. Implementación . . . . .                                              | 31 |

| 3.1. Implementación existente . . . . .                                   | 31 |

| 3.2. Implementación en CUDA . . . . .                                     | 33 |

| 3.2.1. Limitantes de performance . . . . .                                | 34 |

| 3.2.2. Subutilización de los SM . . . . .                                 | 34 |

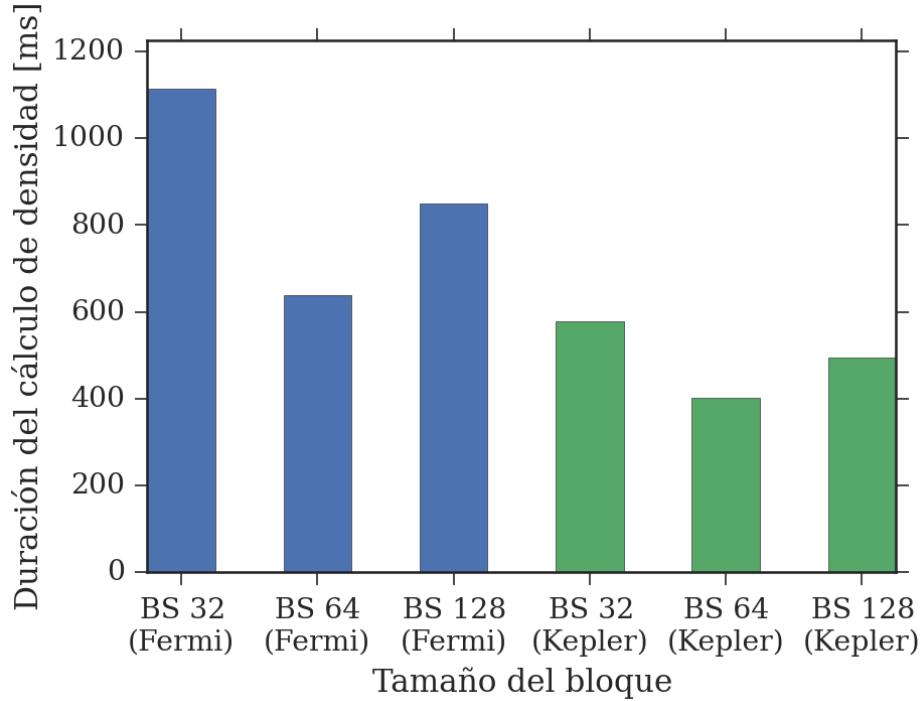

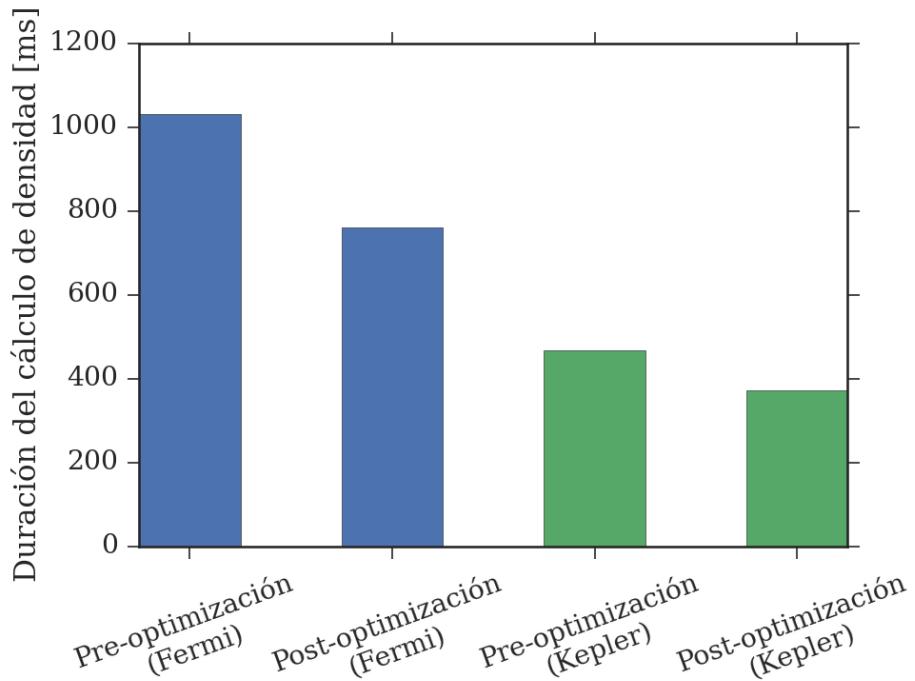

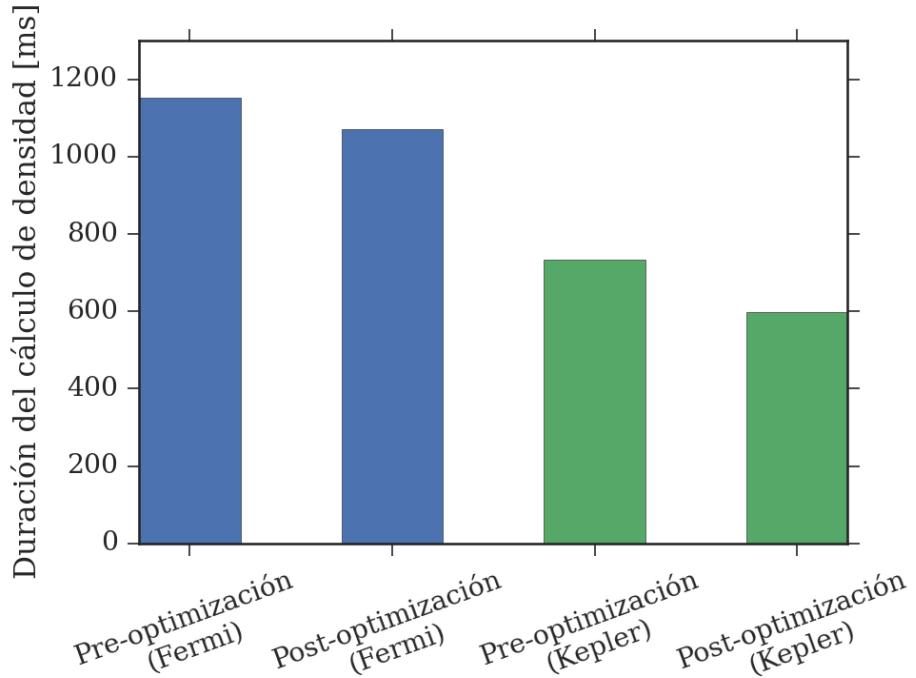

| 3.2.3. Cambios en el threading . . . . .                                  | 35 |

| 3.2.4. Cambios en la reducción de los bloques . . . . .                   | 38 |

| 3.2.5. Cambios en los accesos globales . . . . .                          | 39 |

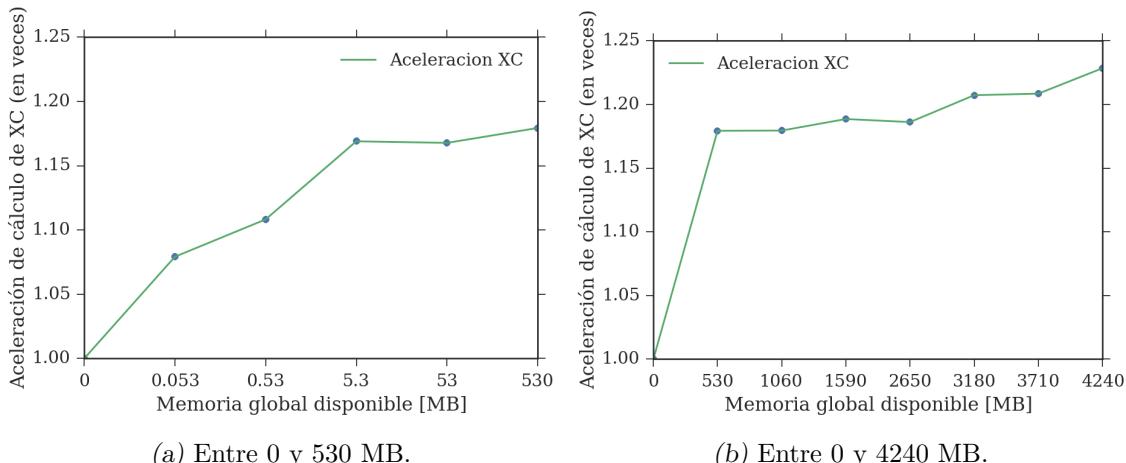

| 3.2.6. Cambios en el almacenamiento de matrices temporales . . . . .      | 41 |

| 3.2.7. Cambios en las memorias compartidas . . . . .                      | 43 |

|                                                            |     |

|------------------------------------------------------------|-----|

| 3.2.8. Escalando más allá de un GPU . . . . .              | 44  |

| 3.3. Implementación en CPU . . . . .                       | 52  |

| 3.3.1. Caso de estudio . . . . .                           | 53  |

| 3.3.2. Estructura original del código . . . . .            | 53  |

| 3.3.3. Cambios en la vectorización . . . . .               | 55  |

| 3.3.4. Almacenamiento de las matrices . . . . .            | 58  |

| 3.3.5. Prototipos de paralelización . . . . .              | 58  |

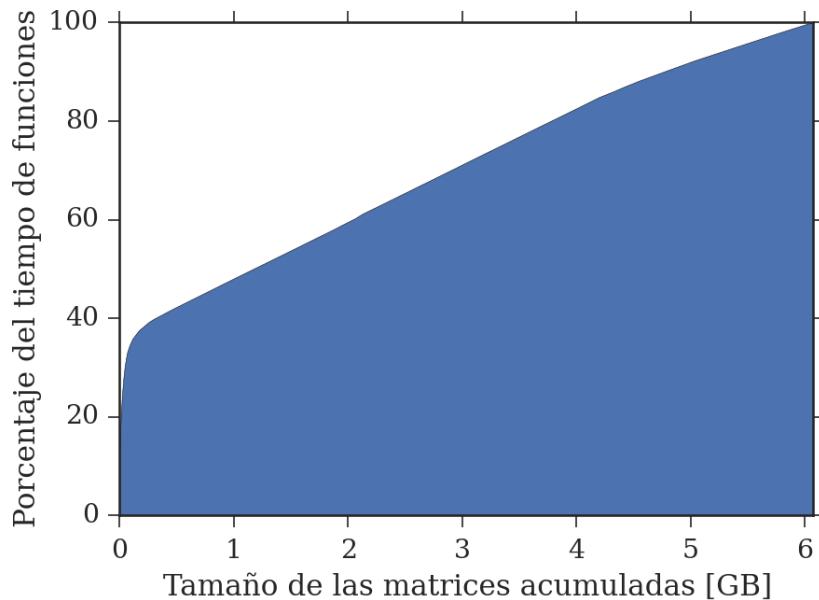

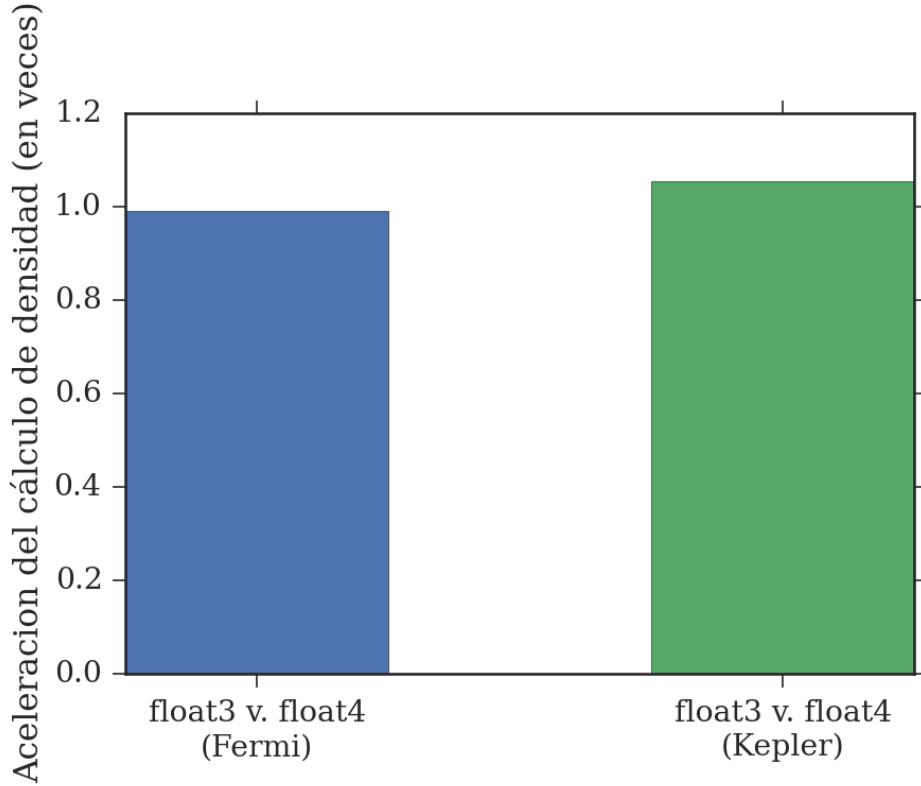

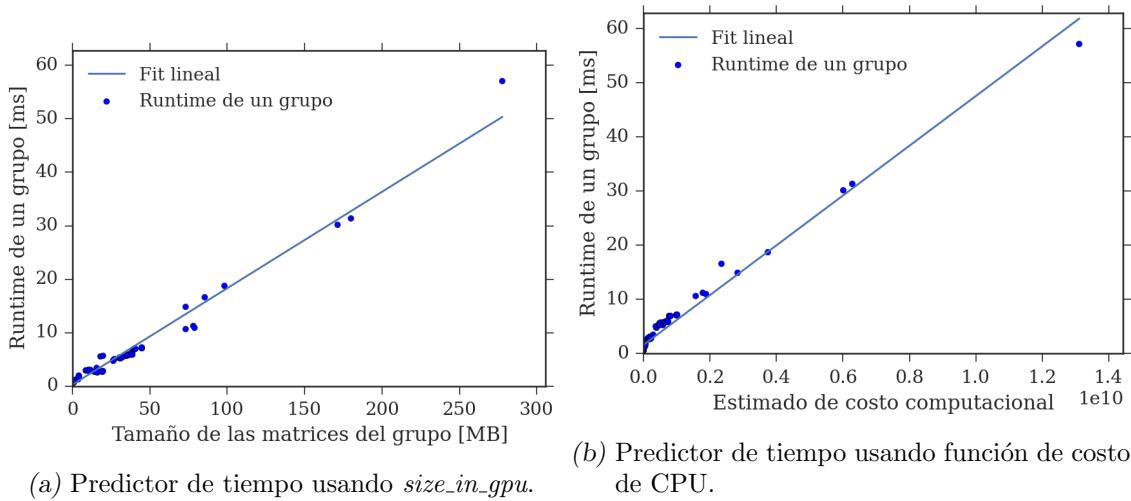

| 3.3.6. Análisis de costo computacional de grupos . . . . . | 60  |

| 3.3.7. Algoritmo de particionado . . . . .                 | 61  |

| 3.3.8. Cambios en paralelismo . . . . .                    | 63  |

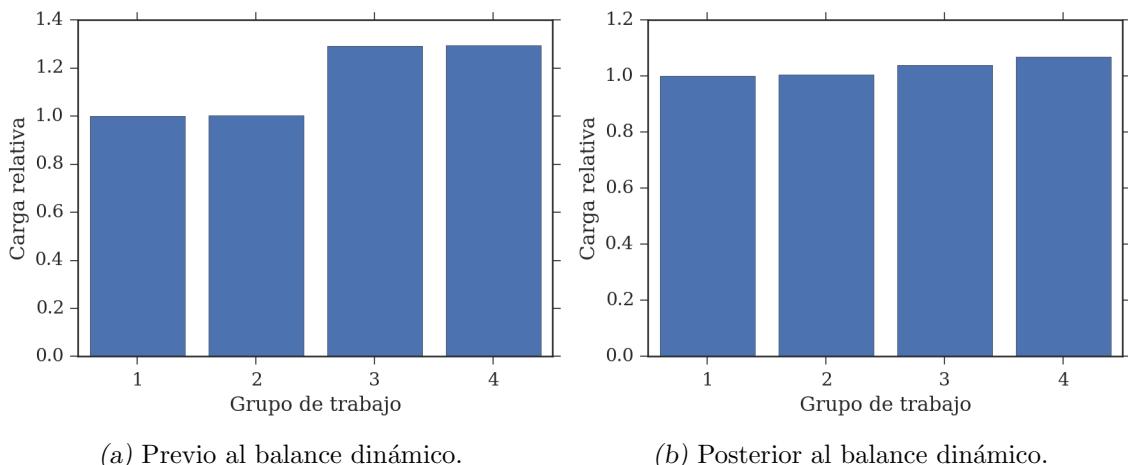

| 3.3.9. Algoritmo de segregación . . . . .                  | 69  |

| 3.3.10. Algoritmo de balanceo . . . . .                    | 69  |

| 3.3.11. Paralelización a funciones y pesos . . . . .       | 70  |

| 3.4. Implementación en Xeon Phi . . . . .                  | 73  |

| 3.4.1. Resultados preliminares . . . . .                   | 73  |

| 4.. Resultados . . . . .                                   | 81  |

| 4.1. Resultados en CPU . . . . .                           | 81  |

| 4.2. Resultados en GPU . . . . .                           | 84  |

| 4.3. Resultados en Xeon Phi . . . . .                      | 84  |

| 4.4. Comparación entre arquitecturas . . . . .             | 85  |

| 4.5. Tamaño de los grupos . . . . .                        | 87  |

| 4.6. ¿Qué me conviene comprar? . . . . .                   | 88  |

| 5.. Conclusiones . . . . .                                 | 91  |

| 5.1. Trabajo a futuro . . . . .                            | 92  |

| Apéndice . . . . .                                         | 99  |

| A.. Equipamiento usado para correr las pruebas . . . . .   | 101 |

| B.. Descripción de modelos químicos probados . . . . .     | 103 |

# 1. INTRODUCCIÓN

Con la aparición de las computadoras, han ganado espacio dentro de las ciencias naturales los métodos de simulación. El uso de estas técnicas permite validar modelos teóricos así como también brindar información detallada (macro y microscópica) del proceso simulado.

En el ámbito de la química existen diferentes modelos que permiten simular procesos de interés. Dentro de estos modelos hay dos que se destacan por su uso:

- Los métodos basados en la mecánica cuántica, que proporcionan una descripción de la estructura electrónica del sistema.

- Los métodos basados en la mecánica molecular, donde las moléculas son tratadas mediante un campo de fuerza clásico y los electrones no son tenidos en cuenta explícitamente.

## 1.1. Modelos Cuánticos (QM)

El comportamiento de los fenómenos a pequeña escala (nanométrica) está regido por las leyes de la mecánica cuántica. Este marco teórico desarrollado a comienzos del siglo XX propone que las partículas (como electrones y protones) pueden (y deben en algunos casos) ser descriptas como ondas. Así, cualquier propiedad de un sistema está determinado por una función llamada *función de onda* ( $\Psi$ ) que satisface la ecuación de Schrödinger dependiente del tiempo:

$$i\hbar \frac{\partial \Psi}{\partial t}(\mathbf{r}, t) = \frac{-\hbar^2}{2m} \nabla^2 \Psi(\mathbf{r}, t) + V(\mathbf{r}, t) \Psi(\mathbf{r}, t) \quad (1.1)$$

donde  $\mathbf{r} = (r_1, \dots, r_n)$  es el vector de todas las posiciones de las partículas del sistema,  $m$  es la masa de la partícula,  $V$  es un potencial que afecta a las partículas y  $\hbar$  es la constante de Planck dividida por  $2\pi$ .

Si el campo externo no depende del tiempo esta ecuación se puede simplificar a la de Schrödinger *independiente del tiempo*:

$$\hat{H}\Psi(\mathbf{r}) = E\Psi(\mathbf{r}) \quad (1.2)$$

donde  $E$  es la energía asociada a la función de onda  $\Psi$  y el operador hamiltoniano  $\hat{H}$  se define como

$$\hat{H} = -\frac{\hbar^2}{m} \nabla^2 + \hat{V}$$

Ahora, si bien resolver esta ecuación diferencial sería suficiente para determinar todas las propiedades del sistema, esto no puede hacerse de manera exacta cuando hay más de un electrón en el mismo. Por este motivo, para problemas de mayor tamaño se utilizan aproximaciones para obtener una solución de la ecuación 1.2.

Existen diversos métodos para resolver de forma aproximada esta ecuación con diferente costo computacional y calidad de la respuesta obtenida. Dentro de estos métodos hay

uno que destaca por su excelente relación costo/calidad, el método basado en la Teoría de los Funcionales de la Densidad (DFT, Density Functional Theory) desarrollada por Hohenberg y Kohn en 1964.

En este marco teórico, la *densidad electrónica*  $\rho$  que representa la probabilidad de encontrar un electrón en cada región del espacio ocupa un rol destacado. La base de este método consiste en dos teoremas publicados por Hohenberg y Kohn [1]. Estos autores demuestran que  $\rho$  y  $V$  (y por lo tanto  $\psi$ ) se encuentran relacionadas biunívocamente, es decir, que una dada densidad electrónica contiene la misma información que la función de onda. De esta manera, cualquier observable (como la energía) puede ser representado como un funcional de la densidad (de allí el nombre de esta teoría).

Además propusieron la dependencia de la energía del sistema como funcional de la densidad de la siguiente forma:

$$E[\rho] = T_s[\rho] + V_{ne}[\rho] + \frac{1}{2} \int \int \frac{\rho(\vec{r}_1)\rho(\vec{r}_2)}{r_{12}} d\vec{r}_1 d\vec{r}_2 + E_{XC}[\rho] \quad (1.3)$$

Donde  $T_s[\rho]$  es la energía cinética asociada con la densidad,  $V_{ne}[\rho]$  es la energía potencial producto de la interacción entre los electrones (la densidad) y los núcleos, el tercer término es el resultado de la repulsión de Coulomb entre electrones y  $E_{XC}[\rho]$  es la energía de intercambio y correlación. Este último término da cuenta de la energía asociada a escribir la función de onda de manera que cumpla con el principio de exclusión de Pauli y de la correlación en la posición instantánea de los electrones.

Esta formulación es exacta si se conociera el término  $E_{XC}[\rho]$  dado que los demás tienen solución analítica. En las aproximaciones hechas para calcularlo reside tanto la calidad como el costo computacional de este tipo de simulaciones. Por ello, el objetivo central de este trabajo consiste en disminuir el tiempo insumido en el cálculo de el término  $E_{XC}[\rho]$ .

La forma comúnmente utilizada para calcular este término se basa en definir un funcional local  $\epsilon_{XC}$  que depende de la densidad (*Local Density Aproximation*, LDA) o de la densidad y su gradiente (*General Gradient Approximation*, GGA) en cada punto del espacio.

De esta manera se puede calcular  $E_{XC}$  mediante la integral:

$$E_{XC} = \int \rho(r) \epsilon_{XC}(\rho(r)) dr \quad (1.4)$$

Esta ecuación puede ser aproximada mediante una suma utilizando una grilla de  $j$  puntos, con pesos  $\omega_j$  según:

$$E_{XC} \approx \sum_j \omega_j \rho(r_j) \epsilon_{XC}(\rho(r_j)) \quad (1.5)$$

Otro aspecto importante de esta teoría es que provee una manera de calcular la densidad  $\rho$ , mediante el denominado método de Kohn-Sham [2]. Este método se basa en el segundo teorema de Hohenberg y Kohn, que establece que para cualquier densidad electrónica de prueba  $\rho^*$  que cumpla que  $\int \rho^*(\vec{r}) d\vec{r} = N$ , donde  $N$  es la cantidad de electrones del sistema, vale que:

$$E[\rho^*] \geq E[\rho] \quad (1.6)$$

Esto produce un método auto-consistente para calcular  $\rho$ . Se empieza con una aproximación inicial  $\rho^*$  y se itera el cálculo de la misma hasta alcanzar un mínimo para  $E$ .

Este marco teórico es uno de los métodos más populares en problemas de estado sólido, especialmente desde la década del 90 cuando se mejoraron las aproximaciones para modelado de interacciones. El valor de esta teoría para el estudio de las propiedades de la materia le valió a Kohn el Premio Nobel de Química en 1998.

Si bien la relación costo-calidad de este método es muy buena, el costo computacional asociado sigue siendo elevado, lo que limita su aplicación a sistemas pequeños (cientos de átomos como máximo).

Por este motivo, se han desarrollado los métodos conocidos como *mecánica molecular* (MM). En estos métodos los átomos son tratados como esferas cargadas y las uniones químicas como resortes (potenciales armónicos). De esta manera, los electrones no son considerados explícitamente, reduciendo drásticamente el costo computacional asociado. Esta técnica es muy poderosa para representar sistemas o procesos en los que no cambia la distribución electrónica.

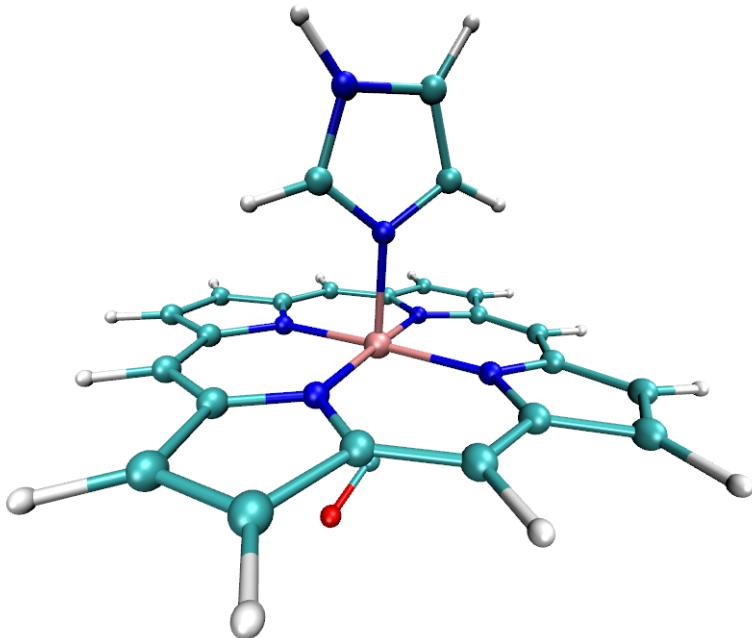

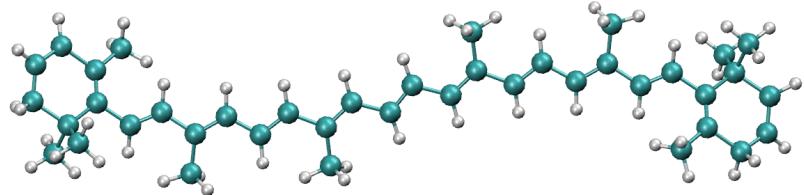

Sin embargo, en muchos de los problemas de interés en química y bioquímica (por ejemplo una reacción química en solución o en el sitio activo de una proteína), el modelado requiere simultáneamente de la representación de miles de átomos y de un tratamiento explícito de los electrones. Para resolver esto, se han desarrollado técnicas híbridas QM/MM (*Quantum Mechanical / Molecular Mechanics*).

Dentro de este esquema se subdivide el sistema en dos partes:

- i) Una parte en la que la estructura electrónica cambia. Se lo modela usando mecánica cuántica (QM).

- ii) Para el resto del sistema se aplica un campo de fuerzas clásico (MM).

De esta manera se puede expresar la energía del sistema QM/MM cómo:

$$E = E_{QM} + E_{QM/MM} + E_{MM} \quad (1.7)$$

donde la energía  $E_{QM}$  se obtiene mediante el método DFT visto más arriba, la energía  $E_{MM}$  proviene de simular el campo de fuerzas clásico y  $E_{QM/MM}$  surge de la interacción entre las regiones  $QM$  y la regiones  $MM$  del modelo.

Esta última se calcula, en este trabajo, mediante la ecuación:

$$E_{QM/MM} = \sum_{l=1}^{N_c} q_l \int \frac{\rho(r)}{|r - R_l|} + \sum_{l=1}^{N_c} \sum_{\alpha=1}^{N_q} [v_{LJ}(|R_l - \tau_\alpha|) + \frac{q_l z_\alpha}{|R_l - \tau_\alpha|}] \quad (1.8)$$

donde el primer término da cuenta de la interacción entre una carga puntual del sistema clásico con la densidad electrónica, y el segundo término representa la interacción entre los núcleos clásicos con los cuánticos mediante un potencial de Lennard-Jones y la interacción Coulombica entre las cargas.

Los métodos *QM/MM*, dentro del marco de métodos multiescala, son ampliamente utilizados en la práctica. Estos modelos han valido a Karplus, Levitt y Warshel el premio Nobel de Química en 2013, por su valor para la simulación de sistemas complejos.

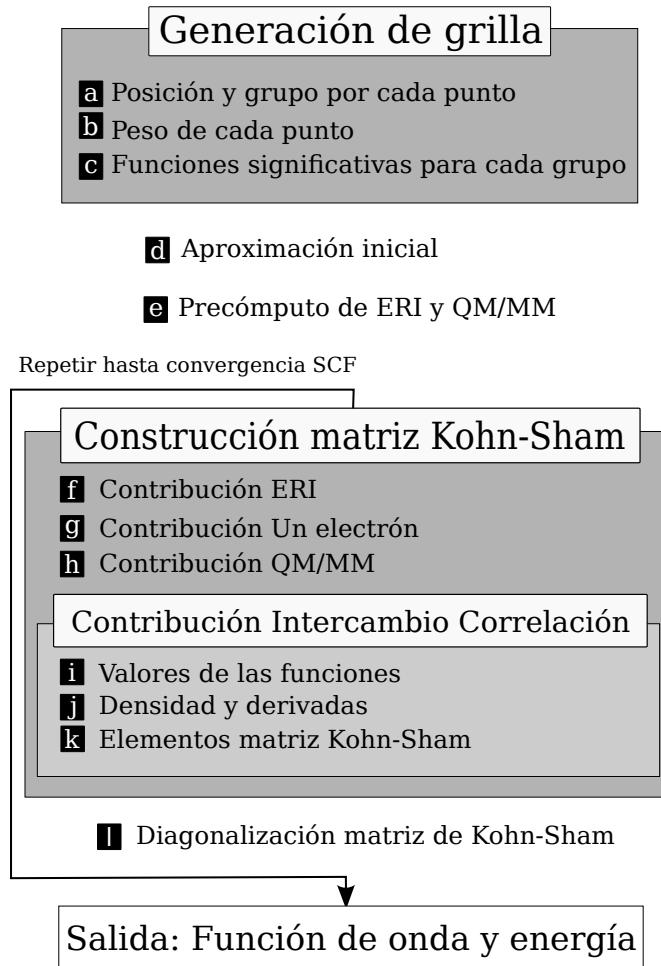

Nuestro trabajo se realiza en base a programas ya existentes. El cálculo de  $E_{QM}$  y  $E_{QM/MM}$  son realizados por la aplicación LIO [3, 4], el cual fue optimizado en este trabajo para el uso de distintas arquitecturas de CPU y GPU. Este paquete se complementa mediante el uso del programa de dinámica molecular Amber [5], que realiza el cálculo de  $E_{MM}$ . Nos concentraremos en las partes computacionalmente más intensivas de LIO,

que corresponden a la implementación de los cálculos de los términos de intercambio y correlación ya introducidos en esta sección.

El diseño de estos algoritmos depende del sistema a tratar. Las simulaciones híbridas requieren la resolución de la estructura electrónica en cada paso de dinámica. Esto restringe el tamaño del problema a resolver a decenas o a lo sumo cientos de átomos. Por estos motivos, el presente trabajo se concentra en la optimización de los algoritmos aplicados a estos sistemas.

## 1.2. Cómputo de alto rendimiento

Una parte significativa del impacto de las computadoras en los distintos aspectos de las ciencias, incluso de la vida diaria, se debe al crecimiento de su poder de cómputo desde la aparición de los primeros microprocesadores hasta los disponibles hoy en día.

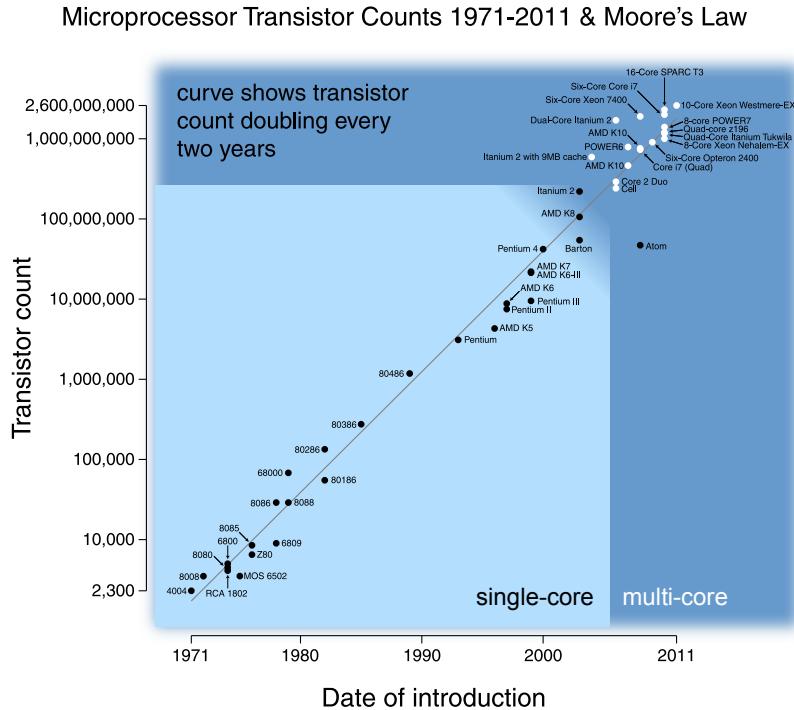

Entre 1986 y 2002, la *performance* de los procesadores creció, en promedio, un 50 % por año [6]. La denominada *Ley de Moore* establece que la densidad de transistores por circuito integrado se duplica cada 18 meses [7]. Esto puede verse en la figura 1.1, que compara la cantidad de transistores de distintos procesadores desde 1971 a la actualidad.

Este crecimiento permitió a los desarrolladores de procesadores incrementar la potencia de cálculo, duplicando la eficiencia cada 24 meses. Esto benefició durante mucho tiempo a los desarrolladores de aplicaciones, quienes escribían programas secuenciales, que solo debían esperar a la aparición de los nuevos modelos de procesadores para ver una reducción sustancial en los tiempos de ejecución de sus aplicaciones.

Fig. 1.1: Cantidad de transistores en procesadores emblemáticos desde 1971

Sin embargo, a medida que los transistores disminuyen su tamaño, aumentan su disipación térmica por unidad de superficie. Esto limita la cantidad que se pueden ubicar en

un circuito sin producir que este se comporte de manera errática. El mismo motivo impide continuar el crecimiento de la frecuencia del reloj.

Los problemas térmicos han implicado que desde el 2002, la tasa de crecimiento de la *performance* de los monoprocesadores haya disminuido a un 20 % anual. Consecuentemente, los principales fabricantes de procesadores han modificado el enfoque de investigación y diseño, empezando a hacerse más y más común el uso de múltiples procesadores por chip.

La preocupación por la disipación y el consumo energético insustentables han sido motivadores de diseños con menor frecuencia de reloj, pero aprovechando las aún crecientes densidades de transistores para incrementar las unidades de soporte. Esta estrategia ha resultado en que, en un CPU moderno, menos del 20 % de todos los transistores disponibles se utilicen para realizar cálculos.

Adicionalmente, las mejoras de *performance* debidas al paralelismo a nivel de instrucción mediante técnicas como ejecución fuera de orden, ejecución especulativa, *pipelining*, etc., han sido progresivamente menores. Actualmente, los esfuerzos invertidos en ese área se han concentrado en el paralelismo a nivel de datos (vectorización) y paralelismo a nivel de tareas (multiprocesadores) [7].

Este enfoque en diseño de arquitecturas hacia otros tipos de paralelismo puede verse tanto en nuevos productos en las líneas establecidas (por ejemplo los procesadores Intel i3, i5 e i7) así como también en nuevos desarrollos que apuntan a cómputo de alta *performance*. La revalorización de las placas gráficas (GPUs) para problemas de cómputo intensivo, y los desarrollos nuevos como la arquitectura MIC (*Many Integrated Core Architecture*) de Intel son claros ejemplos de esta tendencia.

El impacto de este enfoque hacia múltiples hilos de ejecución en paralelo en el desarrollo de aplicaciones es significativo. En simulaciones para las áreas de biología, medicina, química o meteorología es de gran interés minimizar los tiempos de ejecución, para permitir realizar predicciones de mayor calidad usando modelos más sofisticados. Aprovechar las nuevas arquitecturas multiprocesador requiere modificaciones en el código que resultan no triviales, a diferencia del crecimiento en la velocidad de reloj que no requería modificaciones en el diseño del programa. Los intentos de escribir programas que conviertan programas seriales (diseñados para un solo procesador) a paralelos, en lenguajes de propósito general como C, C++ o Fortran, han sido relativamente infructuosos [6].

Existen, sin embargo, herramientas que realizan transformaciones de código fuente serial a código fuente con anotaciones de parallelización automáticas (usando bibliotecas de parallelización asistida como OpenMP para las anotaciones). Ejemplos de estas herramientas incluyen Par4All [8] y Cetus [9]. Estas herramientas pretenden, además, generar código para aceleradores especiales como GPUs.

Como consecuencia, resulta necesario el trabajo a nivel de desarrollo de código para utilizar múltiples procesadores. La aparición de nuevas herramientas ayudan al programador en la tarea del uso eficiente de los recursos computacionales existentes. Un ejemplo de esto es Nvidia CUDA (*Compute Unified Device Architecture*), que provee una arquitectura y lenguaje de programación para el desarrollo de aplicaciones que exploten los recursos provistos por tarjetas gráficas, constituyendo la metodología conocida como GPGPU (*General Purpose Graphical Processing Units*). Otros ejemplos se pueden ver en APIs y bibliotecas unificadas de desarrollo como OpenMP o MPI (*Message Passing Interface*), trabajando conjuntamente con compiladores optimizantes como Intel ICC y PGI Fortran.

Estas herramientas, si bien resultan una ayuda muy importante para el programador,

no constituyen una panacea. Todavía la división del trabajo es inherente al problema a resolver en base a las dependencias de las tareas involucradas. Realizar esta división es una labor que, hasta el día de hoy, es responsabilidad del programador especializado.

En este trabajo, se busca comparar distintas arquitecturas de hardware y cómo las características específicas de la simulación química a realizar permiten o impiden la paralelización de trabajo empleando los distintos recursos específicos que cada arquitectura provee.

## 2. ARQUITECTURAS EN PROFUNDIDAD

### 2.1. CPU

Los microprocesadores ganan en prevalencia desde principios de los años 70, cuando Intel introduce los modelos 4004 y 8008. Actualmente, las arquitecturas de procesadores de 64 bits basadas en la línea x86-64 de Intel dominan no solo el mercado de computadoras personales sino que también el de servidores y *clusters* de cómputo. Dado que utilizaremos el CPU estándar como punto de comparación para las demás arquitecturas, y que éstas están basadas en parte en su diseño, daremos una breve reseña de los aspectos más importantes y desarrollos modernos con respecto a la *performance* dentro de los procesadores actuales. Haremos foco en el concepto de *paralelismo* en las arquitecturas: la posibilidad de ejecutar simultáneamente flujos de instrucciones independientes entre sí.

#### 2.1.1. Tipos de paralelismo

Existen tres categorías de paralelismo que, hoy en día, una arquitectura puede aprovechar para mejorar la *performance* de una aplicación:

- *Instruction Level Parallelism*: Este tipo de optimizaciones buscan ejecutar la mayor cantidad de instrucciones en un mismo hilo de ejecución simultáneamente. Optimizaciones de este estilo incluyen:

- *pipelines* de procesador: se separan las instrucciones en distintas etapas para ejecutar múltiples instrucciones de manera solapada. Cada etapa es un estadio dentro de una cadena de montaje que empieza decodificando una instrucción y la ejecuta de a partes.

- ejecución superescalar fuera de orden: ejecutar al mismo tiempo instrucciones que no usan recursos comunes y son independientes entre sí.

- ejecución especulativa: se basa en la predicción de resultados todavía no finalizados de procesar.

- *Data Level Parallelism*: Consideran las optimizaciones cuyo propósito es lograr aplicar una misma operación a cada elemento de un conjunto datos simultáneamente en un mismo hilo de ejecución. Esta técnica se denomina SIMD (*Single Instruction, Multiple Data*).

- *Thread Level Parallelism*: Concerne al uso de múltiples hilos de ejecución simultáneos, lo cual requiere el uso de procesadores que usualmente comparten la memoria principal (arquitectura SMP, *Symmetric Multiprocessing*). Esto normalmente requiere esfuerzo adicional por parte del programador para mantener consistencia y coherencia.

En base a estos tipos de paralelismo surgieron grandes avances en la arquitectura de procesadores desde 1950 en adelante. Estos se detallan cronológicamente en la tabla 2.1, como también la motivación de su existencia.

A continuación detallamos algunos aspectos de cada una de estas técnicas.

| Año   | Tecnología           | Motivo                                                                                                                    |

|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1950s | Pipelines            | Usar independientemente las distintas unidades del procesador para disminuir los ciclos por instrucción.                  |

| 1970s | Vectorización        | Poder realizar las mismas operaciones sobre muchos datos simultáneamente.                                                 |

| 1980s | Cache                | Disminuir la latencia de muchos accesos a la memoria aprovechando la localidad de los mismos.                             |

| 1987  | Múltiples ALUs       | Poder compensar las ALU que más latencia tienen, se multiplican las unidades para procesar más instrucciones en paralelo. |

| 1988  | Predicción de Saltos | Disminuir y hasta evitar los costos de tener que recalcular el pipeline cuando hay saltos.                                |

| 1995  | Fuera de Orden       | Solapar la ejecución de instrucciones para compensar por instrucciones lentas y accesos a memoria.                        |

| 2002  | SMT                  | Poder procesar de a más de un <i>thread</i> de OS en un solo core.                                                        |

| 2005  | Multi-core           | Aumentar el poder de cómputo sin aumentar la velocidad de clock.                                                          |

Tab. 2.1: Cronología de los avances de arquitectura de procesadores, tomado de [7]

### 2.1.2. Pipeline y Ejecución fuera de orden

Los primeras implementaciones de paralelismo a nivel de un solo procesador fueron a nivel de instrucciones mediante el uso de *pipelines* de múltiples etapas. Por ejemplo, en la arquitectura del Intel Pentium 4 se llegaron a utilizar 20 etapas distintas de pipeline. Cada etapa corresponde a una actividad distinta en el proceso de ejecutar una instrucción. Al tiempo que una instrucción es decodificada, por ejemplo, otra instrucción puede estar siendo leída de memoria ya que, idealmente, las etapas previas no dependen de las posteriores. Este mecanismo funciona bien siempre y cuando una instrucción no dependa de los resultados de otra anterior. Sin embargo, ocurre habitualmente que existe una dependencia entre instrucciones, produciéndose entonces una demora (o *pipe stall*) que requiera ejecutar las instrucciones de manera no solapada (con el costo de *throughput* de instrucciones que ello implica).

Esta técnica llevada a su conclusión lógica se conoce como ejecución fuera de orden (*Out of Order Execution*). Mediante el uso de algoritmos y circuitos dedicados, un procesador puede detectar las dependencias entre las instrucciones y cambiar el orden de ejecución para minimizar la aparición de pipe stalls, manteniendo los mismos resultados. De esta manera, se logra que la mayor parte de las unidades del procesador permanezcan ocupadas el mayor tiempo posible.

Mejoras en este nivel eran usualmente invisibles al programador de un lenguaje de alto nivel como C++, dejando la tarea de aprovechar estas propiedades de la arquitectura a los compiladores optimizantes. Sin embargo, las ventajas de estas técnicas fueron disminuyendo a partir del año 2000 [7].

### 2.1.3. Extensiones vectoriales

Si bien las técnicas SIMD fueron desarrolladas para las supercomputadoras de los años 70 y 80, su aparición en los microprocesadores x86 modernos ocurre en 1996 con el nombre MMX (*MultiMedia eXtensions*), con mejoras luego en las extensiones SSE y AVX. AVX y AVX2 representan la última versión disponible de las instrucciones de vectorización y están presentes en la línea Intel Xeon de procesadores de alta gama y en las más recientes generaciones de procesadores para consumidores.

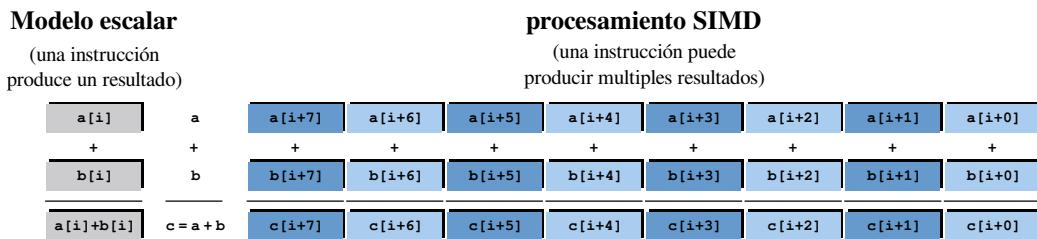

El paralelismo de datos puede ser explotado por el compilador, que analiza los ciclos de programa y detecta cuando hay operaciones independientes que pueden ser realizadas en simultáneo, dividiendo la cantidad de instrucciones totales que tiene que realizar un procesador. Un ejemplo de operación de suma vectorial puede verse en la figura 2.1.

Fig. 2.1: Ejemplo de operación de suma simultánea de ocho elementos. En SSE 4, usando la instrucción ADDPS, el procesador puede hacer estas 16 sumas en simultáneo usando un registro de 128 bits. En cambio, un procesador escalar solo podría hacerlas de a una por vez.

El uso de operaciones sobre múltiples valores ha cobrado importancia como uno de los métodos de incrementar la *performance* de ejecución. La longitud de registros SIMD de las extensiones (64 bits para MMX, 128 para SSE, 256 para AVX) se ha duplicado cada seis años, con lo cual es importante para una aplicación que sus operaciones sean lo más vectorizables posible [7]. Para esto, es ideal que las operaciones sean regulares y los ciclos sean claros y con mínimas dependencias, de modo de hacer mejor uso de estas facilidades.

### 2.1.4. Caches

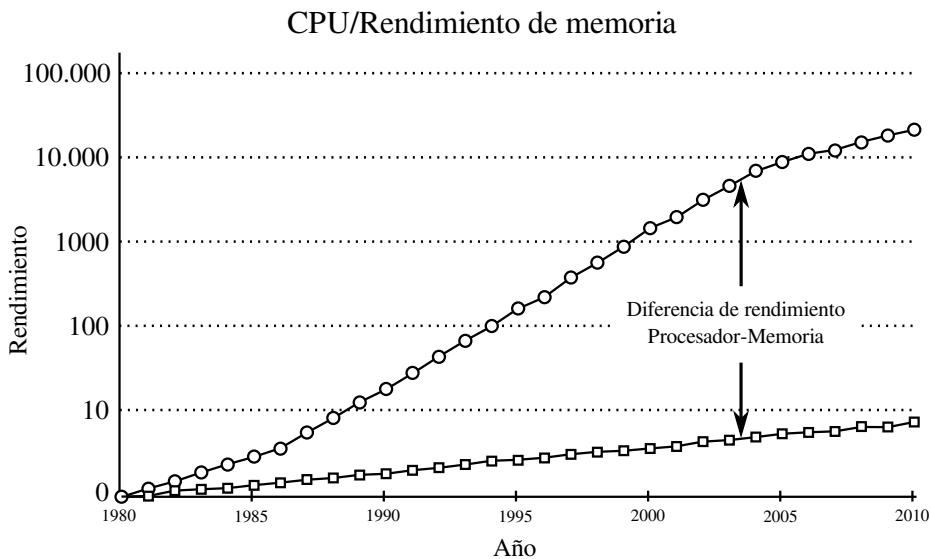

A diferencia de los procesadores, la velocidad de acceso de las memorias principales no aumentó de una manera tan significativa, como se puede ver en la figura 2.2. Como consecuencia, la memoria empezó a convertirse en un serio cuello de botella a la velocidad de ejecución de los programas.

El concepto de *localidad espacial* corresponde con la observación de que los datos con los que opera una sección de un programa suelen estar *cerca* en memoria. Los diseños de procesadores empezaron a incluir distintos tipos de caches para sacar provecho de esta situación: memorias rápidas, próximas al CPU y de menor tamaño para contener el subconjunto de los datos *cercano* al recientemente usado. Su eficacia impulsó el establecimiento de una jerarquía en orden creciente de tamaño y decreciente en velocidad, empezando por las caches L1 y siguiendo por las L2 y L3.

Fig. 2.2: Comparación entre la *performance* de CPU y memoria según el año, la diferencia de entre ellos se denomina *memory gap*. Tomado de [7].

El tamaño de una cache L1 de CPU moderno está en el orden de los 64 KB, una cache L2 en el orden de los 2 MB y una L3 en el orden de 6 MB en adelante.

Si bien la aparición y utilización de caches es transparente al programador en los procesadores de la línea x86-64, los accesos irregulares a la memoria pueden producir que la cache se cargue con datos que no volverán a ser utilizados, causando que datos que sí se vayan a reutilizar sean desalojados. El evento en que datos no se encuentren en memoria cache y deban ser buscados en la memoria principal se denomina *cache miss* y tiene un fuerte impacto en el rendimiento del programa. Por esto es que la regularidad de los accesos a memoria para hacer buen uso de caches resulta fundamental para obtener una buena *performance*.

### 2.1.5. Multiprocesadores

Dentro del área de cómputo de escritorio, servidores y estaciones de trabajo basadas en la línea x86, los procesadores MIMD (*Multiple Instruction Multiple Data*) implicaron una revolución en el abordaje de los problemas de alta *performance*, pero cada procesador individual continúa las líneas anteriores. Los diseños más utilizados se basan en un arquitectura tipo SMP (*Symmetric Multiprocessing*), en la cual todos los procesadores son iguales y comparten una misma memoria principal. Cada procesador tiene sus propios registros y se comunica con los demás mediante memoria compartida o interrupciones.

Por ejemplo, el procesador Intel Xeon E7-8800 posee 12 procesadores (núcleos o *cores*) que pueden ejecutar dos hilos simultáneamente cada uno, mediante el uso de la tecnología denominada *Hyper-Threading*.

A diferencia de los otros métodos, las mejoras posibles mediante el procesamiento paralelo en tareas son sustanciales, pero dependen del programador en gran medida. Un programa serial no se beneficiará de múltiples *cores*, incluso siendo recompilado, a menos que este paralelismo se aproveche explícitamente. Otro aspecto importante es la *escalabilidad*, que consiste en que la división de tareas mantenga a todos los procesadores disponibles

ocupados, aunque crezca la cantidad de cores que intervengan.

Un resultado importante a tener en cuenta es la denominada *Ley de Amdahl* [10], que establece una relación entre la aceleración (*speedup*) máximo alcanzable mediante un incremento en la cantidad de procesadores disponibles, el porcentaje de la aplicación que es paralelizable y el porcentaje que no lo es:

$$S(n) = \frac{1}{(1 - B) + \frac{B}{n}} \quad (2.1)$$

donde  $S$  es el *speedup* máximo de mejora alcanzable,  $B$  es la fracción del algoritmo a ejecutar que se encuentra paralelizada, y  $n$  la cantidad de hilos de ejecución paralelos con los que se dispone.

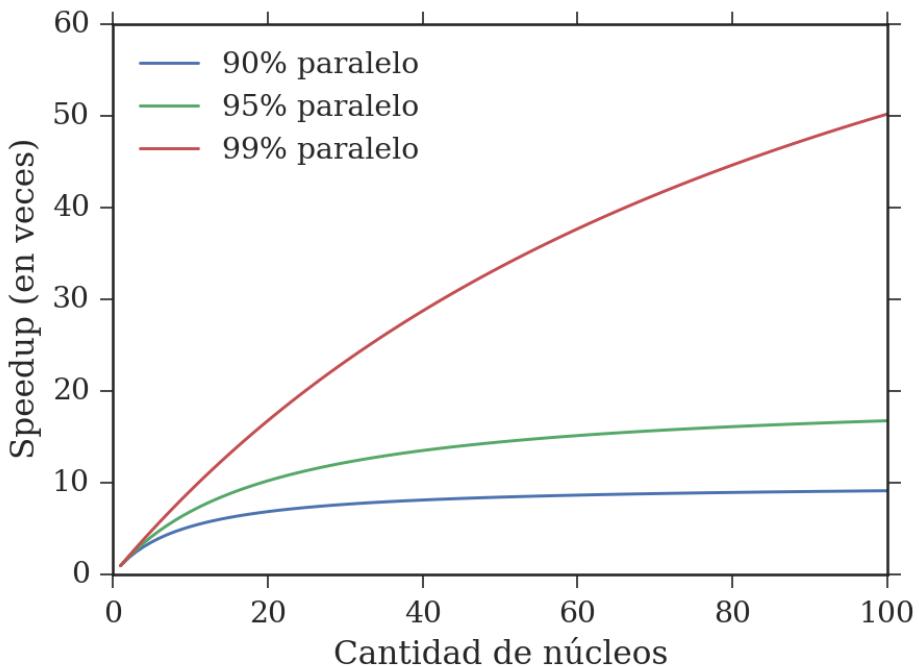

Fig. 2.3: Aceleración teórica máxima (en veces) dada por la ley de Amdahl, según la cantidad de núcleos de procesamiento.

Un ejemplo de esta ley en acción es que si 95 % del problema fuera paralelizable entonces el límite teórico de mejora es de 20 veces (el programa corriendo sobre infinitos cores se ejecutaría en un veinteavo del tiempo que originalmente requería). La figura 2.3 muestra el comportamiento de la ecuación 2.1, que define la ley de Amdahl, con distintas fracciones de código paralelo.

La ley de Amdahl describe el pico teórico de mejora posible. Esta ley es una simplificación, ya que supone que todos los cores tienen trabajo perfectamente distribuido, que no deben comunicarse entre ellos por motivos de sincronización y que no existen otras cargas adicionales introducidas por paralelización misma.

Por otro lado, la presencia de un componente común (la memoria) puede representar cuellos de botella en el acceso a los datos, ya que si el *bus* de memoria es saturado con pedidos, los procesadores deben detener forzosamente su ejecución hasta que los datos estén disponibles, eliminándose entonces el procesamiento paralelo.

Otro punto de conflicto son las caches. Como los procesadores deben tener una visión unificada y consistente de la memoria, a veces es necesario que estos sincronicen los valores de sus caches, especialmente ante una escritura de memoria. Esto se conoce como *coherencia de caches* e involucra una sincronización de alto *overhead*, ya que implica coordinación entre dos o más procesadores a través de un bus de memoria.

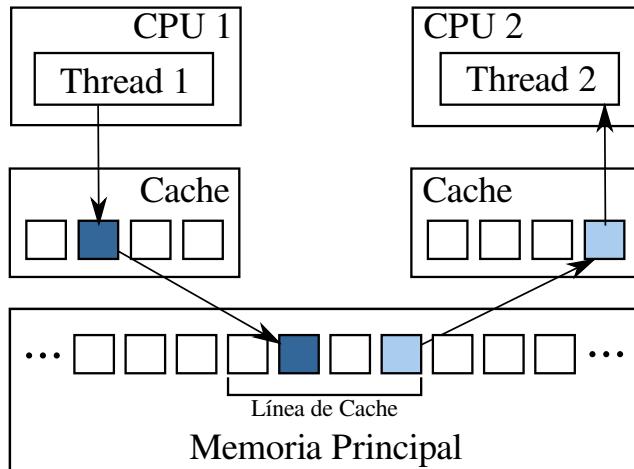

Es, en este punto, que el impacto del paralelismo en el comportamiento del programa puede ser tan fuerte como sutil. Un fenómeno que ilustra esto es el de *false sharing* (figura 2.4), que sucede cuando una variable no compartida entre *threads* reside en la misma línea de cache con una que sí. En ese caso, la variable es pasada de lado a lado entre cores aunque nunca fuese necesario, decrementando la escalabilidad del algoritmo y siendo difícil de detectar al depender intrínsecamente del sistema en el que se ejecuta.

Fig. 2.4: Esquema para ilustrar el problema de *false-sharing* entre caches en un esquema multicore. El *thread 1* escribe un valor en su cache y el *thread 2* lee un valor en su cache. Como ambos valores pertenecen a la misma línea de cache la escritura de 1 invalida la línea de donde lee 2, haciendo que tenga que releer toda la línea.

Los desafíos generados por la adición de cores influencian fuertemente los diseños de una arquitectura, no solo en procesadores estándar sino también en aceleradores como las GPUs.

## 2.2. CUDA

### 2.2.1. Introducción

Una de las arquitecturas analizadas en este trabajo es la arquitectura GPU desarrollada por Nvidia, conocida como CUDA por las siglas en inglés de *Compute Unified Device Architecture*. CUDA surge naturalmente de la aplicación del hardware desarrollado para problemas gráficos, pero aplicados al cómputo científico.

Las placas de vídeo aparecen en 1978 con la introducción de Intel del chip iSBX 275. En 1985, la Commodore Amiga incluía un coprocesador gráfico que podía ejecutar instrucciones independientemente del CPU, un paso importante en la separación y especialización de las tareas. En la década del 90, múltiples avances surgieron en la aceleración 2D para dibujar las interfaces gráficas de los sistemas operativos y, para mediados de la década, muchos fabricantes estaban incursionando en las aceleradoras 3D como agregados a las

placas gráficas tradicionales 2D. A principios de la década del 2000, se agregaron los *shaders* a las placas, pequeños programas independientes que corrían nativo en el GPU, y se podían encadenar entre sí, uno por pixel en la pantalla [11]. Este paralelismo es el desarrollo fundamental que llevó a las GPU a poder procesar operaciones gráficas órdenes de magnitud más rápido que el CPU.

En el 2006, Nvidia introduce la arquitectura G80, que es el primer GPU que deja de resolver únicamente problemas de gráficos para pasar a un motor genérico donde cuenta con un set de instrucciones consistente para todos los tipos de operaciones que realiza (geometría, vertex y pixel shaders) [12]. Como subproducto de esto, la GPU pasa a tener procesadores simétricos más sencillos y fáciles de construir. Esta arquitectura es la que se ha mantenido y mejorado en el tiempo, permitiendo a las GPU escalar masivamente en procesadores simples, de baja frecuencia de reloj y con una disipación térmica manejable.

Los puntos fuertes de las GPU modernas consisten en poder atacar los problemas de paralelismo de manera pseudo-explicita, y con esto poder escalar “fácilmente” si solamente se corre en una placa con más procesadores [13].

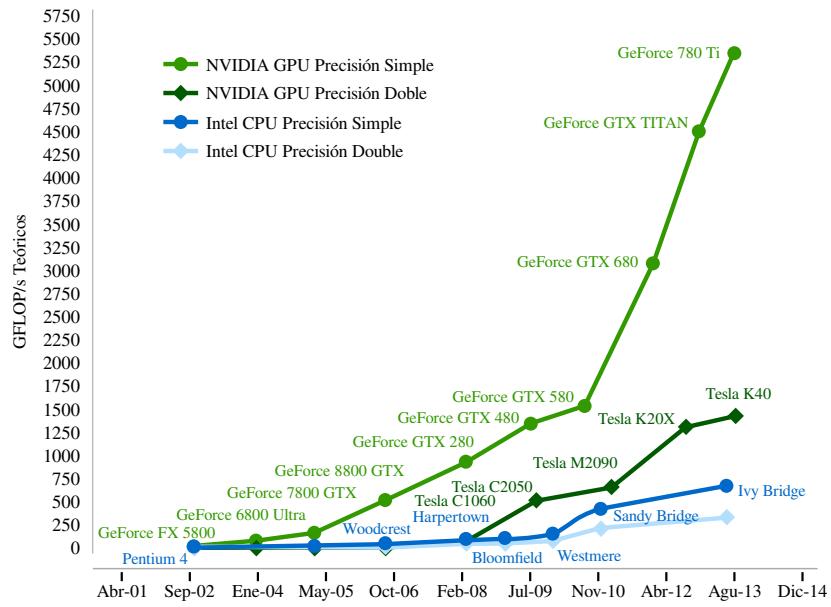

Técnicamente, esta arquitectura cuenta con entre cientos y miles de procesadores especializados en cálculo de punto flotante, procesando cada uno un *thread* distinto pero trabajando de manera sincrónica agrupados en bloques. Cada procesador, a su vez, cuenta con entre 63 a 255 registros [14, 15]. Las GPU cuentan con múltiples niveles de cache y memorias especializadas (subproducto de su diseño fundamental para gráficos). Estos no poseen instrucciones SIMD, ya que su diseño primario está basado en cambio, en SIMT (*Single Instruction Multiple Thread*), las cuales se ejecutan en los bloques sincrónicos de procesadores. De este modo, las placas modernas como la Nvidia Tesla K40 alcanzan poder de cómputo de 4,3 TFLOPs (4300 mil millones de operaciones de punto flotante por segundo) en cálculos de precisión simple, 1,7 TFLOPs en precisión doble y 288 GB/seg de transferencia de memoria, usando 2880 CUDA Cores [16]. Para poner en escala la concentración de poder de cálculo: una computadora usando solo dos de estas placas posee una capacidad de cómputo comparable a la supercomputadora más potente del mundo en Noviembre 2001 [17]. Una comparativa del poder de cómputo teórico entre GPUs y CPUs puede ver en la figura 2.5.

Para poder explotar la arquitectura CUDA, los programas deben ser diseñados de manera de que el problema se pueda particionar usando el modelo de grilla de bloques de *threads*. Para este propósito es que Nvidia desarrolló el lenguaje CUDA.

Hoy en día, poder aprovechar la potencialidad de las GPU requiere una reescritura completa de los códigos ya existentes desarrollados para CPU y un cambio de paradigma importante, al dejar de tener vectorización, paralelización automática y otras técnicas tradicionales de optimización en CPU. Sin embargo, este trabajo ha rendido sus frutos en muchos casos: en los últimos seis años, la literatura de HPC con aplicaciones en GPU ha explotado con desarrollos nuevos basados en la aceleración de algoritmos numéricos (su principal uso). Por este motivo, este trabajo no ahondará en las particularidades del lenguaje CUDA y su modelo de paralelismo, más allá de lo estrictamente necesario para analizar *performance*. Para más información se puede consultar la bibliografía [12, 18, 19].

Además, no todas las aplicaciones deben reescribirse de manera completa. Con la introducción de las bibliotecas CuBLAS y CuFFT, se ha buscado reemplazar con mínimos cambios las históricas bibliotecas BLAS y FFTw, piedras fundamentales del cómputo HPC [20, 21].

Nuevas soluciones para la portabilidad se siguen desarrollando: las bibliotecas como Thrust [22], OpenMP 4.0 [23] y OpenACC 2.0 [24] son herramientas que buscan generar

Fig. 2.5: Picos teóricos de *performance* en GFLOPS/s. Tomado de [13].

código que puedan utilizar eficientemente el acelerador de cómputo que se haya disponible. Estas herramientas permiten definir las operaciones de manera genérica y dejan el trabajo pesado al compilador para que subdivida el problema de manera que el acelerador (CPU, GPU, MIC) necesite. Obviamente, los ajustes finos siempre quedan pendiente para el programador especializado, pero estas herramientas representan un avance fundamental al uso masivo de técnicas de paralelización automáticas, necesarias hoy día y potencialmente imprescindibles en el futuro.

### 2.2.2. Organización de procesadores

Los procesadores GPGPU diseñados por Nvidia han sido reorganizados a lo largo de su existencia múltiples veces pero conservan algunas líneas de diseño a través de su evolución. A continuación se describe la organización definida en la arquitectura **Fermi** y luego analizaremos las diferencias con **Kepler**.

Las arquitecturas de las GPUs se centran en el uso de una cantidad escalable de procesadores *multithreaded* denominados *Streaming Multiprocessors* (SMs). Un multiprocesador está diseñado para ejecutar cientos de threads concurrentemente, usando sus unidades aritméticas llamadas *Streaming Processors* (SPs). Las instrucciones se encadenan para aprovechar el paralelismo a nivel instrucción dentro de un mismo flujo de ejecución, y funcionando en conjunto con el paralelismo a nivel de *thread*, usado de manera extensa a través del hardware. Todas las instrucciones son ejecutadas en orden y no hay predicción de saltos ni ejecución especulativa, todo se ejecuta solamente cuando se lo necesita [19].

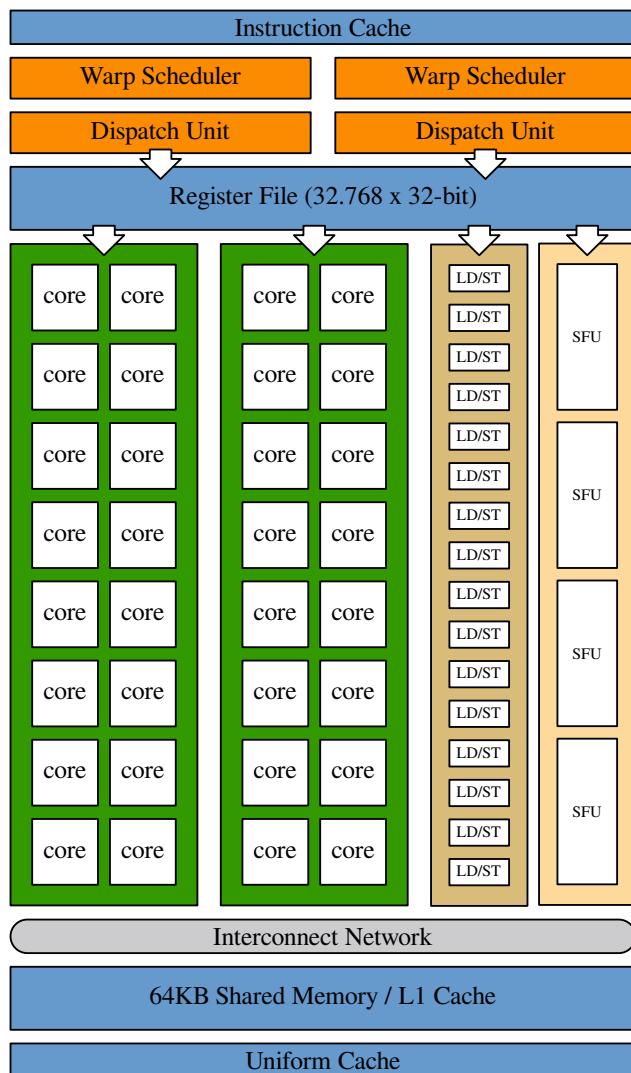

Los SMs (figura 2.6) son unidades completas de ejecución. Cada uno de ellos tiene 32 SPs interconectados entre sí que operan sobre un *register file* de 64 KB común a todos. Los SMs cuentan con múltiples unidades de *Load/Store*, que permiten realizar accesos a memoria independientes. Existen cuatro unidades de SFU (*Special Function Unit*) por SM, para realizar rápidamente operaciones matemáticas trascendentales (trigonométricas, potencias, raíces, etc.). Cada SM ejecuta simultáneamente una cantidad fija de threads,

Fig. 2.6: Diagrama de bloques del SM de GF100 Fermi. Basado en [14].

llamado *warp*, con cada uno de estos corriendo en un SP. Las unidades de despacho de warps se encargan de mantener registro de qué *threads* están disponibles para correr en un momento dado y permiten realizar cambios de contexto por hardware eficientemente ( $< 25\mu s$ ) [25]. Con esto, se pueden ejecutar concurrentemente dos warps distintos para esconder la latencia de las operaciones. En precisión doble, esto no es posible, así que hay solamente un warp corriendo a la vez.

Un SM cuenta con una memoria común de 64 KB que se puede usar de forma automática tanto como memoria compartida común a todos los *threads* como cache L1 para todos los accesos a memoria.

Fig. 2.7: Diagrama de bloques de GF100 Fermi. Tomado de [14].

Por como funciona un pipeline gráfico clásico, los SM se agrupan de a cuatro en GPCs (*Graphics Processing Cluster*) y no interactúa con el modelo de cómputo de CUDA. Un esquema de esta división global de los SM y cómo se comunican puede verse en la figura 2.7.

Todos los accesos a memoria global (la memoria por fuera del procesador) se realizan a través de la cache L1 de cada SM y a través de la L2 del todo el procesador. Esta L2 consiste de seis bancos compartidos de 128 KB. Estas caches se comunican de manera directa tanto con la DRAM propia de la placa como con el bus PCI Express por el cual pueden comunicarse dos placas entre sí, sin pasar por CPU, y son *write-through*, es decir cada escritura se hace tanto en la DRAM como en la memoria cache.

Como estos procesadores implementan el estándar IEEE754-2008, cuentan con operaciones de precisión simple y doble acorde al mismo, por lo cual los cálculos intermedios en operaciones como FMA (*Fused Multiply-Add*), que toma tres operandos y devuelve el producto de dos de ellos sumado al tercero, no pierden precisión por redondeo.

### 2.2.3. Organización de la memoria

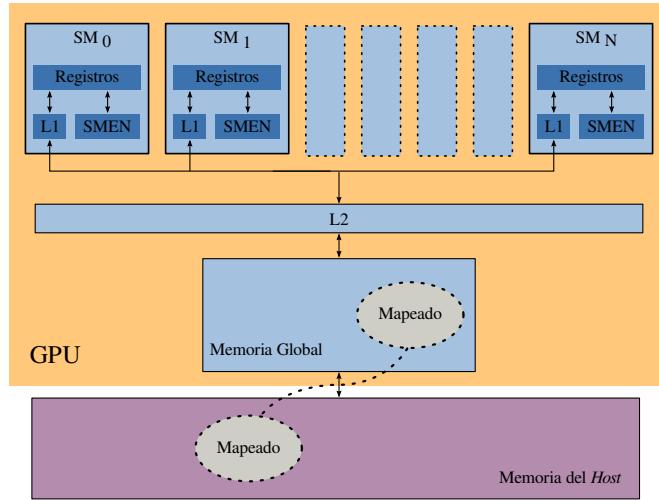

La memoria de la GPU es uno de los puntos cruciales de esta arquitectura, un esquema gráfico puede observarse en la figura 2.8. Esta se subdivide entre memorias on-chip y memorias on-board, de acuerdo a su ubicación y latencia de acceso, en cuatro categorías distintas:

- Registros

- Memoria local

- Memoria compartida

- Memoria global

Cada *thread* de ejecución cuenta con una cantidad limitada de registros de punto flotante de 32 bits con latencia de un par de ciclos de clock. A su vez, existe una cantidad finita de registros totales que cuenta un SM (oscila entre 16535 y 65535 registros). Por su baja latencia son la clase principal de almacenamiento temporal.

La memoria local es una memoria propia de cada *thread*, y se encuentra almacenada dentro de la memoria global. Esta memoria es definida automáticamente por el compilador y sirve como área de almacenamiento cuando se acaban los registros: los valores anteriores se escriben a esta memoria, dejando los registros libres para nuevos valores en cálculos, y cuando se terminan estos cálculos se carga los valores originales nuevamente. Cuenta con las mismas desventajas que la memoria global, incluyendo su tiempo de acceso.

La memoria compartida, o *shared*, es una memoria que es visible para todos los *threads* dentro de un mismo SM. Cada *thread* puede escribir en cualquier parte de la memoria compartida dentro de su bloque y puede ser leído por cualquier otro *thread* de este. Es una memoria muy rápida, on-chip, y que tarda aproximadamente 40 ciclos de acceso [26]. Esta memoria es compartida con la cache L1, la cual tiene capacidad de entre 16 KB y 64 KB configurable por software. Esta memoria se encuentra dividida en 32 bancos de 2 KB de tamaño, permitiendo que cada uno de los 32 *threads* acceda independientemente a un float. Si hubiera conflicto, los accesos a ese banco se serializarían, aumentando la latencia de la llamada [18].

La memoria global es la memoria principal fuera del chip de la GPU. Esta es de gran tamaño (de entre 1 GB y 12 GB) y es compartida por todos los SM de la GPU y los CPU que integran el sistema. Es decir, tanto los GPU como los CPU pueden invocar las funciones de CUDA para transferir datos entre la memoria de la placa y la memoria RAM de *host*. La latencia de acceso a la memoria global es de cientos de ciclos [26], sumamente lenta en comparación con el procesador. La memoria global también puede ser mapeada, o *pinneada*, para que exista una copia de esa reserva tanto en la memoria en la placa como en la memoria principal del procesador. El driver de CUDA va a mantener la consistencia entre ambas de manera asíncrona, evitando la necesidad de hacer copias de memoria explícitas. No es ilimitada la cantidad de memoria mapeada posible, por lo que es importante saber elegir qué elementos se van a almacenar de esta manera.

Adicionalmente, la GPU cuenta con múltiples niveles de memorias cache para poder aminorar el hecho de que el principal cuello de botella del cómputo es la latencia en los accesos a memoria global. Estas se dividen en cuatro:

- Cache L1

Fig. 2.8: Esquema de la jerarquía de memorias en GPU, detallando de las disponibles en cada SM, la memoria compartida (SMEN), la L2 global, la memoria de la placa (global) y la mapeada entre el *host* y la placa de video. Tomado de [18].

- Cache L2

- Cache constante

- Cache de textura

La cache L1 es dedicada por SM. Esta cache fue introducida en Fermi y su diseño hace que también esté dedicada a la memoria compartida, por lo que es posible en tiempo de ejecución darle directivas a la GPU que asigne más memoria cache o más memoria compartida, permitiendo a los bloques tener mayores espacios de memorias compartidas o mayores *hit rates* de caches.

La cache L2 es común a todos los SM de la GPU, donde, a partir de Fermi en Nvidia, todos los accesos de lectura y escritura a memoria global y textura pasan a través de esta [14].

La cache constante es una cache sobre la memoria global dedicada solamente a lecturas de memoria. Esta es muy reducida (solo cuenta con 64 KB) y está optimizada para muchos accesos a la misma dirección. Cuando un *thread* lee esta memoria, se retransmite a los demás *threads* del warp que estén leyendo esa misma dirección, reduciendo el ancho de banda necesario. Si, en cambio, los *threads* leen distintas direcciones, los accesos se serializan. Cuando hay un *miss* de esta memoria, la lectura tiene el costo de una lectura de memoria global.

La cache de textura es una cache sobre la memoria global que presenta no solo localidad espacial, como la mayoría de las caches de procesadores normales (es decir, la cache contiene una porción consecutiva de la memoria principal), sino que se le puede agregar el concepto de dimensiones, para poder modelar datos en más de una dimensión. Esto se adapta de muy bien a los problemas de gráficos en 2D y 3D, y es una herramienta clave a la hora de minimizar los accesos a matrices no solo por filas sino por columnas. Esta cache se debe definir en momento de compilación en el código, ya que tiene límites espaciales (necesarios para poder definir áreas de memoria sobre la cual operar) y a su vez se debe acceder a los datos subyacentes a través de funciones específicas. Una característica

adicional de esta cache es que como necesita resolver estos accesos no convencionales a la memoria, cuenta con una unidad propia de resolución de direcciones. Esta unidad tiene limitantes en cuanto a sus posibilidades, ya que no posee un ancho de banda suficiente como para resolver todos los accesos a memoria globales que podrían surgir, por lo cual su uso debe ser criterioso.

#### 2.2.4. Esquema de paralelismo

Al ser una arquitectura masivamente paralela desde su concepción, CUDA presenta varios niveles de paralelismo, para agrupar lógicamente el cómputo y poder dividir físicamente su distribución. Los principales son:

- Bloques de *threads*

- Grilla de bloques

- Streams

- Múltiples placas

El paralelismo a nivel de bloque instancia una cantidad de *threads*, subdivididos lógicamente en 1D, 2D o 3D. Los *threads* internamente se agrupan de a 32, es decir, un *warp*. Cada uno de estos *threads* va a contar con una manera de identificarlos únicamente: un **blockId** y, dentro de cada bloque, su propio **threadId**. Además, van a correr simultáneamente en el mismo SM y van a ser puestos y sacados de ejecución de a un warp dinámicamente por el *scheduler* de hardware que cuenta cada SM. Para compartir información entre ellos, se puede utilizar la memoria compartida o las instrucciones de comunicación de *threads* intrawarp (solo disponibles a partir de Kepler [15]).

El paralelismo a nivel de grilla determina una matriz de bloques de ejecución que partitiona el dominio del problema. El *GigaThread Scheduler* va a ejecutar cada bloque en un SM hasta el final de la ejecución de todos los *threads* de este. Los bloques no comparten información entre sí. Por esto, no pueden ser sincronizados mediante memoria global ya que no se asegura el orden en el que serán puestos a correr, y un bloque mantiene su SM ocupado hasta que termine de ejecutar, bloqueando a los demás (es decir, no hay *preemption* en los SM).

El paralelismo de stream es una herramienta empleada para hacer trabajos concurrentes usando una sola placa. Esta técnica permite que múltiples kernels (unidades de código en CUDA) o copias de memoria independientes estén encolados, para que el driver pueda ejecutarlas simultáneamente si se están subutilizando los recursos, de forma de minimizar tiempo ocioso del dispositivo. Los streams permiten kernels concurrentes pero cuentan con importantes restricciones que generan sincronización implícita, lo cual hay que tener presente si se desea mantener el trabajo de forma paralela.

El paralelismo a nivel de placa consiste en poder distribuir la carga del problema entre distintas GPUs dispuestas en un mismo sistema compartiendo una memoria RAM común como si fuera un software multithreaded tradicional. CUDA no cuenta con un modelo implícito de paralelismo entre distintas placas, pero es posible hacerlo manualmente eligiendo de manera explícita qué dispositivo usar. Las placas se pueden comunicar asíncronamente entre sí, tanto accediendo a las memorias globales de cada una como ejecutando código remotamente. En las versiones modernas del driver de CUDA, también

pueden comunicarse directamente las placas entre sí a través de la red, permitiendo escalar multinodo fácilmente en un cluster de cómputo [18].

### 2.2.5. Diferencias entre Tesla, Fermi, Kepler

Hasta ahora se describió la arquitectura vista desde el punto de vista Fermi, que es la segunda arquitectura GPGPU diseñada por Nvidia. Fermi es la evolución de Tesla, construida para desacoplar aún más los conceptos de procesamiento gráfico de modo de lograr un procesador más escalable y de propósito general. La arquitectura sucesora a Fermi es Kepler, presentada en el 2012, con las metas de disminuir el consumo y aumentar la potencia de cálculo [15].

| Características        | Tesla (GT200)   | Fermi (GF100)   | Kepler (GK110)   |

|------------------------|-----------------|-----------------|------------------|

| Año introducción       | 2006            | 2010            | 2012             |

| Transistores           | 1400 millones   | 3000 millones   | 3500 millones    |

| Tecnología fabricación | 65 nm           | 40 nm           | 28 nm            |

| SMs                    | 30              | 16              | 15               |

| SP / SM                | 8               | 32              | 192              |

| Caché L1               | -               | 16 - 48 KB      | 16 - 32 - 48 KB  |

| Caché L2               | -               | 768 KB          | 1536 KB          |

| Memoria Shared/SM      | 16 KB           | 16 - 48 KB      | 16 - 32 - 48 KB  |

| Registros/Thread       | 63              | 63              | 255              |

| Pico Precisión Simple  | 240 MAD / clock | 512 FMA / clock | 2880 FMA / clock |

| Pico GFLOPS Simple     | 933             | 1345            | 3977             |

| GFLOPS/Watt            | 3,95            | 5,38            | 15,9             |

Tab. 2.2: Tabla comparativa de las características más prominentes de las tres arquitecturas de CUDA.

En la tabla 2.2 se ve una comparación de los recursos que están más directamente relacionados a la *performance* de un dispositivo GPU. Se puede apreciar el crecimiento notable del poder de cómputo debido a las tecnologías de fabricación, que permitieron aumentar la cantidad de transistores por unidad de superficie. También se puede comprobar que, a diferencia de los CPU, las arquitecturas GPGPU decidieron utilizar esos nuevos transistores disponibles para más núcleos de procesamiento, en vez de dedicarlos a aumentar las memorias cache, que crecieron mínimamente (comparando contra las caches de CPU).

Una de las diferencias más notorias entre Tesla y Fermi es la presencia de FMA contra el MAD (*Multiply - Add*). El MAD realiza la multiplicación y la acumulación en dos pasos, pero más rápidos que hacerlos independientemente por tener hardware dedicado. Debido a que debe redondear entre los pasos, pierde precisión y no respeta completamente el estándar IEEE754-2008. El FMA, en cambio, lo hace en una sola operación, y sin redondeos intermedios.

La métrica usada por Nvidia para publicitar la *performance* de estos dispositivos y poder compararlos entre sí, y contra CPU, son los GFLOPS. Esta unidad mide cuantas operaciones de punto flotante de precisión simple se pueden realizar por segundo. Los GFLOPs son utilizados también por los clusters en el ranking TOP500, donde se ordenan de acuerdo a la *performance* medida usando un software estandarizado, LINPACK. No solo

es notable como se cuadruplicó la *performance* (teórica) en solamente seis años, sino que aún más importante es como mejoró la *performance* por Watt. Esto también se ve en que Kepler tiene menos SM que Fermi o Tesla, pero son mucho más poderosos y eficientes. La tecnología de fabricación ha ayudado a la disminución del consumo, un problema que acechaba a los diseños Fermi, ya que sus consumos superiores a 200W por dispositivo los hacían muy difíciles de refrigerar incluso en clusters de HPC. Se puede apreciar entonces la estrategia de mercado de Nvidia de introducirse en las supercomputadoras de todo el mundo, donde el consumo y la refrigeración son factores limitantes (mucho más aún que, por ejemplo, en computadoras de escritorio) [7].

### 2.2.6. CUDA, Herramientas de desarrollo, profiling, exploración

Para soportar una arquitectura masivamente paralela, se debe usar una ISA (*Instruction Set Architecture*) diseñada especialmente para el problema. En el caso de CUDA, esta ISA se denominada PTX y debe poder soportar conceptos fundamentales del cómputo GPGPU: grandes cantidades de registros, operaciones en punto flotante de precisión simple y doble, y FMA (fused multiply-add). Además, el código compilado para GPU debe ser agnóstico al dispositivo que lo va a correr, por lo cual la parallelización no debe estar demasiado atada a este, sino que el dispatching lo debe poder determinar el driver de la placa en tiempo de ejecución. Un último requerimiento clave de esta ISA es que debe soportar hacer ajustes manuales, para poder construir partes claves de ciertas bibliotecas frecuentemente usadas (como las rutinas de BLAS de álgebra lineal) [14].

El lenguaje CUDA es una extensión de C++, con ciertas características agregadas para poder expresar la subdivisión de las rutinas en *threads* y bloques, junto con mecanismos para especificar qué variables y funciones van a ejecutarse en la GPU y en el CPU. Una característica de CUDA es que todas las llamadas a los kernels de ejecución son asincrónicas, por lo que es relativamente sencillo solapar código en GPU y CPU. A su vez se cuenta con múltiples funciones opcionales, con distinta granularidad, que permiten esperar a que todas las llamadas asíncronas a GPU finalicen, agregando determinismo en forma de barreras de sincronización al lenguaje.

El código CUDA compila usando nvcc, una variante del GNU gcc que se encarga de generar el código PTX para las funciones que se van a ejecutar en las GPU. Este código objeto después se adosa normalmente con el resto del código que corre en CPU y se genera un binario ejecutable.

Nvidia, además, provee herramientas de profiling para explorar cómo se están utilizando los recursos durante la ejecución. Éstas son esenciales para optimizar, puesto que los limitantes de GPU son sumamente distintos a los de CPU, presentando dificultades conceptuales incluso para programadores experimentados. Las herramientas de profiling no solo muestran *runtime*, sino que sirven para ver dónde hay accesos a memoria excesivos, puntos de sincronización costosos, limitantes en los registros y cómo se superponen las llamadas asíncronas.

El uso de todas estas herramientas fue vital en este trabajo para poder entender cómo funciona la arquitectura en detalle, cómo medir *performance* y utilización, y cómo los cambios realizados impactaron en las distintas generaciones de dispositivos.

### 2.2.7. Requerimientos de un problema para GPGPU

Dada la organización de un procesador GPU, un problema debe exhibir al menos las siguientes características para que tenga potencialidad para poder aprovechar las características y recursos disponibles en esta arquitectura:

1. El problema debe tener una gran parte paralelizable.

2. El problema debe consistir, mayormente, de operaciones numéricas.

3. El problema debe poder ser modelado, en su mayor parte, utilizando arreglos o matrices.

4. El tiempo de cómputo debe ser muy superior al tiempo de transferencia de datos.

El ítem 1 se refiere a que debe existir alguna forma de partir el problema en subproblemas que puedan realizarse simultáneamente, sin que haya dependencias de resultados entre sí. Si el problema requiere partes seriales, lo ideal es que se las pueda dividir en partes independientes que sean etapas de una cadena de procesos, donde cada una de éstas exhiban características fuertemente paralelas. Como las arquitecturas masivamente paralelas tienen como desventaja una menor eficiencia por núcleo, si el problema no se puede dividir para maximizar la ocupación de todos los procesadores disponibles, va a resultar muy difícil superar en eficiencia a los procesadores seriales.

El ítem 2 habla acerca de que el método de resolución de los problemas debe provenir de una aplicación numérica o de gran carga aritmética. El set de instrucciones de las arquitecturas GPGPU están fuertemente influenciados por las aplicaciones 3D que las impulsaron en un principio. Éstas consisten mayormente de transformaciones de álgebra lineal para modelar iluminación, hacer renders o mover puntos de vistas. Todos estos problemas son inherentemente de punto flotante, por lo cual el set de instrucciones, las ALUs internas y los registros están optimizados para este caso de uso.

El ítem 3 menciona que los problemas que mejor se pueden tratar en esta arquitectura se pueden representar como operaciones entre arreglos o matrices de dos, tres o cuatro dimensiones. Las estructuras de datos no secuenciales en memoria incurren en múltiples accesos a memoria para recorrerlas y, en las arquitecturas GPGPU, generan un gran cuello de botella. Además, suelen ser difíciles de paralelizar en múltiples subproblemas. Tener como parámetros de entrada matrices o arreglos que se puedan partir fácilmente producen en overheads mínimos de cómputo y permiten aprovechar mejor las memorias caches y las herramientas de prefetching que brinda el hardware.

Item 4 ataca uno de los puntos críticos de esta arquitectura. Para poder operar con datos, se requiere que estén en la memoria de la placa, no en la memoria de propósito general de la computadora. Se debe, entonces, hacer copias explícitas entre las dos memorias, ya que ambas tienen espacios de direcciones independientes. Esta copia se realiza a través de buses que, a pesar de tener un gran *throughput*, también tienen una gran latencia (del orden de milisegundos). Por lo tanto, para minimizar el tiempo de ejecución de un programa usando GPGPUs, se debe considerar también el tiempo de transferencia de datos a la hora de determinar si el beneficio de computar en menor tiempo lo justifica. Las nuevas versiones de CUDA buscan brindar nuevas herramientas para simplificar este requerimiento, proveyendo espacio de direccionamiento único y memoria unificada [18], pero siguen siendo copias de memoria a través de los buses (aunque asincrónicas).

Estas características limitan enormemente la clase de problemas que una GPGPU puede afrontar, y suelen ser una buena heurística para determinar de antemano si vale la pena invertir el tiempo necesario para la implementación y ajuste fino.

### 2.2.8. Diferencia entre CPU y GPU - Procesadores especulativos

Hasta ahora, solo se consideraron a los GPUs de forma aislada, observando las prestaciones del hardware y una aproximación a la manera en que se escriben los programas para esta arquitectura. La esencia de GPGPU se puede apreciar mejor comparándola contra los motivos de la evolución de CPU, y los problemas que se fueron enfrentando los diseños siguiendo la historia de los componentes que fueron apareciendo en estos. Esto se mostró en la tabla 2.1 (página 8), que detalla algunos de los eventos más importantes que aceleraron la *performance* de los CPU.

Lo clave es observar el siguiente patrón: “*no desechar algo que pudiéramos necesitar pronto*”, “*intentar predecir el futuro de los condicionales*”, “*intentar correr múltiples instrucciones a la vez porque puede llegar a bloquear en alguna de ellas*”.

Todos estos problemas han convertido al CPU en un dispositivo que gira alrededor de la especulación, de los valores futuros que pueden tener las ejecuciones, del probable reutilización de datos. En un CPU moderno (por ej. Intel Xeon E7-8800 [27]) las unidades que verdaderamente realizan las operaciones lógico-aritméticas (las ALU) son muy pocas en comparación con la cantidad utilizadas para las operaciones de soporte.

En contraste, los dispositivos GPU son verdaderos procesadores de cómputo masivo. Están diseñadas para resolver constantemente operaciones muy bien definidas (instrucciones de punto flotante en su mayoría). Comparativamente con un CPU, las ALU de las GPU son bastante pobres y lentas. No funcionan a las mismas velocidades de clock (rara vez superan 1,1 GHz) y sus SP deben estar sincronizados entre sí. Pero la gran ventaja esta en la cantidad.

Un CPU cuenta con pocas ALU por core, dependiendo de la cantidad de cores y del tamaño de sus operaciones SIMD (alrededor de 16 cores por *die* de x86 es el tope de línea ofrecido actualmente, procesando de a 32 bytes simultáneamente). Un GPU cuenta con miles de ALUs en total (más de 2500 CUDA cores en una Tesla K20 [16]). El diseño de esta arquitectura concibe la escalabilidad cuantitativa de las unidades de cómputo como la característica esencial a tener, tanto por su énfasis fundamental, las aplicaciones gráficas, como para su aspecto de coprocesador numérico de propósito general.

Por contrapartida, los GPUs disponen de pocas unidades de soporte del procesamiento. Éstos no disponen de pipelines especulativos, el tamaño de las caches están a órdenes de magnitud de las de CPU, la latencia a las memorias principales de la GPU están a centenas de clocks de distancia, etc. La arquitectura supone que siempre va a tener más trabajo disponible para realizar, por lo cual en vez de intentar solucionar las falencias de un grupo de *threads*, directamente pone al grupo en espera para más adelante y continúa procesando otro warp de *threads*. Se puede notar que durante del diseño de la arquitectura CUDA, buscaron resolver el problema del cómputo masivo pensando en hacer más cuentas a la vez y recalcular datos, si fuera necesario. Esto es una marcada diferencia con respecto a los CPU, que están pensados en rehacer el menor trabajo posible e intentar mantener todos los datos que pueda en las memorias caches masivas.

Nuevamente, en este punto se puede apreciar el legado histórico de los CPU. Al tener que poder soportar cualquier aplicación, no pueden avocarse de lleno a una sola problemática. Para las arquitecturas GPGPU, el hecho de no tener que diseñar un procesador

de propósito general compatible con versiones anteriores, permitió un cambio radical a la hora de concebir una arquitectura de gran throughput auxiliar al procesador, no reemplazándolo sino más bien adicionando poder de cómputo [28].

Las arquitecturas Tesla, Fermi y Kepler conciben el diseño de un procesador de alto desempeño. Su meta principal es poder soportar grandes cantidades de paralelismo, mediante el uso de procesadores simétricos, pero tomando la fuerte restricción de “*no siempre tiene que andar bien*”. Es decir, los diseñadores suponen que el código que van a ejecutar está bien adaptado a la arquitectura y no disponen casi de mecanismos en el procesador para dar optimizaciones post-compilación. Relajar esta restricción permite romper con el modelo de cómputo de CPU y definir nuevas estrategias de paralelismo, que no siempre se adaptan bien a todos los problemas, pero para el subconjunto de los desafíos que se presentan en el área de HPC y de videojuegos han probado ser un cambio paradigmático.

### 2.2.9. Idoneidad para la tarea

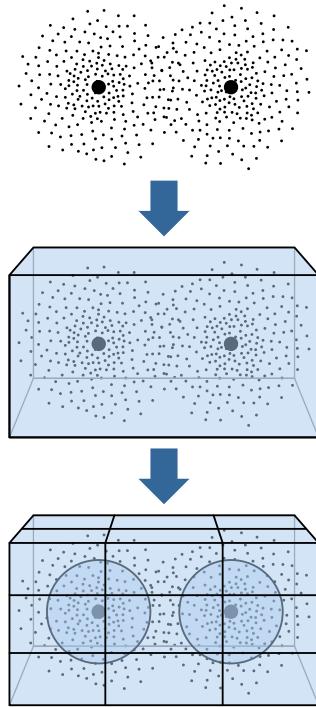

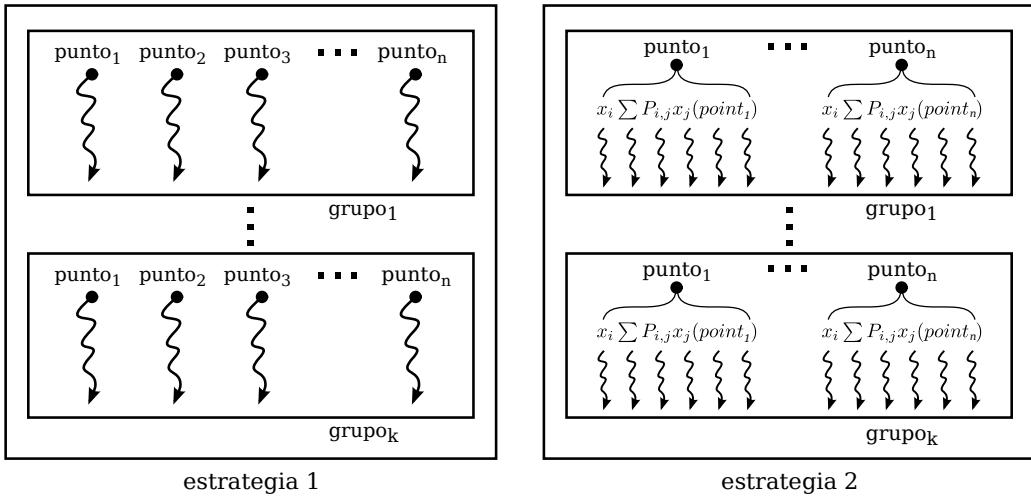

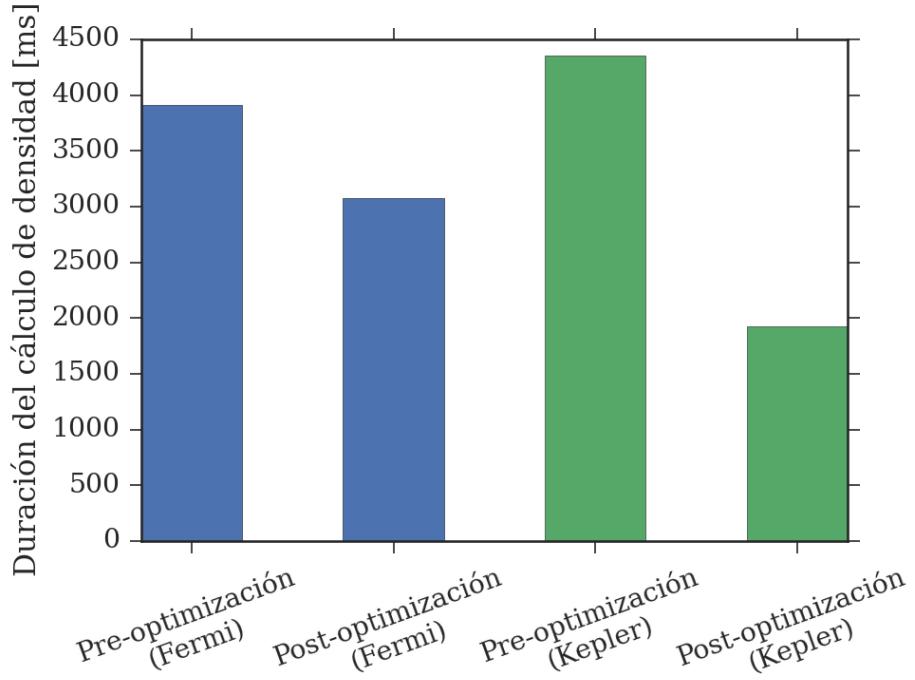

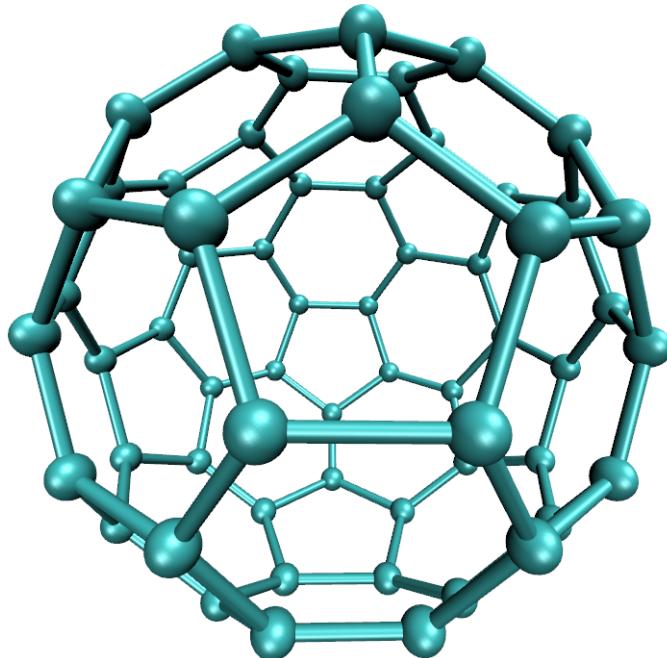

El problema de QM/MM enfrentado en este trabajo cuenta con múltiples operaciones matemáticas de gran volumen de cálculos. En particular, las operaciones matriciales constituyen los principales cuellos de botella en esta aplicación. Estas operaciones se realizan para varios grupos dentro de una grilla de integración (ecuación 1.5), los cuales se pueden realizar de manera independiente (y por lo tanto en paralelo).

Para obtener los valores numéricos de densidad buscados en los puntos, se deben obtener las derivadas primeras y segundas, lo cual implica hacer múltiples operaciones de multiplicación matricial. Este tipo de problemas está estudiado fuertemente en la literatura debido a la multiplicidad de aplicaciones de diferentes campos que requieren de operaciones de álgebra lineal.

En nuestro caso, para un sistema se requieren miles de estas multiplicaciones entre matrices, algunas con matrices de más de  $500^2$  elementos. Como LIO es un proyecto de resolución numérica de QM/MM, los problemas enfrentados son casi, en su totalidad, operaciones de punto flotante. Luego, dadas las características de contar con un fuerte nivel de paralelismo en los cuellos de botella y de ser operaciones mayormente de punto flotante, se determinó que el uso de GPGPU para este problema era promisorio, en comparación con arquitecturas de propósito general con menos poder de cómputo. La exploración original de esta arquitectura trajo buenos resultados, por lo que se prosiguió su análisis como un camino prometedor [4].

## 2.3. Xeon Phi

### 2.3.1. Introducción

La arquitectura Xeon Phi es la culminación de un trabajo iniciado por Intel en 2004, previendo la necesidad de paralelismo masivo para aplicaciones futuras. Saliendo al mercado al final de 2012 y con el propósito de competir en cómputo intensivo con Nvidia CUDA, ha ganado gran tracción dentro de HPC a pesar de ser muy reciente. Por ejemplo, Xeon Phi ha sido implementado en la supercomputadora Tianhe-2 de la Universidad de Sun Yat-Sen en China, listada en Top 500 como la supercomputadora más rápida del mundo en Junio 2013, Noviembre 2013, Junio 2014 y Noviembre 2014 [29, 30, 31]. Los 16000 nodos de esta supercomputadora contienen dos Ivy Bridge Xeon y tres coprocesadores Xeon Phi cada uno, dando un poder total de cómputo teórico de 54,9 PetaFLOPS.

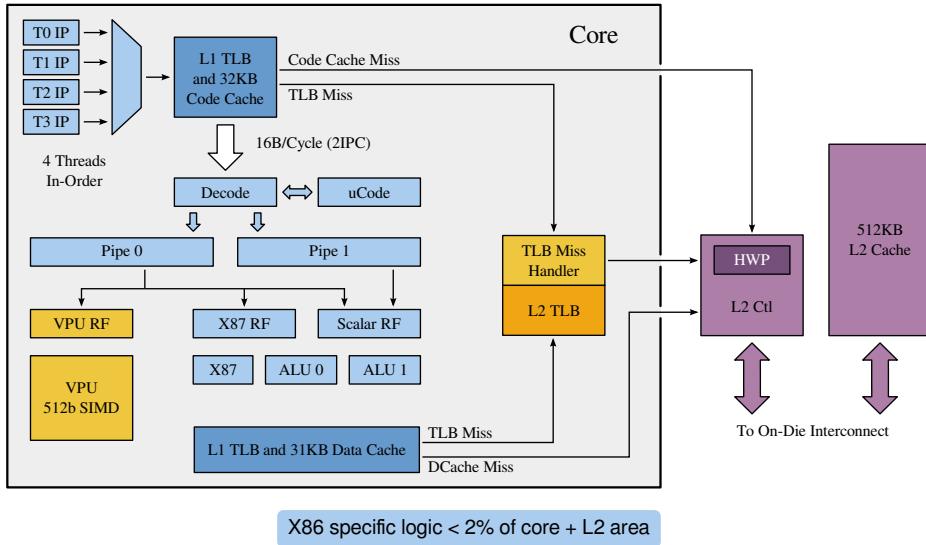

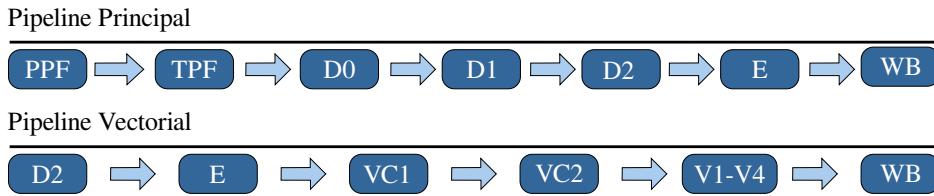

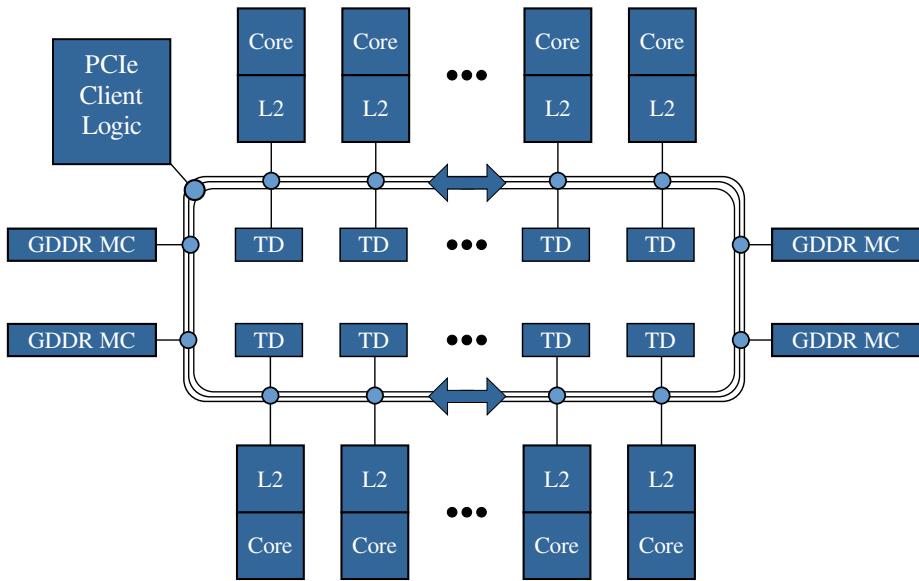

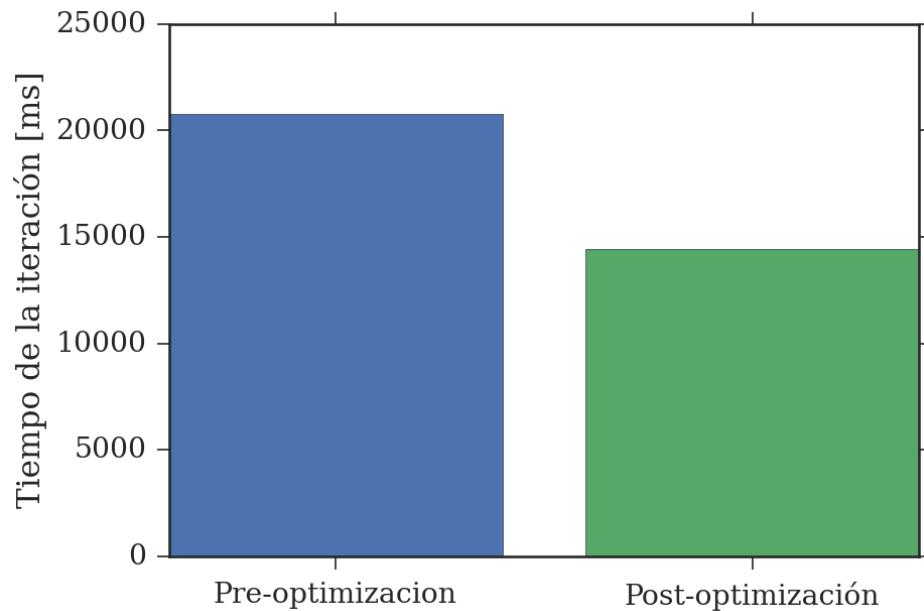

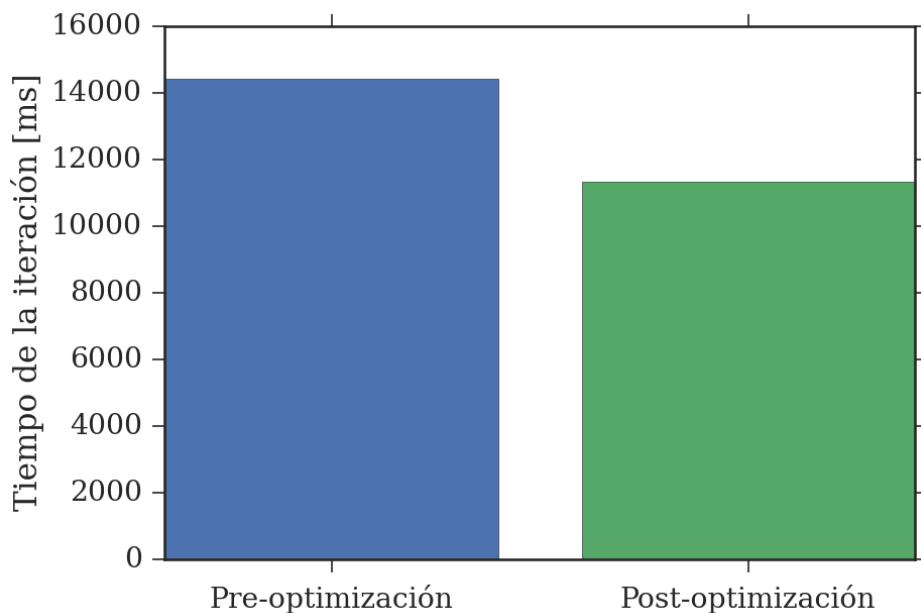

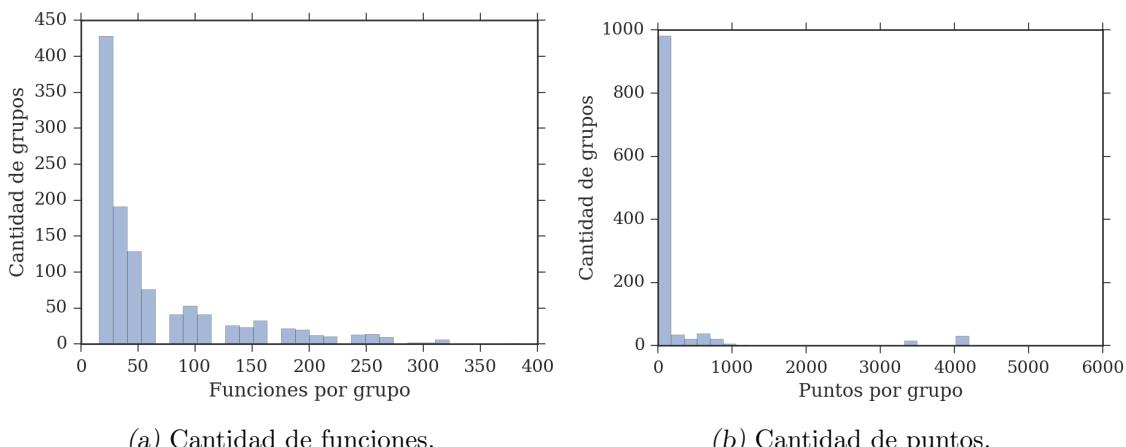

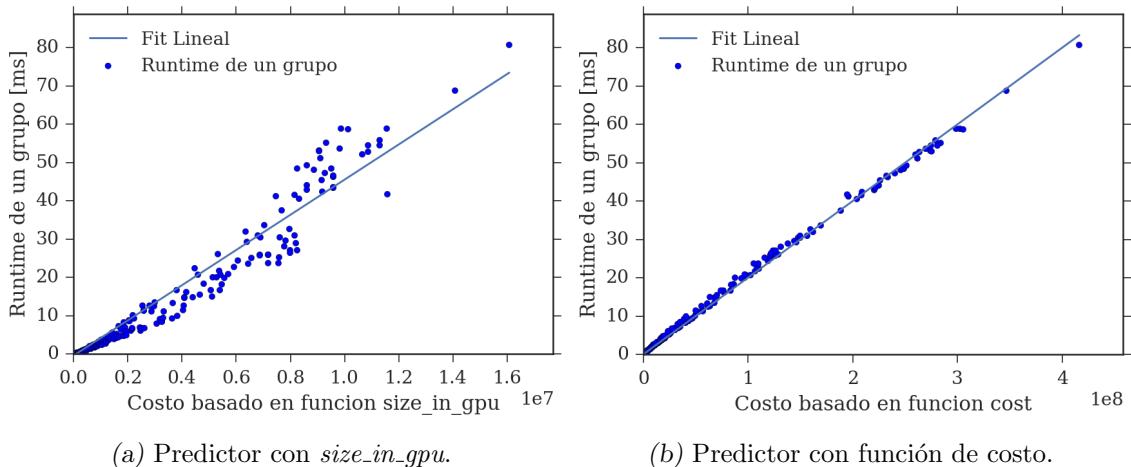

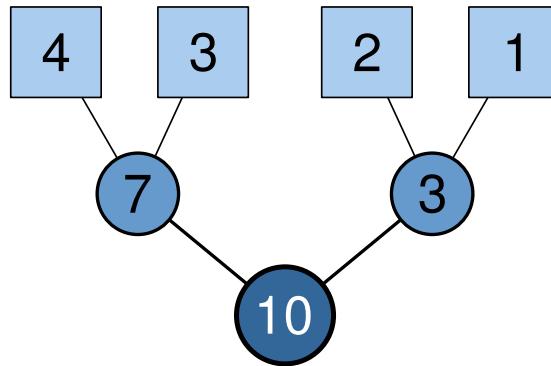

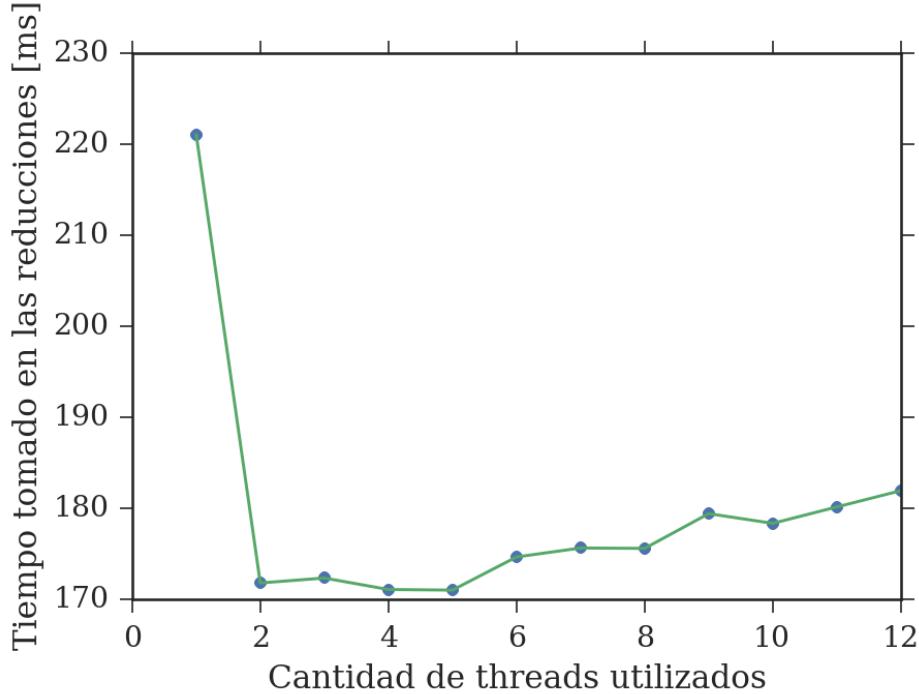

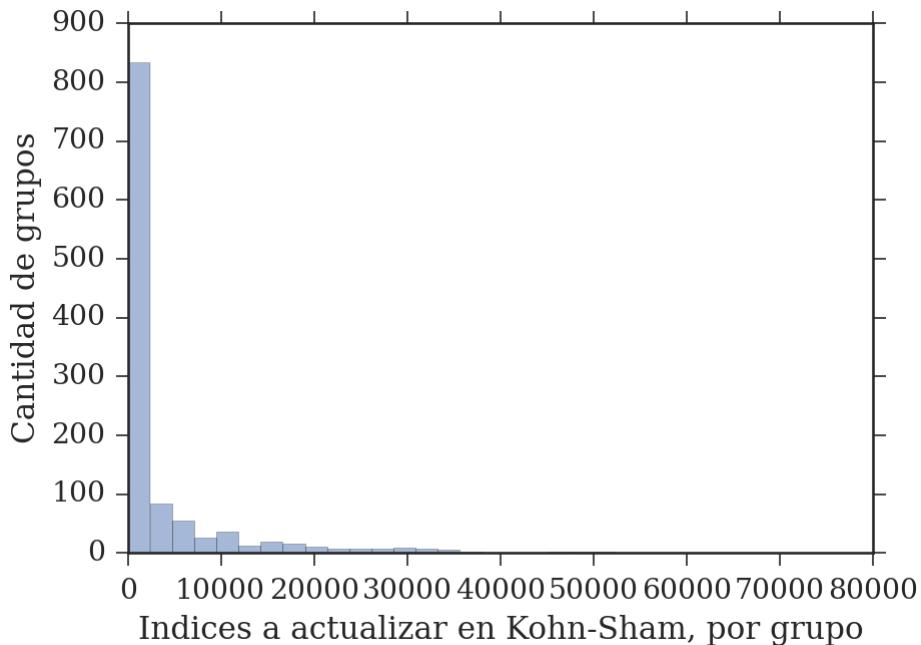

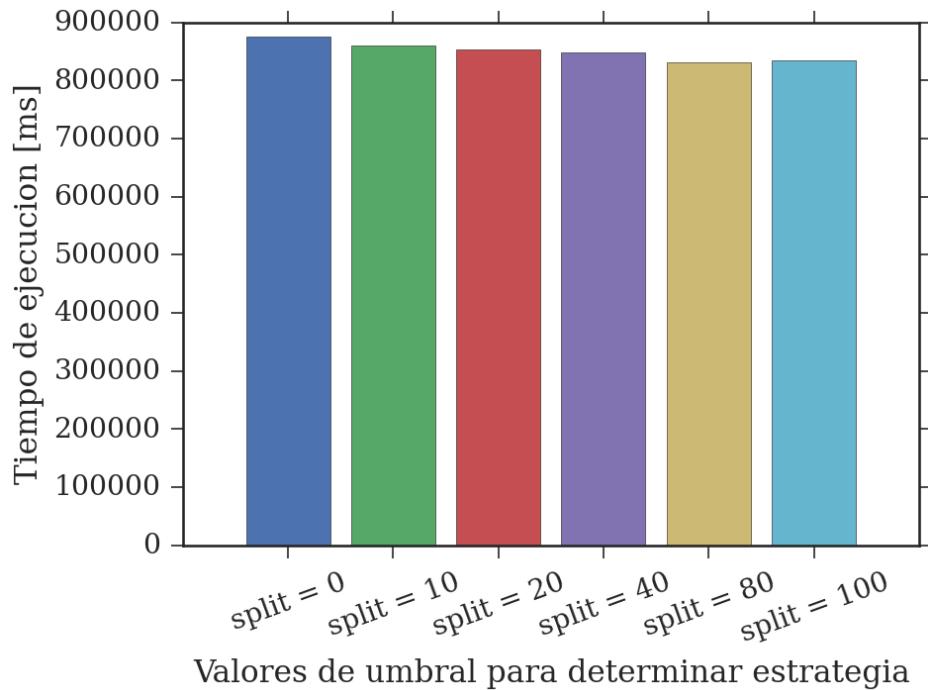

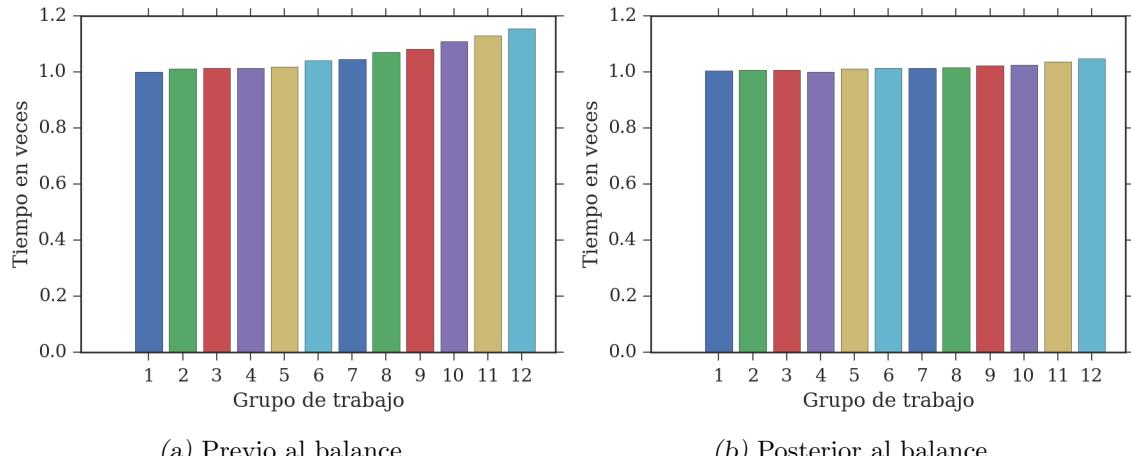

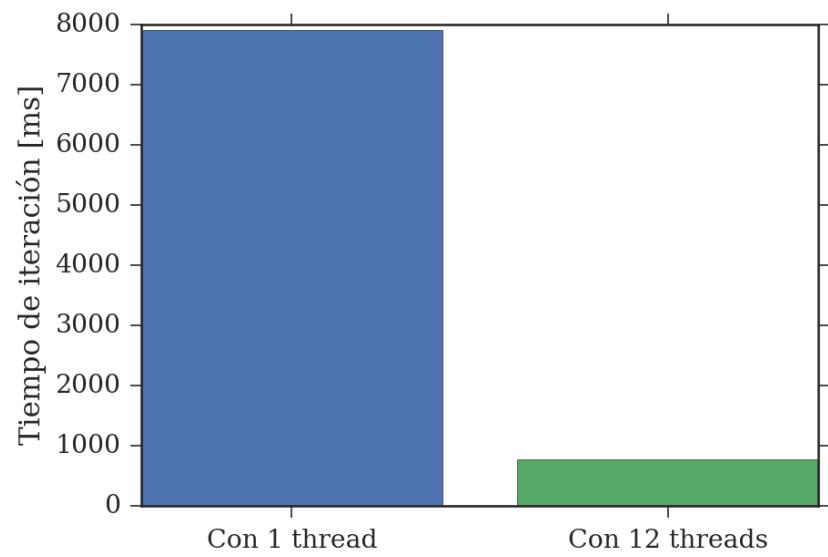

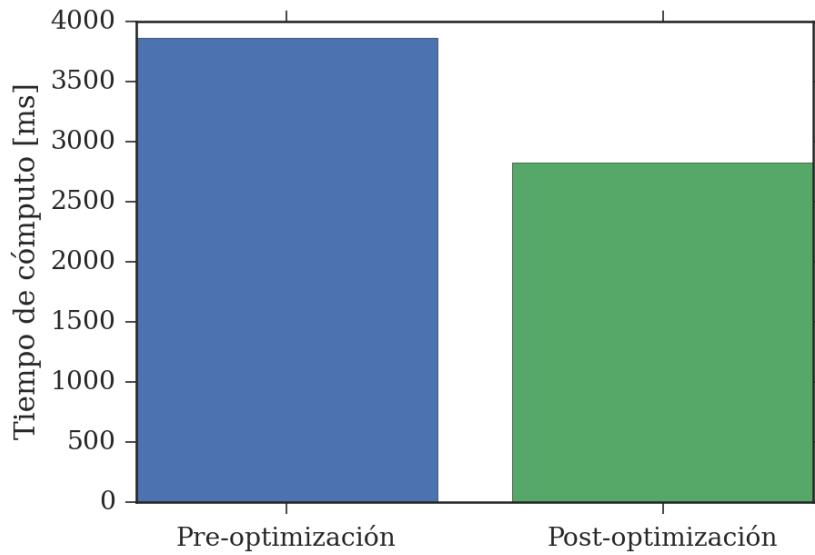

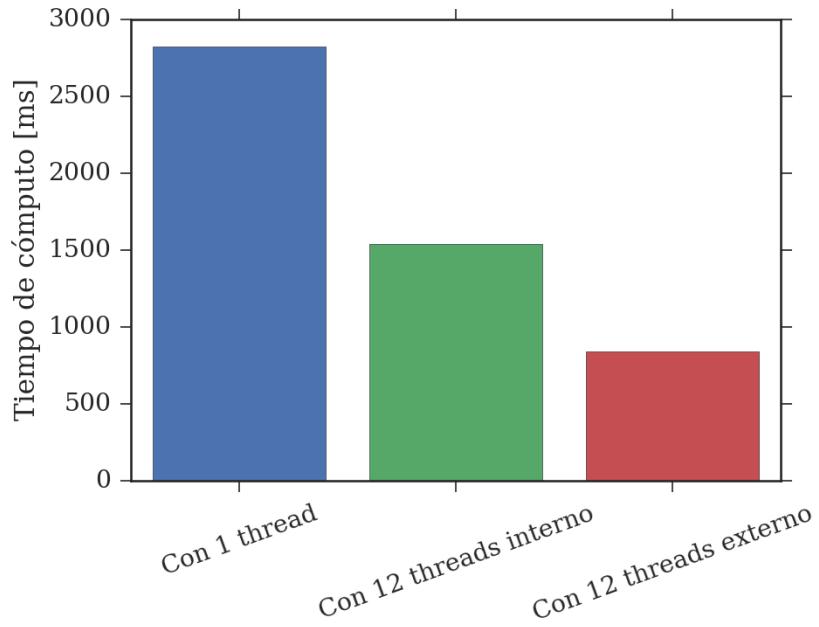

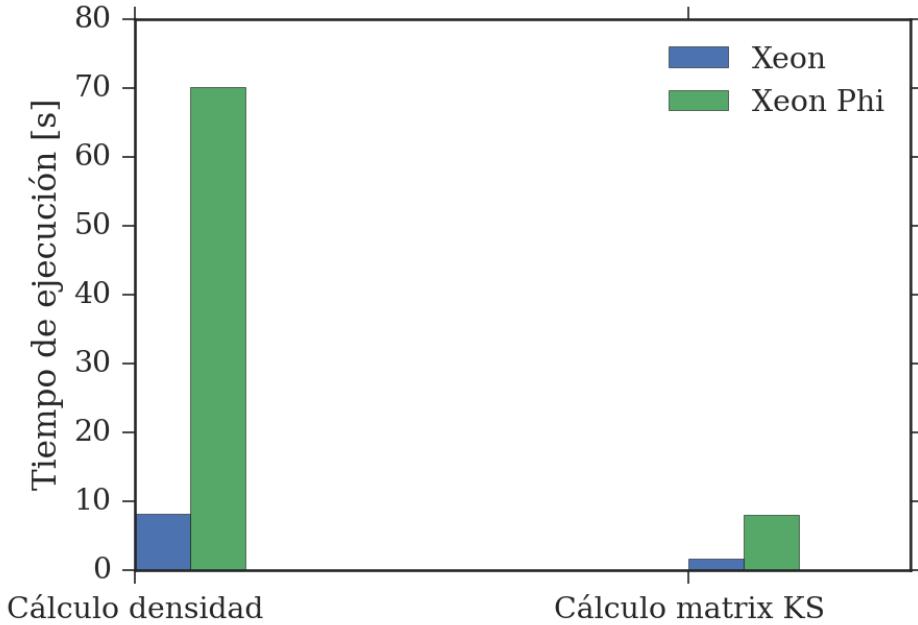

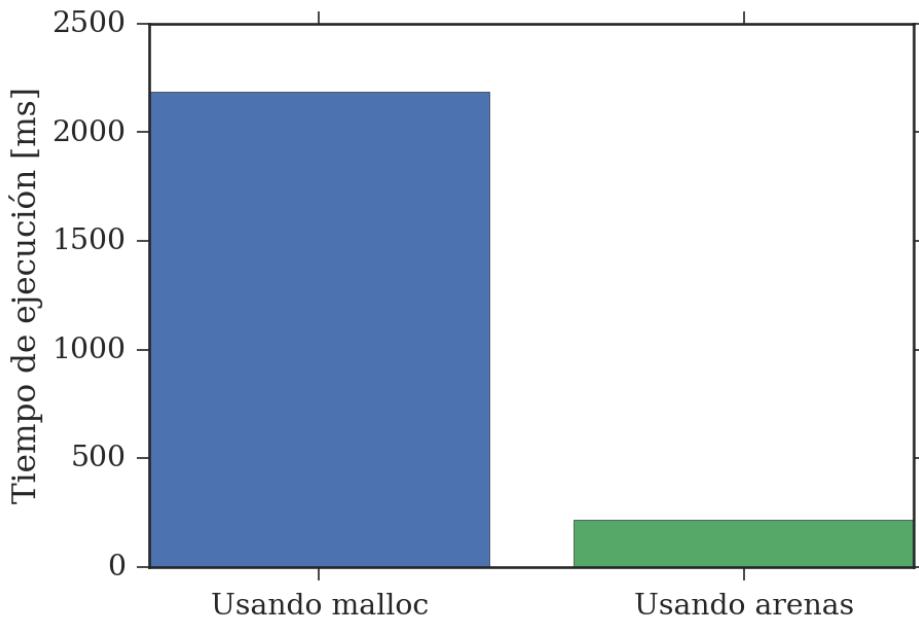

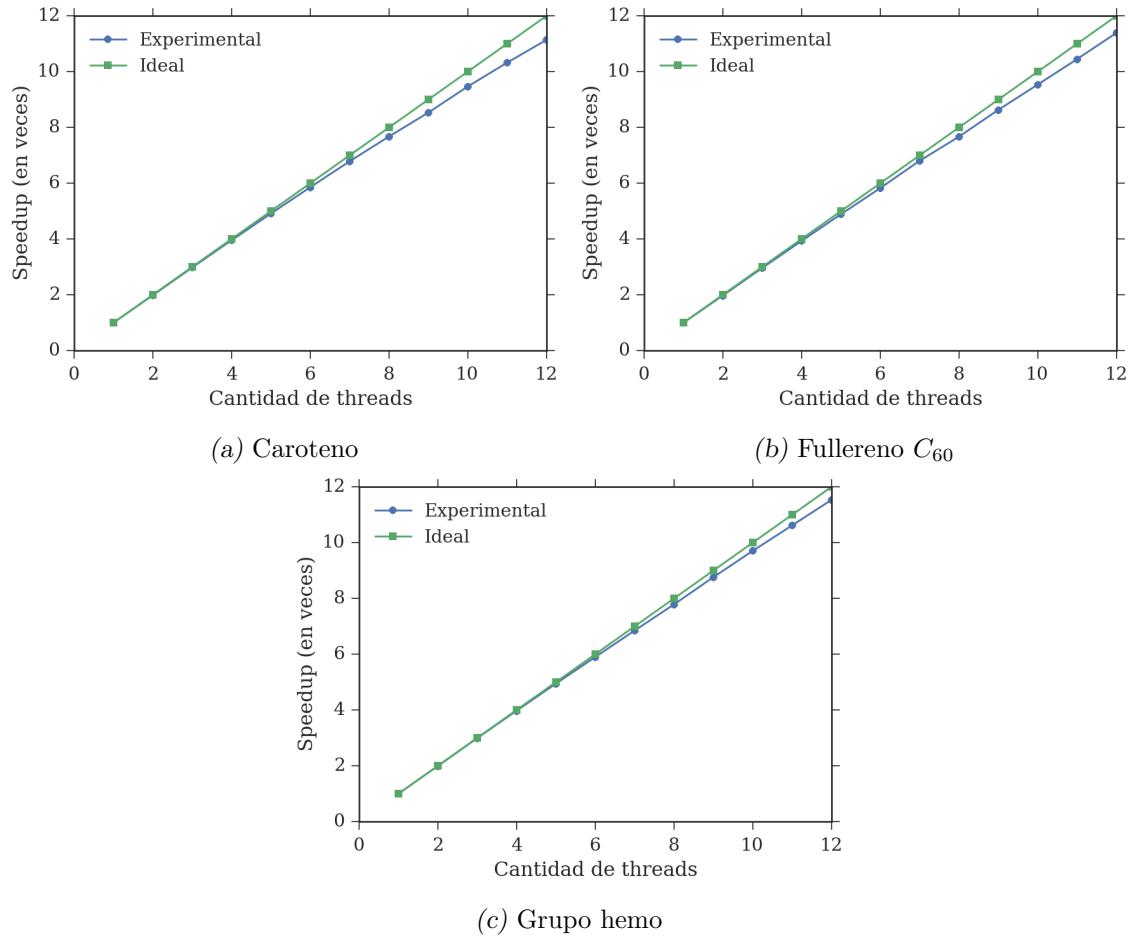

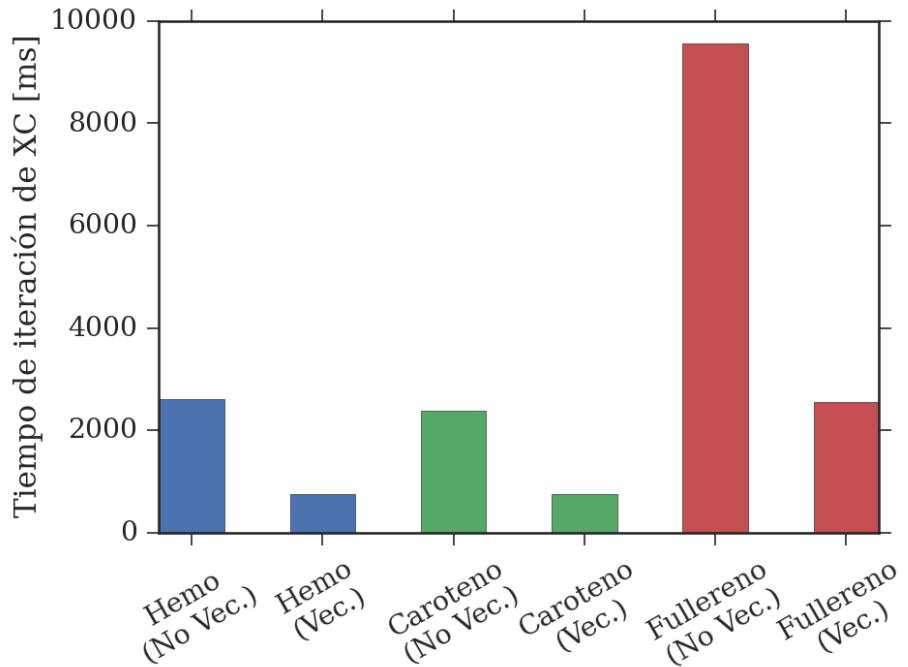

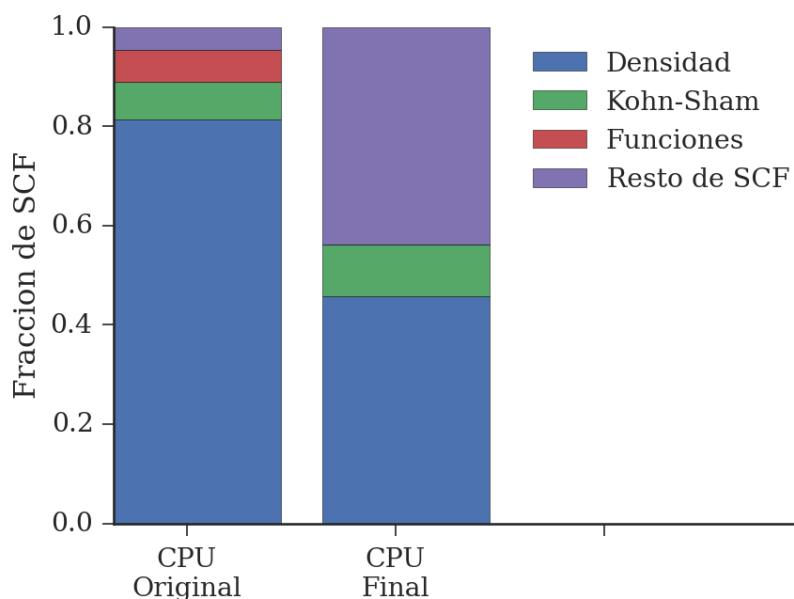

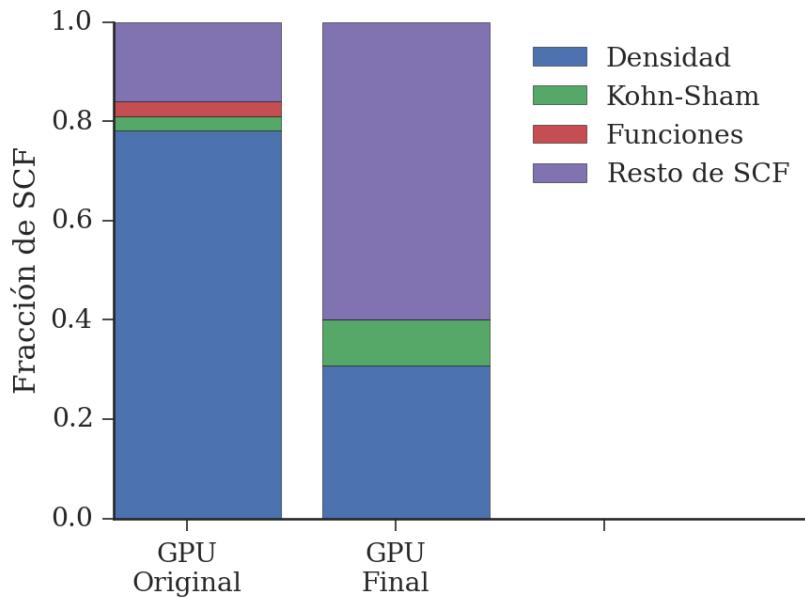

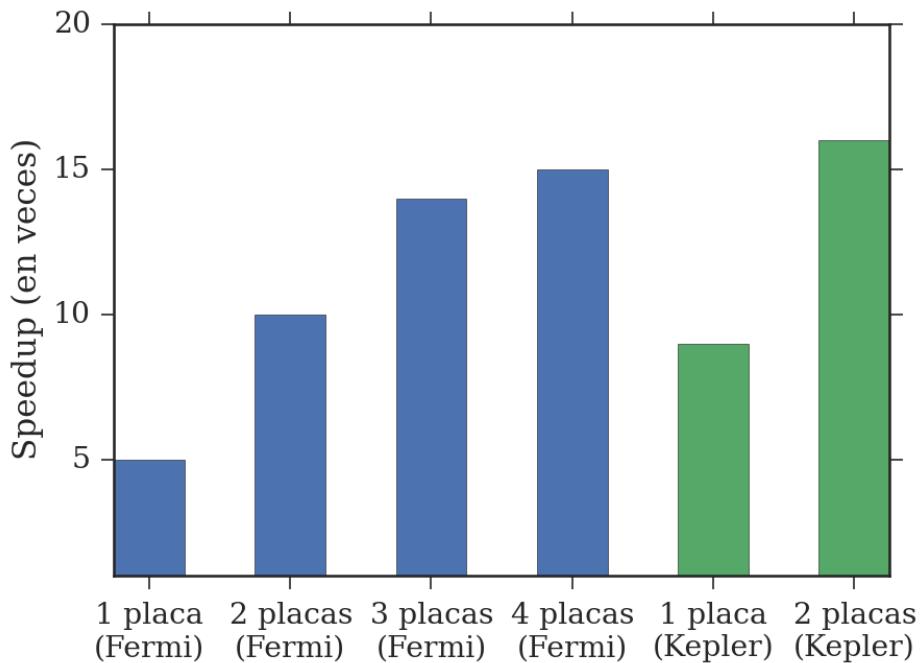

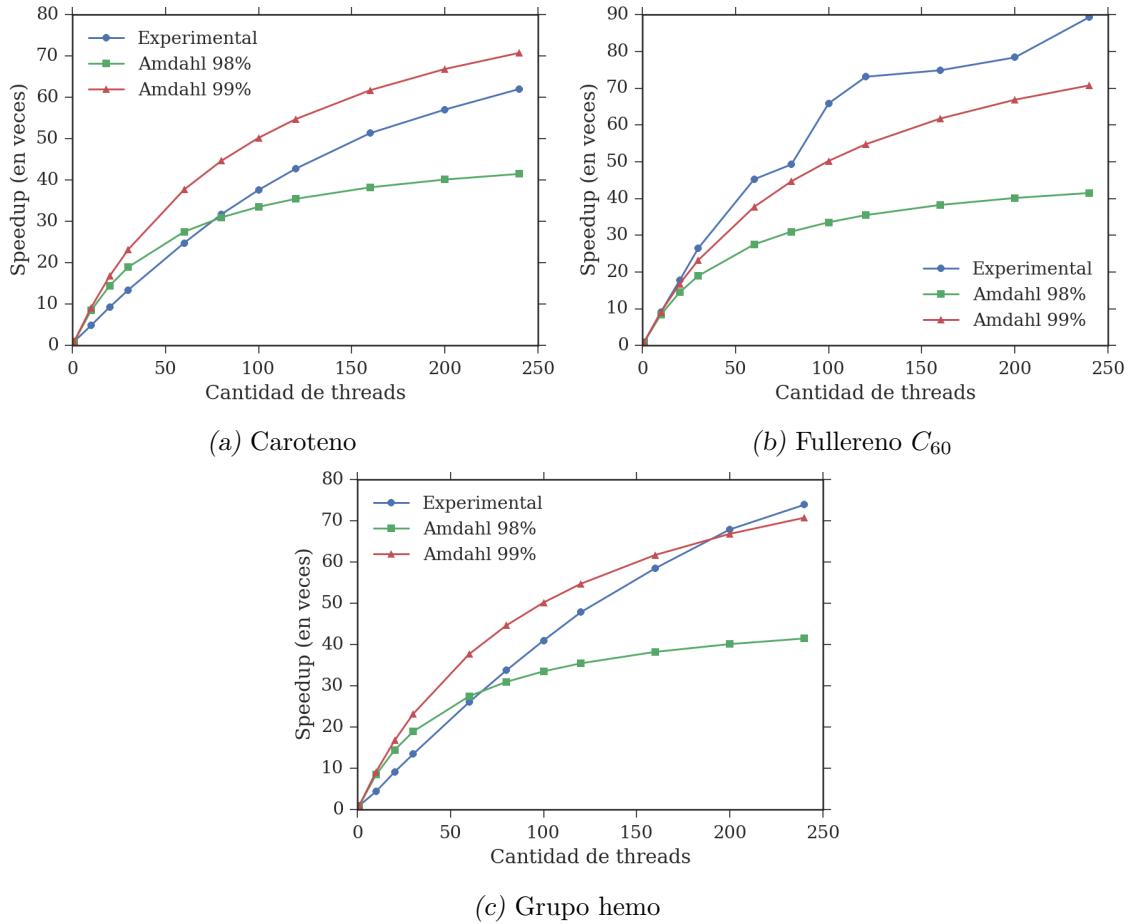

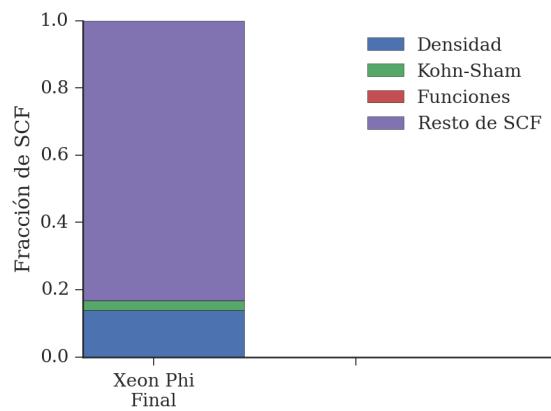

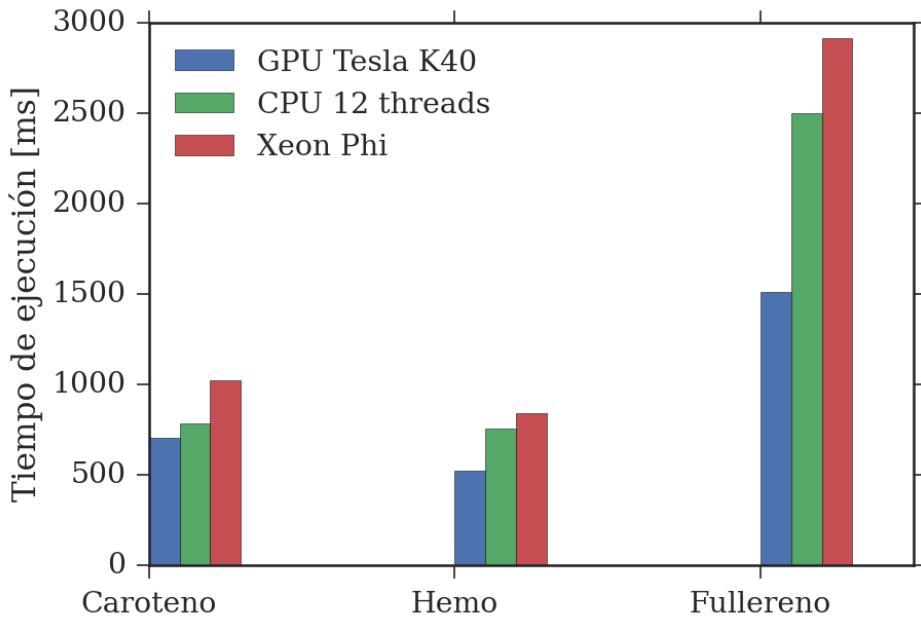

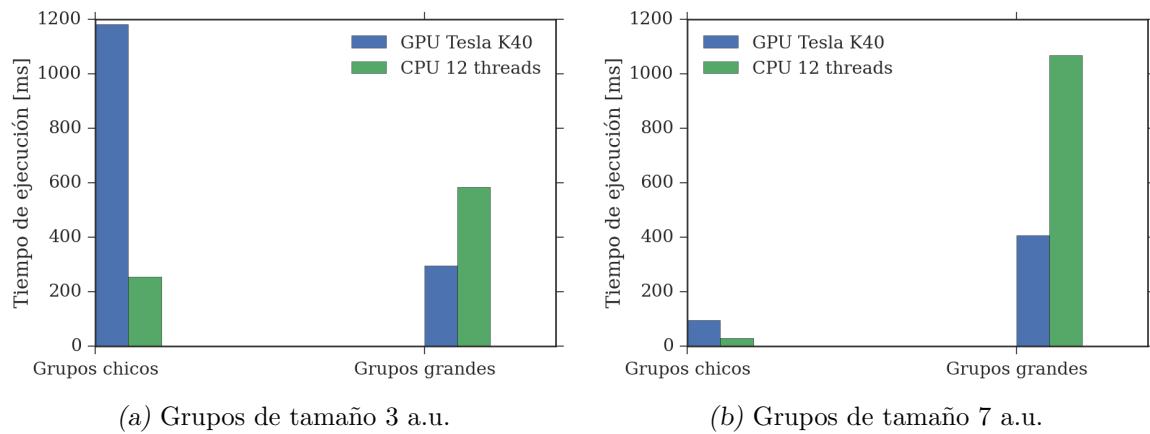

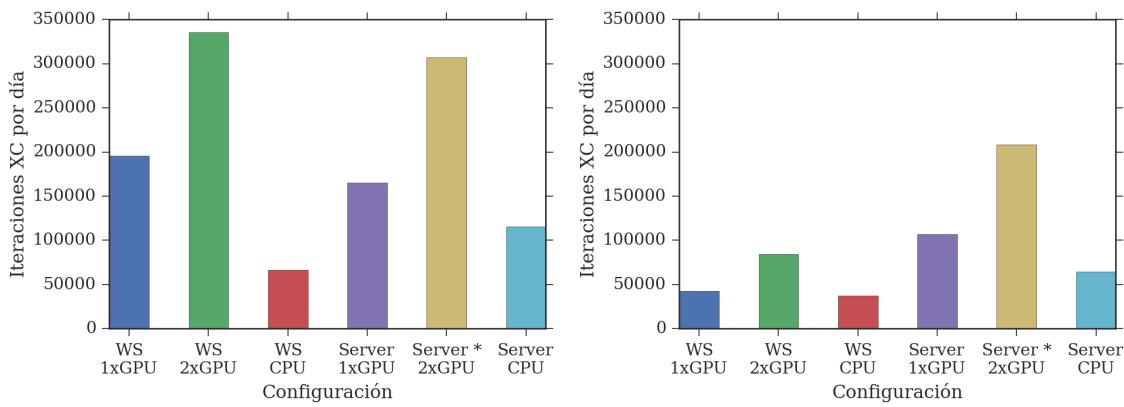

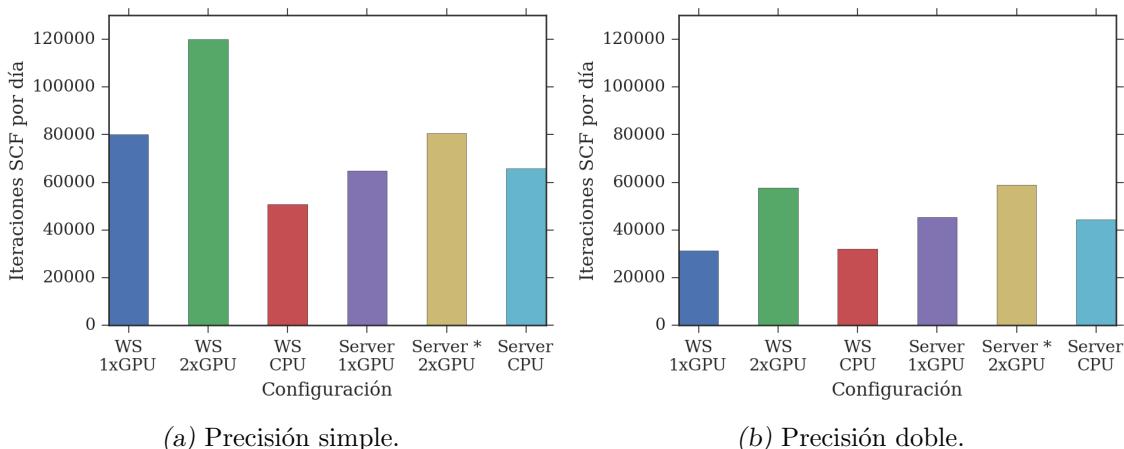

### 2.3.2. Microarquitectura general