UNIVERSIDAD DE BUENOS AIRES

FACULTAD DE CIENCIAS EXACTAS Y NATURALES

DEPARTAMENTO DE COMPUTACIÓN

# Ampliando las capacidades de una aplicación de cómputo QM/MM utilizando GPU

Tesis presentada para optar al título de

Licenciado en Ciencias de la Computación

Eduardo Andrés Perez Leale

Director: Dr. Esteban Mocskos

Codirector: Dr. Mariano Camilo González Lebrero

Buenos Aires, 2019

## RESUMEN

Hoy en día, la simulación numérica es una disciplina fundamental dentro de una gran cantidad de áreas de la ciencia y la tecnología. El uso de estas técnicas permite validar modelos teóricos así como también brindar información detallada (macro y microscópica) del proceso simulado, complementando el uso de las técnicas experimentales tradicionales. Este trabajo se enfoca en modificar el software de estructura electrónica LIO. Este código se basa en la teoría de los funcionales de la densidad (DFT) y permite estimar propiedades de sistemas moleculares de manera muy eficiente mediante el empleo de tarjetas gráficas (GPUs) en las partes más demandantes del cálculo. En el esquema de DFT la calidad (así cómo el mayor costo) está dada por el cálculo de lo que se llama “energía de intercambio y correlación”(EXC), por ello LIO realiza los calculos asociados a estos terminos en GPU. Para el cálculo de EXC existen múltiples “recetas” (llamadas funcionales de intercambio y correlación) que pueden ser convenientes para el tratamiento de diferentes sistemas o propiedades. La versión original de LIO incluía un único funcional (llamado PBE) lo que limitaba sus capacidades.

**Libxc** es una biblioteca de funcionales de intercambio y correlación para DFT diseñada para realizar simulaciones utilizando únicamente procesadores generales por lo que su implementación en GPU puede no resultar eficiente.

El desafío planteado en esta tesis es lograr utilizar **Libxc** desde LIO sin que impacte en su performance. Para lograrlo se realizaron los siguientes pasos:

1. Se integró LIO con **Libxc** sin modificar la estructura general de **Libxc** para poder realizar simulaciones con mayor diversidad de funcionales.

2. Se seleccionó un subconjunto de funcionales de **Libxc** y se realizó su implementación en GPU, para lo cual se realizó una modificación en la arquitectura y los algoritmos de **Libxc**. Se comenzó por el funcional PBE para poder validar el correcto funcionamiento de la aplicación. Luego, se implementó el resto de los funcionales seleccionados y se obtuvo una versión de LIO integrada con **Libxc** para GPU.

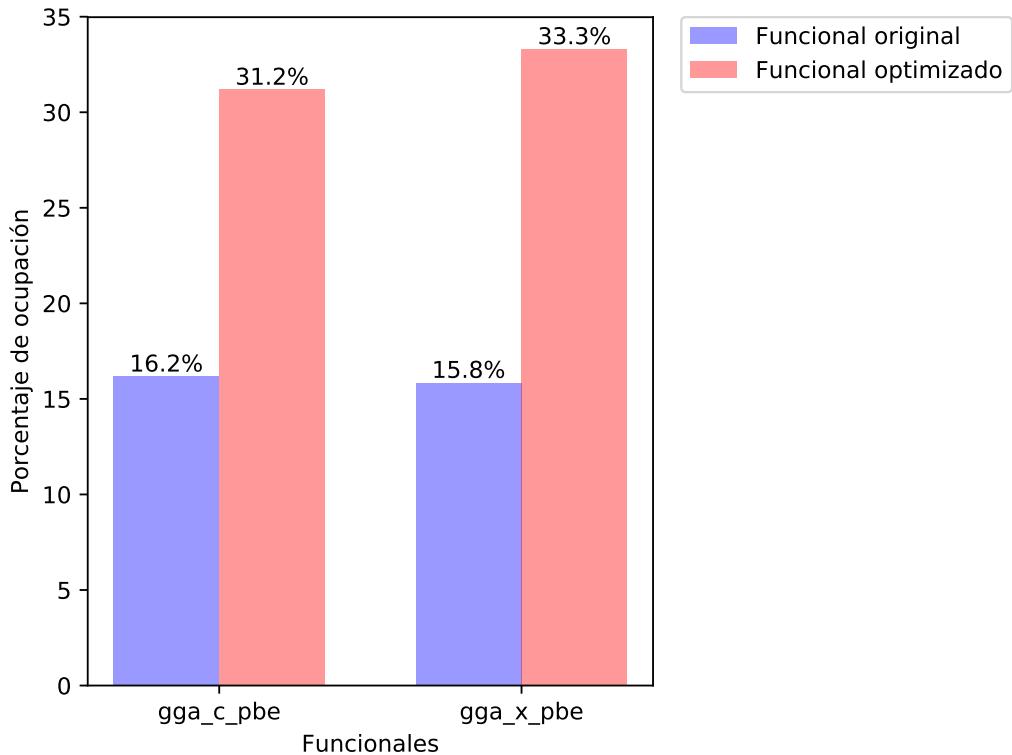

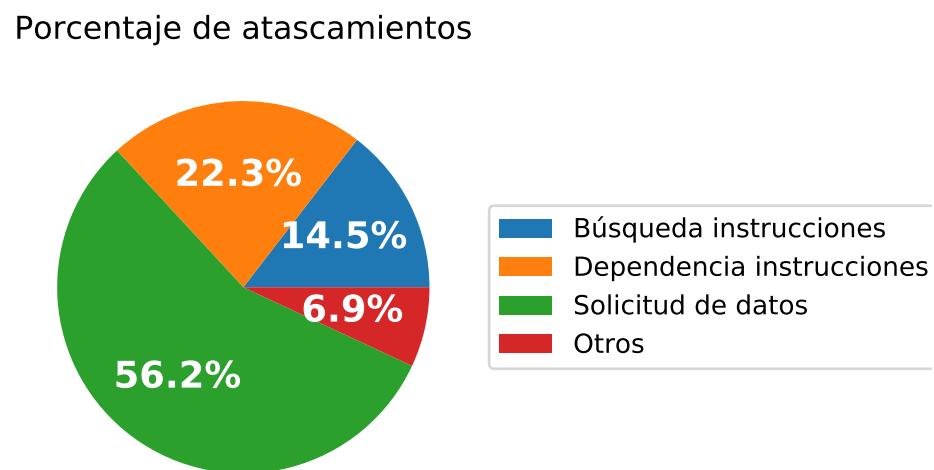

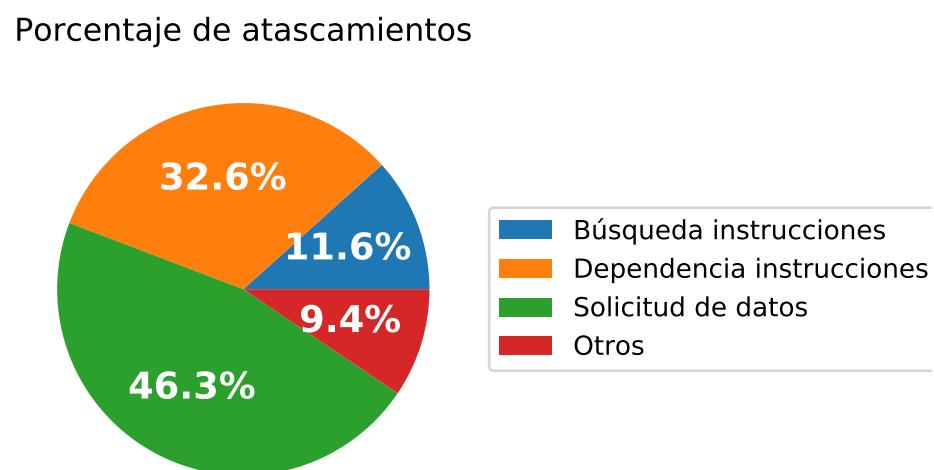

3. Se analizó el uso de los recursos de la tarjetas gráficas con el fin de poder aprovechar al máximo la arquitectura de las GPUs. Se buscó cambiar la estrategia de paralelización en la estructura del cómputo de **Libxc** para aprovechar la mayor cantidad de memoria que poseen las tarjetas gráficas para almacenar más resultados intermedios.

4. Se exploró el uso de diversos compiladores provistos por el proyecto LLVM en un intento de realizar una traducción automática del código fuente de la biblioteca **Libxc** para GPUS.

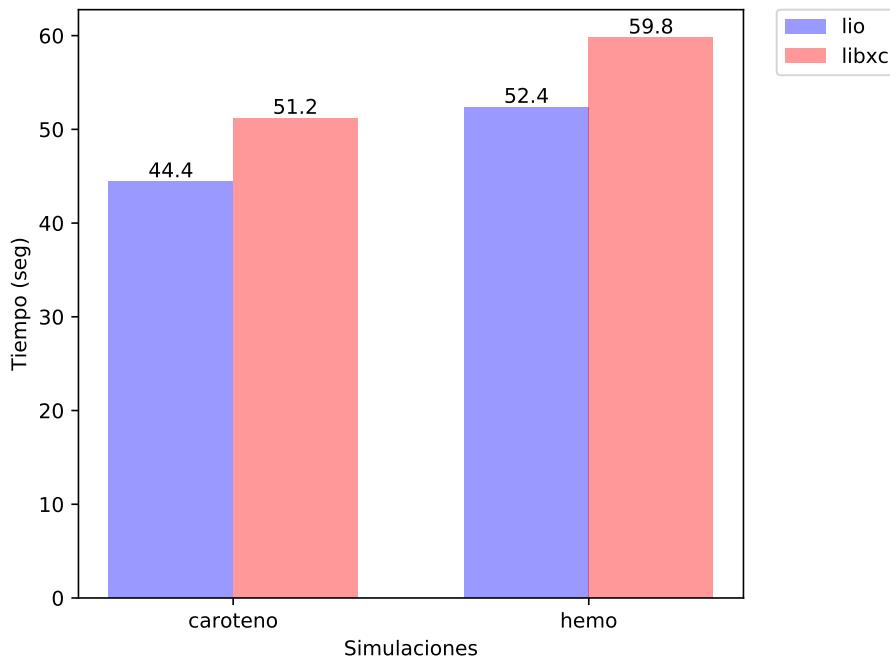

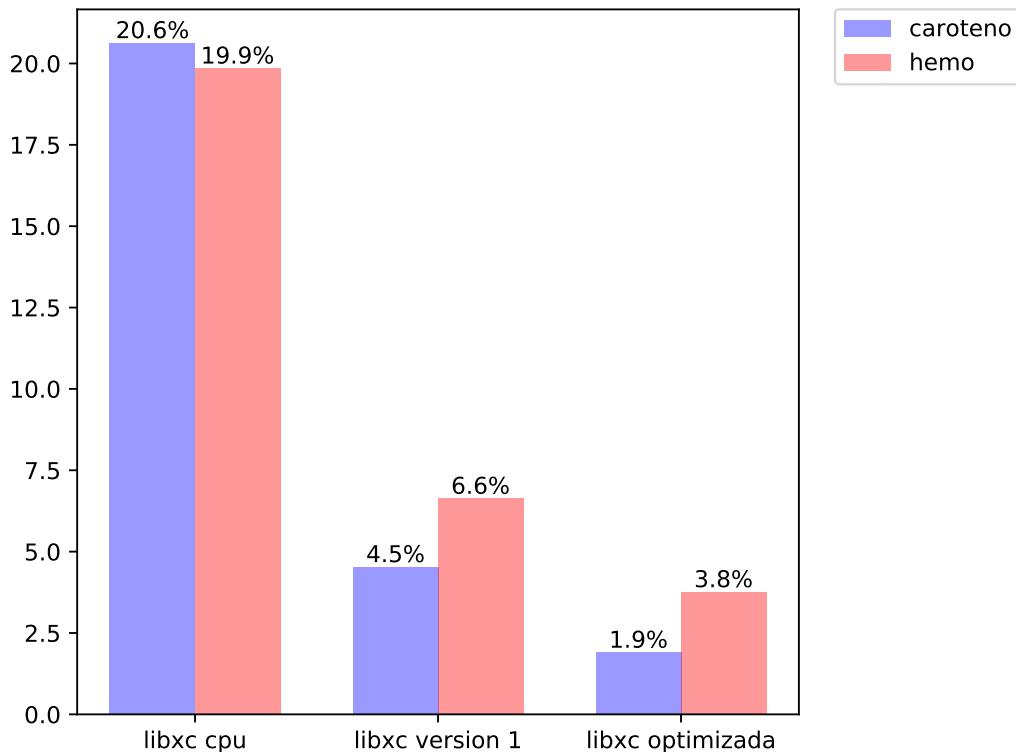

Como resultado de este trabajo se pudo lograr una ampliación de las capacidades del cómputo del software LIO al vincularlo con la biblioteca **Libxc** con un impacto menor en la performance que va de 19 % en la primer etapa, al 4 % en la etapa final. También se lograron identificar los puntos clave en la implementación que permitirían continuar con las tareas de optimización. Las mejoras permiten que LIO pueda ser utilizada con una amplia gamma de algoritmos que realizan los cálculos de intercambio de energía y correlación lo que consecuentemente permite realizar simulaciones en condiciones más variadas.

Como corolario de este trabajo se pudo estandarizar (aunque no automatizar) un procedimiento que permite realizar una traducción de los funcionales de **Libxc** para que puedan ser ejecutados en GPU.

**Palabras claves:** QM/MM, DFT, LIO, **Libxc**, GPGPU, CUDA, LLVM, *scheduling*.

## Índice general

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 1.. Introducción . . . . .                                                | 1  |

| 1.1. Modelos cuánticos (QM) . . . . .                                     | 1  |

| 1.2. Libxc . . . . .                                                      | 4  |

| 2.. Arquitecturas en profundidad . . . . .                                | 5  |

| 2.1. GPGPU con CUDA . . . . .                                             | 5  |

| 2.1.1. Organización de procesadores . . . . .                             | 6  |

| 2.1.2. Organización de la memoria . . . . .                               | 9  |

| 2.1.3. Esquema de paralelismo . . . . .                                   | 11 |

| 2.1.4. Arquitectura Kepler . . . . .                                      | 12 |

| 2.1.5. Arquitectura Maxwell . . . . .                                     | 15 |

| 2.1.6. Arquitectura Pascal . . . . .                                      | 17 |

| 2.1.7. Diferencias entre Tesla, Fermi, Kepler, Maxwell y Pascal . . . . . | 18 |

| 2.1.8. CUDA, Herramientas de desarrollo, profiling, exploración . . . . . | 18 |

| 2.1.9. Requerimientos de un problema para GPGPU . . . . .                 | 19 |

| 2.1.10. Diferencia entre CPU y GPU, procesadores especulativos . . . . .  | 20 |

| 2.1.11. Idoneidad para la tarea . . . . .                                 | 21 |

| 3.. Herramientas . . . . .                                                | 23 |

| 3.1. Herramientas . . . . .                                               | 23 |

| 3.1.1. LLVM . . . . .                                                     | 23 |

| 3.1.2. Clang . . . . .                                                    | 25 |

| 3.1.3. LLC . . . . .                                                      | 26 |

| 4.. Implementación . . . . .                                              | 27 |

| 4.1. Implementación existente . . . . .                                   | 27 |

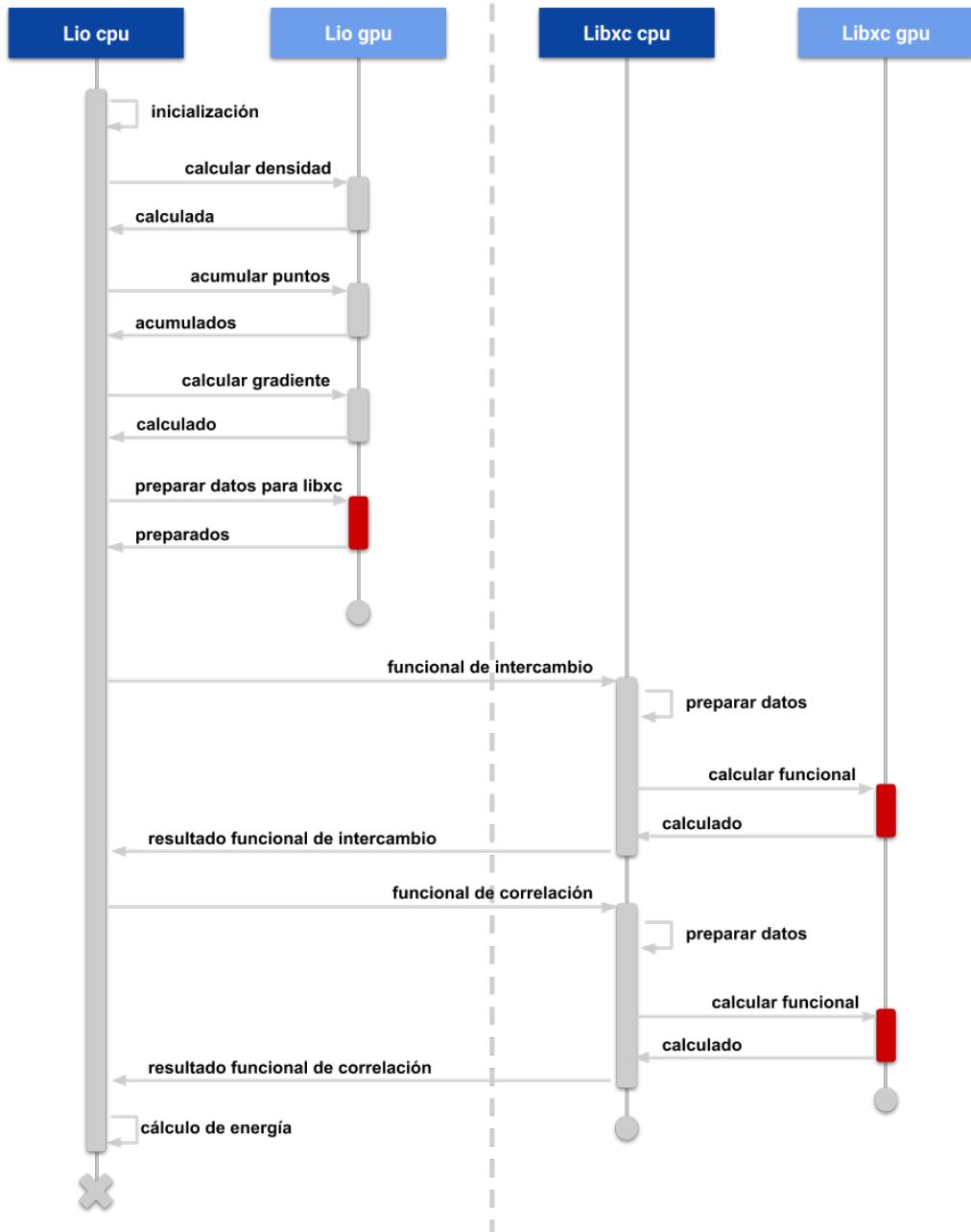

| 4.2. Integración LIO - Libxc versión cpu . . . . .                        | 29 |

| 4.2.1. Estructura original del código LIO . . . . .                       | 30 |

| 4.2.2. Cálculo de energía modificado . . . . .                            | 30 |

| 4.3. Traducción de Libxc a CUDA . . . . .                                 | 31 |

| 4.3.1. Arquitectura de Libxc . . . . .                                    | 32 |

| 4.4. Integración LIO - Libxc versión GPU . . . . .                        | 34 |

| 4.4.1. Arquitectura de la solución . . . . .                              | 34 |

| 4.4.2. Modificaciones a los componentes . . . . .                         | 35 |

| 4.4.3. Precisión numérica . . . . .                                       | 35 |

| 4.5. Resultados preliminares . . . . .                                    | 36 |

| 4.6. Optimizaciones a Libxc . . . . .                                     | 38 |

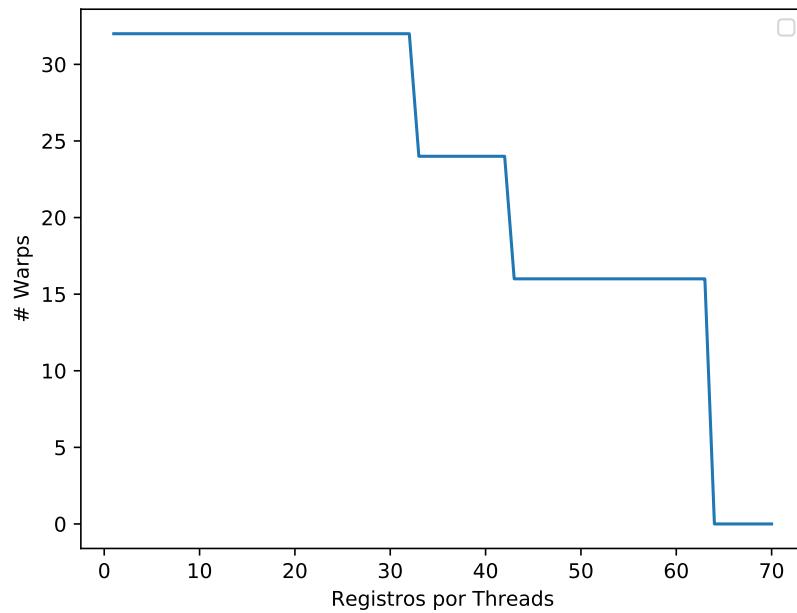

| 4.6.1. Detectando cuellos de botella . . . . .                            | 38 |

| 4.6.2. Posibles causas de los cuellos de botella . . . . .                | 40 |

| 4.6.3. Buscando soluciones a los cuellos de botella . . . . .             | 44 |

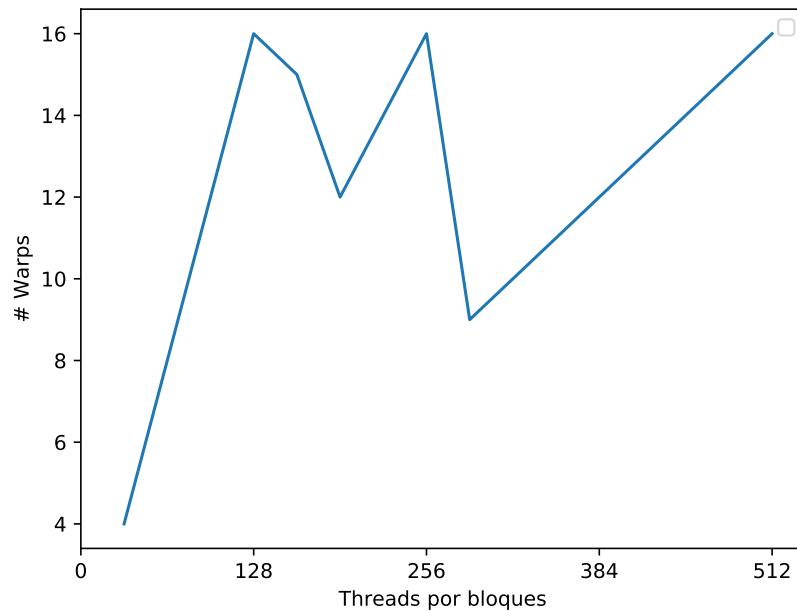

| 4.6.4. Variando la cantidad de threads . . . . .                          | 44 |

| 4.6.5. Deep profiling . . . . .                                           | 46 |

| 4.6.6. Modificando la forma de compilación . . . . .                      | 53 |

|                                                                                        |    |

|----------------------------------------------------------------------------------------|----|

| 4.7. Completando la traducción . . . . .                                               | 56 |

| 5.. Resultados . . . . .                                                               | 57 |

| 5.1. Tiempos de ejecución de las simulaciones . . . . .                                | 57 |

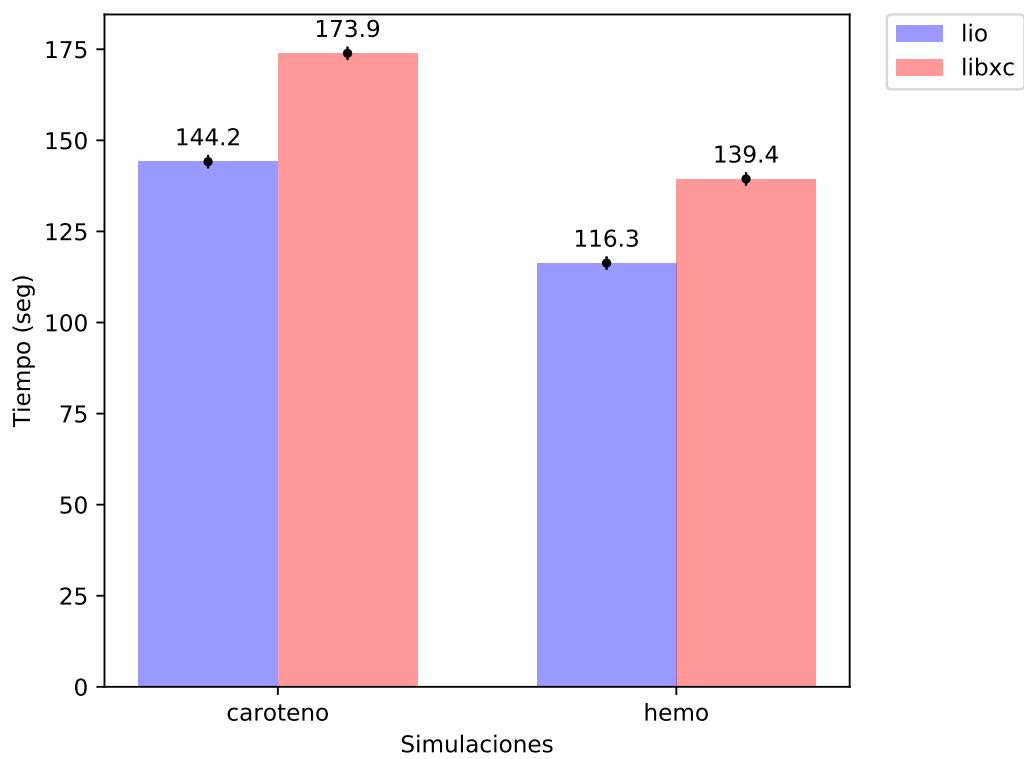

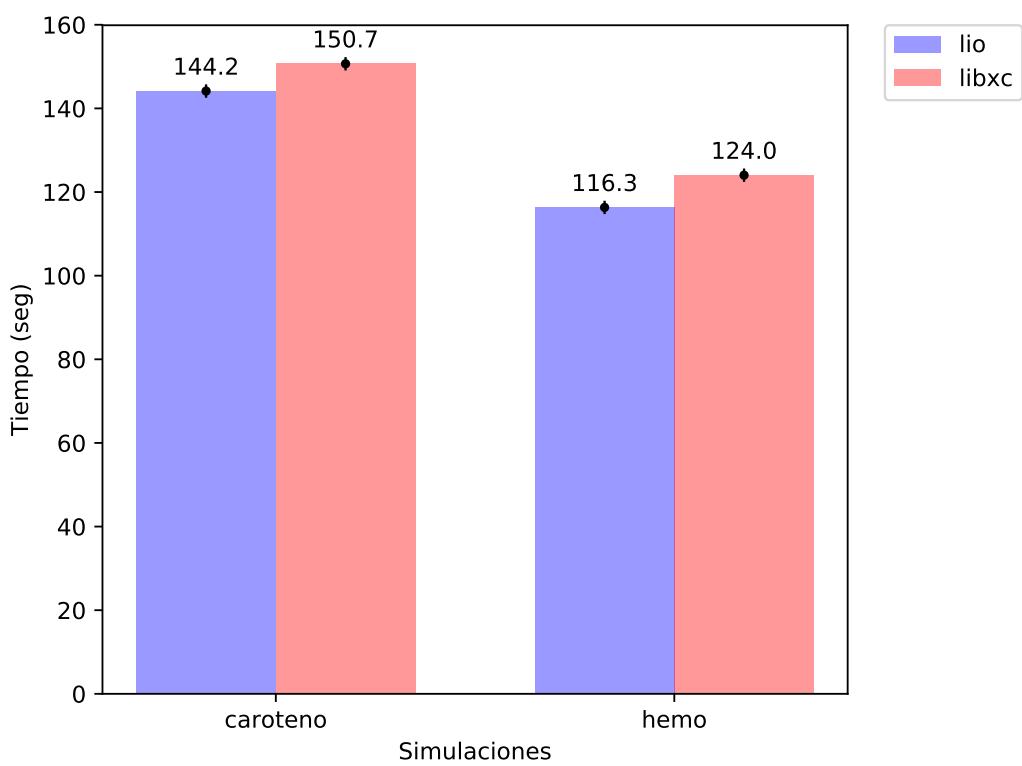

| 5.1.1. Resultados obtenidos utilizando la versión original de Libxc . . . . .          | 57 |

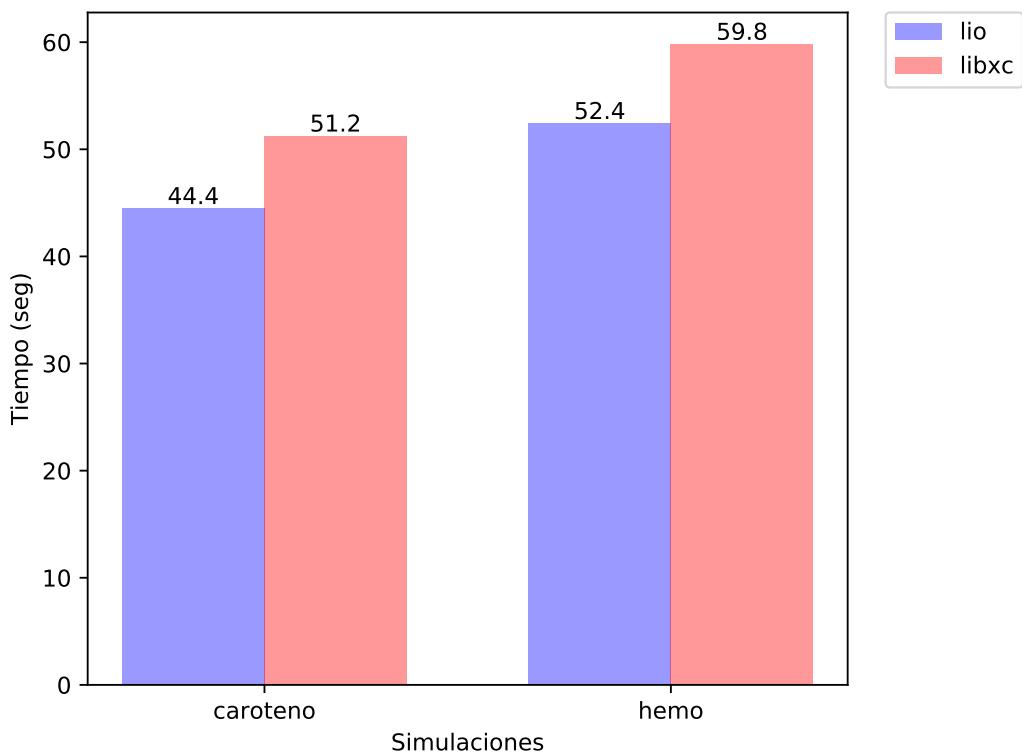

| 5.1.2. Resultados obtenidos utilizando la primera versión de Libxc en GPU              | 57 |

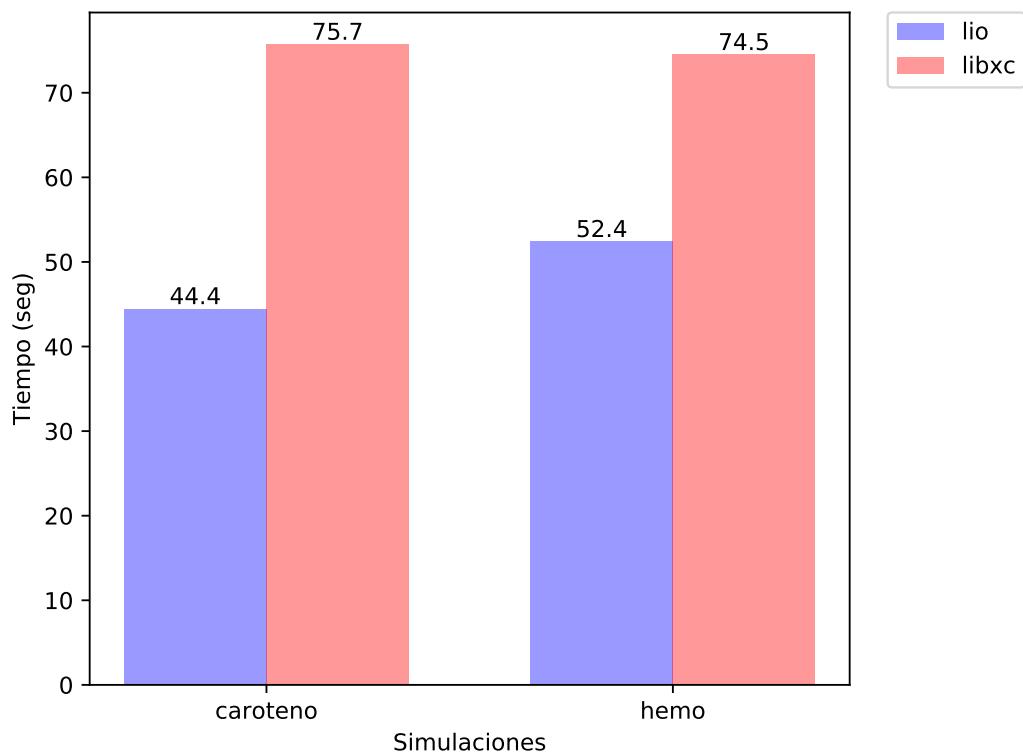

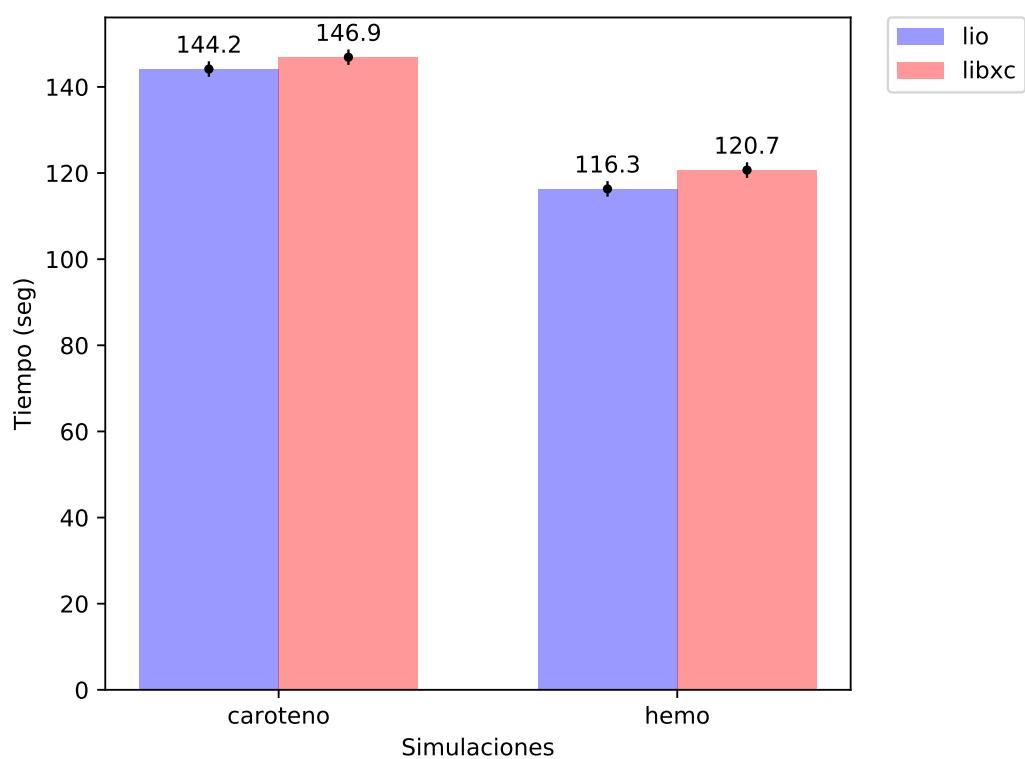

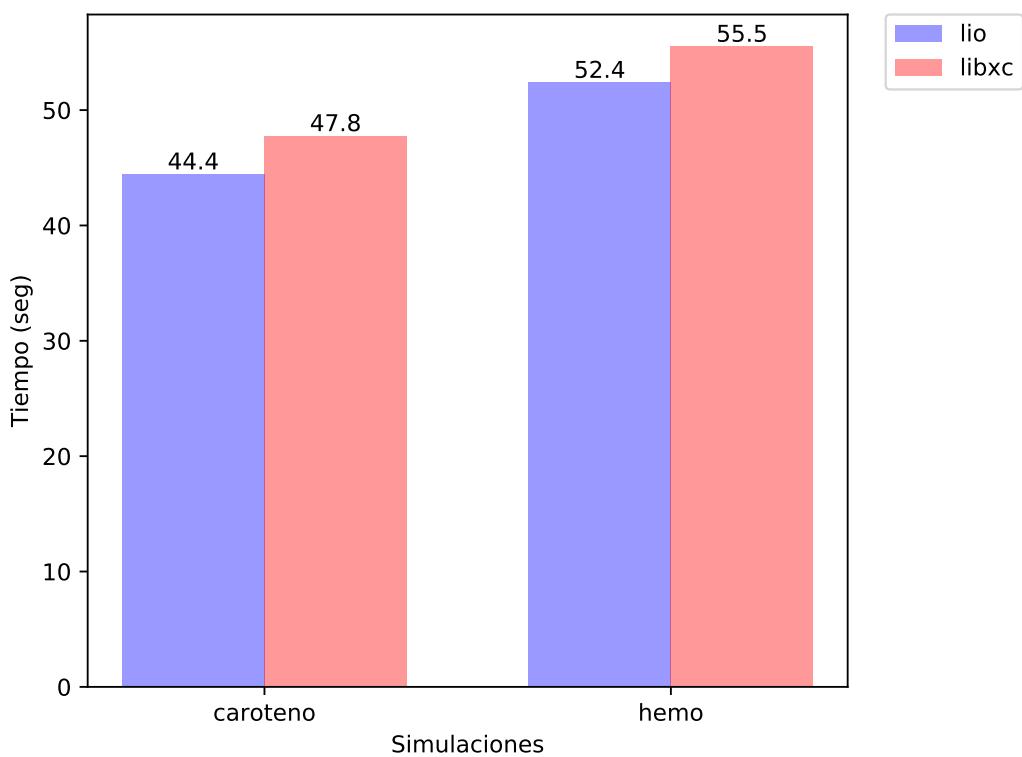

| 5.1.3. Resultados obtenidos utilizando la versión optimizada de Libxc en GPU . . . . . | 62 |

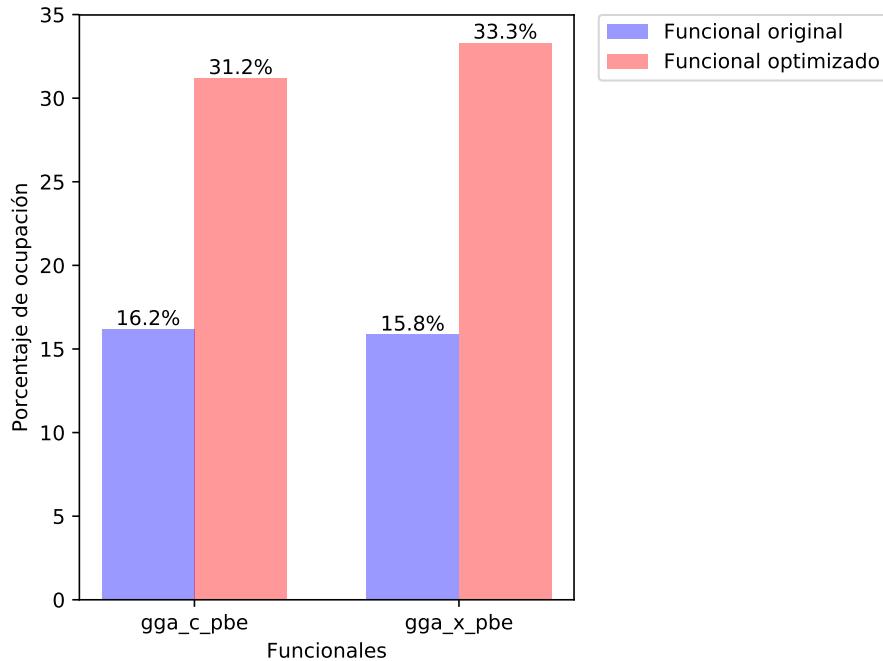

| 5.2. Ocupación de bloques de memoria . . . . .                                         | 66 |

| 5.3. Atascamientos (stalls) . . . . .                                                  | 66 |

| 5.4. Configuración de memoria cache . . . . .                                          | 68 |

| 5.5. Estructuras de datos alineadas en memoria . . . . .                               | 68 |

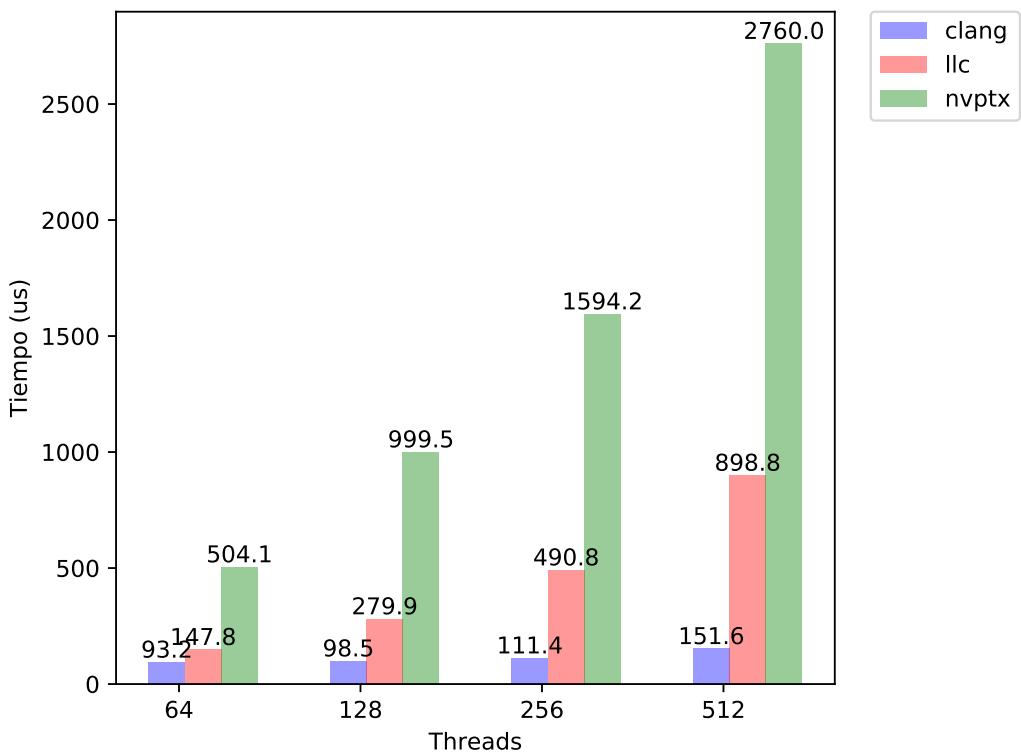

| 5.6. Otros compiladores . . . . .                                                      | 69 |

| 5.7. Calidad numérica de los resultados . . . . .                                      | 69 |

| 6.. Conclusiones . . . . .                                                             | 71 |

| Apéndice                                                                               | 77 |

| A.. Equipamiento usado para correr las pruebas . . . . .                               | 79 |

| B.. Descripción de modelos químicos probados . . . . .                                 | 81 |

| C.. Cantidad de variables de los funcionales de Libxc . . . . .                        | 83 |

| D.. Tiempos de ejecución de los funcionales . . . . .                                  | 87 |

| E.. Opciones de compilación . . . . .                                                  | 89 |

# 1. INTRODUCCIÓN

Hoy en día, la simulación numérica es una disciplina fundamental dentro de una gran cantidad de áreas de desarrollo científico y tecnológico. El uso de estas técnicas permite validar modelos teóricos así como también brindar información detallada (macro y microscópica) del proceso simulado, complementando el uso de las técnicas experimentales tradicionales.

En el ámbito de la química existen diferentes metodologías que permiten simular procesos de interés. Hay dos que se destacan por su uso:

- i) Los métodos basados en la mecánica cuántica, que proporcionan una descripción detallada de la estructura electrónica del sistema.

- ii) Los métodos basados en la mecánica molecular, en los cuales las moléculas son tratadas mediante un campo de fuerza clásico y los electrones no son tenidos en cuenta explícitamente.

## 1.1. Modelos cuánticos (QM)

El comportamiento de los fenómenos a pequeña escala (nanométrica) está regido por las leyes de la mecánica cuántica. Este marco teórico desarrollado a comienzos del siglo XX propone que las partículas (como electrones y protones) pueden (y deben en algunos casos) ser descriptas como ondas. Así, cualquier propiedad de un sistema está determinado por una función llamada *función de onda* ( $\Psi$ ) que satisface la ecuación de Schrödinger dependiente del tiempo:

$$i\hbar \frac{\partial \Psi}{\partial t}(\mathbf{r}, t) = \frac{-\hbar^2}{2m} \nabla^2 \Psi(\mathbf{r}, t) + V(\mathbf{r}, t) \Psi(\mathbf{r}, t) \quad (1.1)$$

donde  $\mathbf{r} = (r_1, \dots, r_n)$  es el vector de todas las posiciones de las partículas del sistema,  $m$  es la masa de la partícula,  $V$  es un potencial que afecta a las partículas y  $\hbar$  es la constante de Planck dividida por  $2\pi$ .

Si el campo externo no depende del tiempo esta ecuación se puede simplificar a la de Schrödinger *independiente del tiempo*:

$$\hat{H}\Psi(\mathbf{r}) = E\Psi(\mathbf{r}) \quad (1.2)$$

donde  $E$  es la energía asociada a la función de onda  $\Psi$  y el operador hamiltoniano  $\hat{H}$  se define como:

$$\hat{H} = -\frac{\hbar^2}{m} \nabla^2 + \hat{V}$$

Ahora, si bien resolver esta ecuación diferencial sería suficiente para determinar todas las propiedades del sistema, no puede hacerse de manera exacta cuando hay más de un electrón en el mismo. Por este motivo, para problemas de mayor tamaño se utilizan aproximaciones para obtener una solución de la ecuación 1.2.

Existen diversos métodos para resolver de forma aproximada esta ecuación con diferente costo computacional y calidad de la respuesta obtenida. Dentro de estos métodos hay

uno que destaca por su excelente relación costo/calidad, el método basado en la *Teoría de los Funcionales de la Densidad* (DFT, Density Functional Theory) desarrollada por Hohenberg y Kohn en 1964.

En este marco teórico, la *densidad electrónica*  $\rho$  que representa la probabilidad de encontrar un electrón en cada región del espacio ocupa un rol destacado. La base de este método consiste en dos teoremas publicados por Hohenberg y Kohn [1]. Estos autores demuestran que  $\rho$  y  $V$  (y por lo tanto  $\psi$ ) se encuentran relacionadas biunívocamente, es decir, que una dada densidad electrónica contiene la misma información que la función de onda. De esta manera, cualquier observable (como la energía) puede ser representado como un funcional de la densidad (de allí el nombre de esta teoría).

Además, propusieron la dependencia de la energía del sistema como funcional de la densidad de la siguiente forma:

$$E[\rho] = T_s[\rho] + V_{ne}[\rho] + \frac{1}{2} \int \int \frac{\rho(\vec{r}_1)\rho(\vec{r}_2)}{r_{12}} d\vec{r}_1 d\vec{r}_2 + E_{XC}[\rho] \quad (1.3)$$

donde  $T_s[\rho]$  es la energía cinética asociada con la densidad,  $V_{ne}[\rho]$  es la energía potencial producto de la interacción entre los electrones (la densidad) y los núcleos, el tercer término es el resultado de la repulsión de Coulomb entre electrones (Electron Repulsion Integral - ERI) y  $E_{XC}[\rho]$  es la energía de intercambio y correlación. Este último término da cuenta de la energía asociada a escribir la función de onda de manera que cumpla con el principio de exclusión de Pauli y de la correlación en la posición instantánea de los electrones.

Esta formulación es exacta si se conociera el término  $E_{XC}[\rho]$  dado que los demás tienen solución analítica. En las aproximaciones hechas para calcularlo reside tanto la calidad como el costo computacional de este tipo de simulaciones. Uno de los puntos principales en los cuales se han centrado diversos trabajos, consiste en disminuir el tiempo insumido en el cómputo del término  $E_{XC}[\rho]$  [2].

La forma comúnmente utilizada para calcular este término se basa en definir un funcional local  $\epsilon_{XC}$  que depende de la densidad (*Local Density Aproximation*, LDA) o de la densidad y su gradiente (*General Gradient Approximation*, GGA) en cada punto del espacio.

De esta manera se puede calcular  $E_{XC}$  mediante la integral:

$$E_{XC} = \int \rho(r) \epsilon_{XC}(\rho(r)) d\vec{r} \quad (1.4)$$

Esta ecuación puede ser aproximada mediante una suma utilizando una grilla de  $j$  puntos, con pesos  $\omega_j$  según:

$$E_{XC} \approx \sum_j \omega_j \rho(r_j) \epsilon_{XC}(\rho(r_j)) \quad (1.5)$$

Otro aspecto importante de esta teoría es que provee una manera de calcular la densidad  $\rho$ , mediante el denominado método de Kohn-Sham [3]. Este método se basa en el segundo teorema de Hohenberg y Kohn, que establece que para cualquier densidad electrónica de prueba  $\rho^*$  que cumpla que  $\int \rho^*(\vec{r}) d\vec{r} = N$ , donde  $N$  es la cantidad de electrones del sistema, vale que:

$$E[\rho^*] \geq E[\rho] \quad (1.6)$$

Esto produce un método auto-consistente para calcular  $\rho$ . Se empieza con una aproximación inicial  $\rho^*$  y se itera el cálculo de la misma hasta alcanzar un mínimo para  $E$ .

Este marco teórico es uno de los métodos más populares en problemas de estado sólido, especialmente desde la década del 90 cuando se mejoraron las aproximaciones para modelado de interacciones. El valor de esta teoría para el estudio de las propiedades de la materia le valió a Kohn el Premio Nobel de Química en 1998.

Si bien la relación costo-calidad de este método es muy buena, el costo computacional asociado sigue siendo elevado, lo que limita su aplicación a sistemas pequeños (cientos de átomos como máximo).

Por este motivo, se han desarrollado los métodos conocidos como *mecánica molecular* (MM). En estos métodos los átomos son tratados como esferas cargadas y las uniones químicas como resortes (potenciales armónicos). De esta manera, los electrones no son considerados explícitamente, reduciendo drásticamente el costo computacional asociado. Esta técnica es muy poderosa para representar sistemas o procesos en los que no cambia la distribución electrónica.

Sin embargo, en muchos de los problemas de interés en química y bioquímica (por ejemplo una reacción química en solución o en el sitio activo de una proteína), el modelado requiere simultáneamente de la representación de miles de átomos y de un tratamiento explícito de los electrones. Para resolver esto, se han desarrollado técnicas híbridas QM/MM (*Quantum Mechanical / Molecular Mechanics*).

Dentro de este esquema se subdivide el sistema en dos partes:

- I) Una parte en la que la estructura electrónica cambia. Se lo modela usando mecánica cuántica (QM).

- II) Para el resto del sistema se aplica un campo de fuerzas clásico (MM).

De esta manera se puede expresar la energía del sistema QM/MM como:

$$E = E_{QM} + E_{QM/MM} + E_{MM} \quad (1.7)$$

donde la energía  $E_{QM}$  se obtiene mediante el método DFT visto más arriba, la energía  $E_{MM}$  proviene de simular el campo de fuerzas clásico y  $E_{QM/MM}$  surge de la interacción entre las regiones *QM* y la regiones *MM* del modelo.

Esta última se calcula, mediante la ecuación:

$$E_{QM/MM} = \sum_{l=1}^{N_c} q_l \int \frac{\rho(r)}{|r - R_l|} + \sum_{l=1}^{N_c} \sum_{\alpha=1}^{N_q} [v_{LJ}(|R_l - \tau_\alpha|) + \frac{q_l z_\alpha}{|R_l - \tau_\alpha|}] \quad (1.8)$$

donde el primer término da cuenta de la interacción entre una carga puntual del sistema clásico con la densidad electrónica, y el segundo término representa la interacción entre los núcleos clásicos con los cuánticos mediante un potencial de Lennard-Jones y la interacción Coulombica entre las cargas.

Los métodos *QM/MM*, dentro del marco de métodos multiescala, son ampliamente utilizados en la práctica. Estos modelos han valido a Karplus, Levitt y Warshel el premio Nobel de Química en 2013, por su valor para la simulación de sistemas complejos.

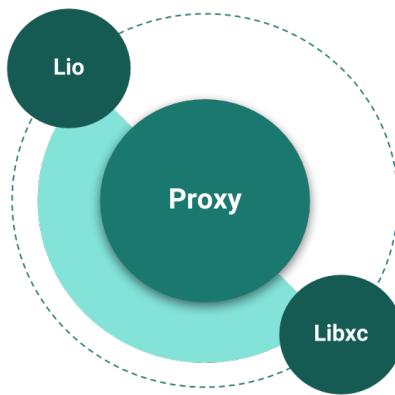

Nuestro trabajo se realiza en base a programas ya existentes. El cálculo de  $E_{QM}$  y  $E_{QM/MM}$  son realizados por la aplicación LIO [2, 4], el cual está optimizado para el uso de distintas arquitecturas de CPU y GPU. Este paquete se complementa mediante el uso del programa de dinámica molecular Amber [5], que realiza el cálculo de  $E_{MM}$ .

## 1.2. Libxc

**Libxc** [6] es una biblioteca de funcionales de intercambio y correlación en el marco de la teoría funcional de la densidad. El objetivo es proporcionar un conjunto portátil, bien probado y confiable de funcionales de intercambio y correlación que puedan ser utilizadas por otros programas.

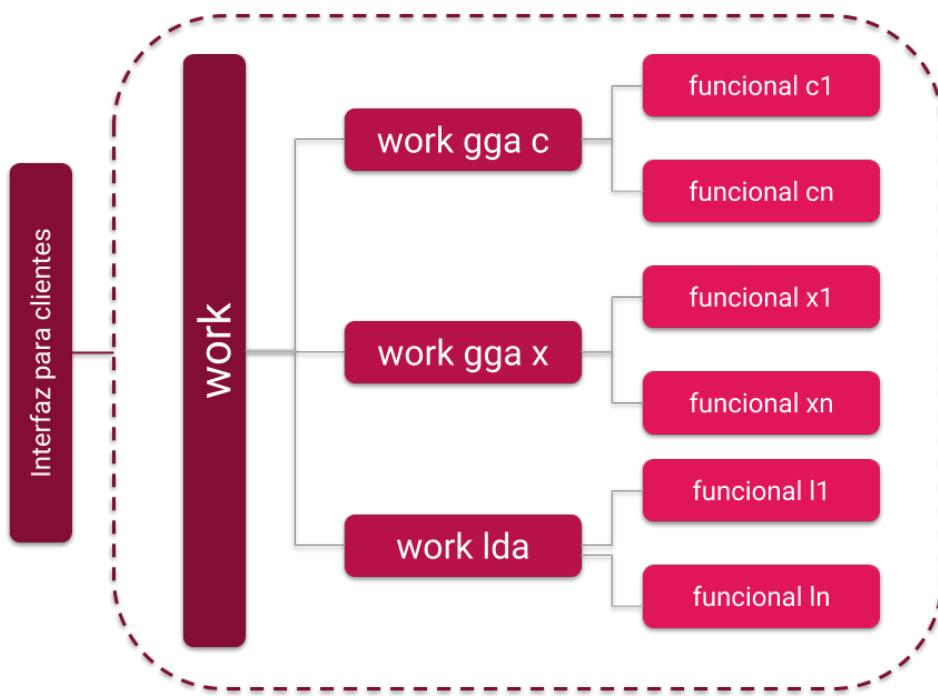

En **Libxc** se pueden encontrar diferentes tipos de funcionales: LDA, GGA, híbridos y mGGA. Estos funcionales dependen de la información local, en el sentido de que el valor del potencial en un punto dado depende únicamente de los valores de la densidad (y el gradiente de la densidad y la densidad de energía cinética, para los casos de GGA y mGGA), en un punto dado puede calcular la energía de intercambio y correlación:

$$\begin{aligned} E_{XC}^{\text{LDA}} &= E_{XC}^{\text{LDA}}[n(\vec{r})] \\ E_{XC}^{\text{GGA}} &= E_{XC}^{\text{GGA}}[n(\vec{r}), \vec{\nabla}n(\vec{r})] \\ E_{XC}^{\text{Hyb}} &= a_x E^{\text{EXX}} + E_{XC}^{\text{GGA}}[n(\vec{r}), \vec{\nabla}n(\vec{r})] \\ E_{XC}^{\text{mGGA}} &= E_{XC}^{\text{mGGA}}[n(\vec{r}), \vec{\nabla}n(\vec{r}), \nabla^2n(\vec{r}), \tau(\vec{r})] \end{aligned}$$

Donde  $n(\vec{r})$  es el valor de la densidad en las coordenadas  $\vec{r}$ ,  $\tau(\vec{r})$  es la energía cinética en el mismo,  $\vec{\nabla}$  denota el gradiente, y  $\nabla^2n(\vec{r})$  el laplaciano.

También puede calcular los gradientes de esta energía y para la mayoría de los funcionales también derivadas de orden superior.

El código fuente de los funcionales de **Libxc** se encuentra implementado en C generado a través de un programa de manipulación de objetos matemáticos llamado **Maple**.

Un factor importante a tener en cuenta es que **Libxc** está diseñada para ser ejecutada en CPU y utiliza números de doble precisión para realizar los cálculos de los funcionales. Esto implica que el mayor esfuerzo del presente trabajo estará centrado en, no solo realizar una traducción automática del código de los 180 funcionales para que funcionen en GPU, sino también que esa traducción utilice de manera eficiente los recursos que proveen las arquitecturas de cómputo paralelo de las placas de video.

En resumen, el objetivo del presente trabajo es extender la funcionalidad de **LIO** poniendo a disposición los 180 funcionales que provee **Libxc**, modificados de modo que puedan ser ejecutados eficientemente en tarjetas gráficas (GPUs).

## 2. ARQUITECTURAS EN PROFUNDIDAD

### 2.1. GPGPU con CUDA

Una de las arquitecturas analizadas en este trabajo es la arquitectura GPU desarrollada por Nvidia, conocida como **CUDA** por las siglas en inglés de *Compute Unified Device Architecture*. CUDA surge naturalmente de la aplicación del hardware desarrollado para aplicaciones de uso intensivo de gráficos, pero aplicados al cómputo científico.

Las placas de vídeo aparecen en 1978 con la introducción de Intel del chip iSBX 275. En 1985, la **Commodore Amiga** incluía un coprocesador gráfico que podía ejecutar instrucciones independientemente del CPU, un paso importante en la separación y especialización de las tareas. En la década del 90, múltiples avances surgieron en la aceleración 2D para dibujar las interfaces gráficas de los sistemas operativos y, para mediados de la década, muchos fabricantes estaban incursionando en las aceleradoras 3D como agregados a las placas gráficas tradicionales 2D. A principios de la década del 2000, se agregaron los *shaders* a las placas, pequeños programas independientes que corrían nativamente en la GPU, y se podían encadenar entre sí, uno por pixel en la pantalla [7]. Este paralelismo es el desarrollo fundamental que llevó a las GPU a poder procesar operaciones gráficas órdenes de magnitud más rápido que los CPU normales.

En el 2006, Nvidia introduce la arquitectura G80, que es la primer GPU que deja de resolver únicamente problemas de gráficos para pasar a ser un motor genérico. Contaba con un set de instrucciones consistente para todos los tipos de operaciones que realizaba (geometría, vertex y pixel shaders) [8]. Como subproducto de esto, la GPU pasa a tener procesadores simétricos más simples y fáciles de construir. Esta arquitectura es la que se ha mantenido y mejorado en el tiempo, permitiendo a las GPU escalar masivamente en procesadores simples, de baja frecuencia de reloj y con una disipación térmica manejable.

Los puntos fuertes de las GPU modernas consisten en poder atacar los problemas de paralelismo de manera pseudo-explicita, y con esto poder escalar “fácilmente” si solamente se corre en una placa con más procesadores [9].

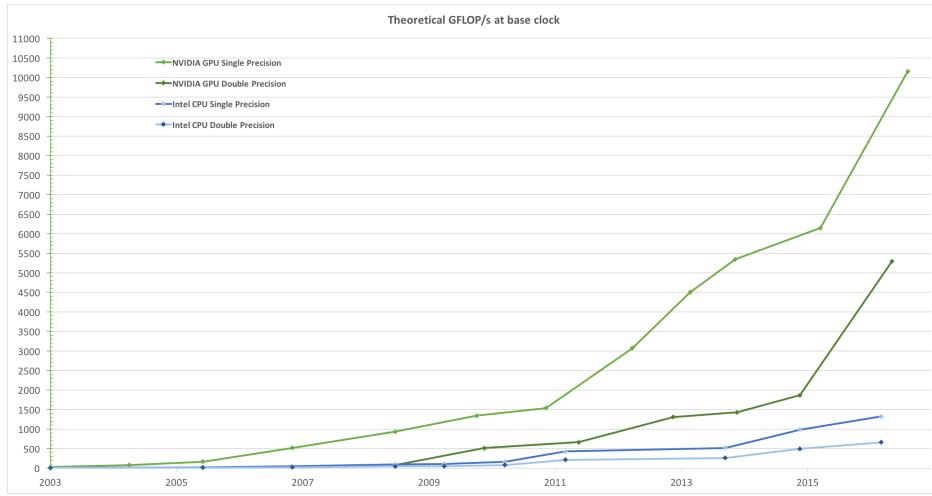

Técnicamente, esta arquitectura cuenta con entre cientos y miles de procesadores especializados en cálculo de punto flotante, procesando cada uno un *thread* distinto pero trabajando de manera sincrónica agrupados en bloques. Cada procesador, a su vez, cuenta con entre 63 a 255 registros [10, 11] de memoria para almacenar resultados. Las GPUs cuentan con múltiples niveles de cache y memorias especializadas (subproducto de su diseño fundamental para gráficos). Estos no poseen instrucciones SIMD, ya que su diseño primario esta basado en cambio, en SIMT (*Single Instruction Multiple Thread*), las cuales se ejecutan en los bloques sincrónicos de procesadores. De este modo, las placas modernas como la Nvidia **Tesla K40** alcanzan un poder de cómputo de 4,3 TFLOPs (4300 mil millones de operaciones de punto flotante por segundo) en cálculos de precisión simple, 1,7 TFLOPs en precisión doble y 288 GB/seg de transferencia de memoria, usando 2880 CUDA cores [12]. Para poner en escala la concentración de poder de cálculo: una computadora usando solo dos de estas placas posee una capacidad de cómputo comparable a la supercomputadora más potente del mundo en Noviembre 2001. Una comparativa del poder de cómputo teórico entre GPUs y CPUs puede verse en la figura 2.1.

Sin embargo, para poder explotar la arquitectura CUDA, los programas deben ser

Fig. 2.1: Picos teóricos de *performance* en GFLOPS/s. Reproducido de [9].

diseñados de manera de que el problema se pueda particionar usando el modelo de grilla de bloques de *threads*. Para este propósito es que Nvidia desarrolló la arquitectura CUDA.

Hoy en día, poder aprovechar la potencialidad de las GPU requiere una reescritura completa de los códigos ya existentes desarrollados para CPU y un cambio de paradigma importante, al dejar de tener vectorización, paralelización automática y otras técnicas tradicionales de optimización en CPU. Sin embargo, este trabajo ha rendido sus frutos en muchos casos: en los últimos seis años, la literatura de HPC con aplicaciones en GPU ha explotado con desarrollos nuevos basados en la aceleración de algoritmos numéricos (su principal uso). Por este motivo, este trabajo no ahondará en las particularidades del lenguaje CUDA y su modelo de paralelismo, más allá de lo estrictamente necesario para analizar *performance*. Para más información se puede consultar la bibliografía [8, 13, 14].

Además, no todas las aplicaciones deben reescribirse de manera completa. Con la introducción de las bibliotecas CuBLAS y CuFFT, se ha buscado reemplazar con mínimos cambios las históricas bibliotecas BLAS y FFTw, piedras fundamentales del cómputo científico [15, 16].

Además, se siguen desarrollando nuevas soluciones que consideran la portabilidad entre plataformas: las bibliotecas como Thrust [17], OpenMP 4.0 [18] y OpenACC 2.0 [19] son herramientas que buscan generar código que puedan utilizar eficientemente el acelerador de cómputo que se haya disponible. Estas herramientas permiten definir las operaciones de manera genérica y dejar el trabajo pesado al compilador para que subdivida el problema de manera que el acelerador (CPU, GPU, MIC) necesite. Obviamente, los ajustes finos siempre quedan pendientes para el programador especializado, pero estas herramientas representan un avance fundamental al uso masivo de técnicas de paralelización automáticas, necesarias hoy día y potencialmente imprescindibles en el futuro.

### 2.1.1. Organización de procesadores

Los procesadores GPGPU diseñados por Nvidia han sido reorganizados a lo largo de su existencia múltiples veces pero conservan algunas líneas de diseño a través de su evolución. A continuación se describe en detalle la organización definida en la arquitectura Fermi y en las secciones subsiguientes daremos los detalles más importantes de las arqui-

tecturas Kepler, Maxwell y Pascal. Por último realizaremos una breve comparación de las características principales de cada arquitectura.

Las arquitecturas de las GPUs se centran en el uso de una cantidad escalable de procesadores *multithreaded* denominados *Streaming Multiprocessors* (SMs). Un multiprocesador está diseñado para ejecutar cientos de threads concurrentemente, usando sus unidades aritméticas llamadas *Streaming Processors* (SPs). Las instrucciones se encadenan para aprovechar el paralelismo a nivel instrucción dentro de un mismo flujo de ejecución, y funcionando en conjunto con el paralelismo a nivel de *thread*, usado de manera extensa a través del hardware. Todas las instrucciones son ejecutadas en orden y no hay predicción de saltos ni ejecución especulativa, todo se ejecuta solamente cuando se lo necesita [14].

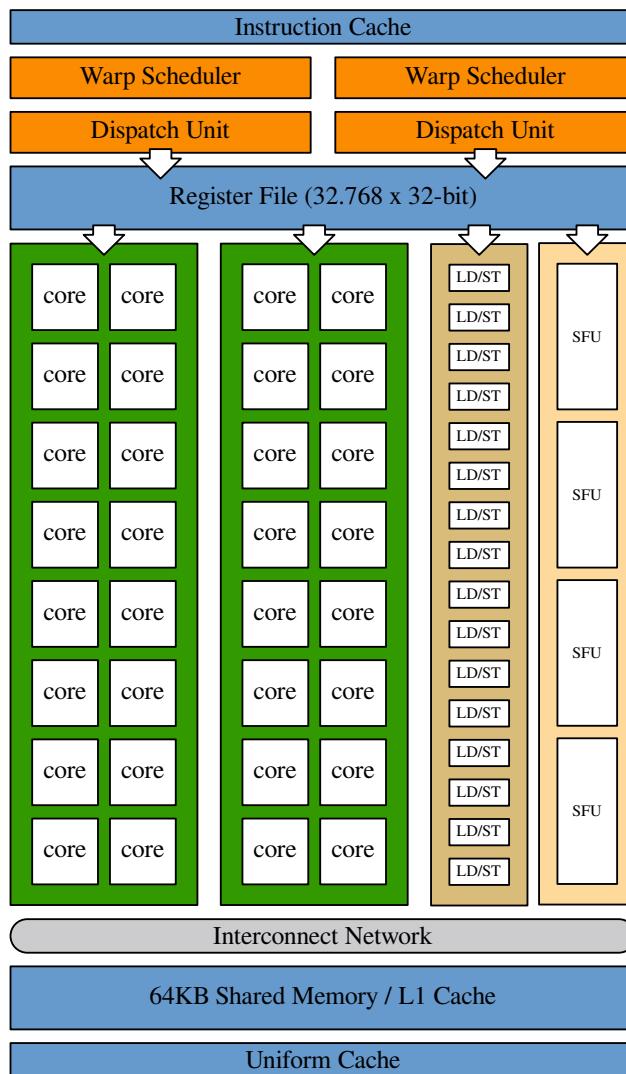

Fig. 2.2: Diagrama de bloques del SM de GF100 Fermi. Basado en [10].

Los SMs (figura 2.2) son unidades completas de ejecución. Cada uno de ellos tiene 32 SPs interconectados entre sí que operan sobre un *register file* de 64 KB común a todos. Los SMs cuentan con múltiples unidades de *Load/Store*, que permiten realizar accesos a memoria independientes. Existen cuatro unidades de SFU (*Special Function Unit*) por

SM, para realizar rápidamente operaciones matemáticas trascendentales (trigonometrías, potencias, raíces, etc.). Cada SM ejecuta simultáneamente una cantidad fija de threads, llamado *warp*, con cada uno de estos corriendo en un SP. Las unidades de despacho de warps se encargan de mantener registro de qué *threads* están disponibles para correr en un momento dado y permiten realizar cambios de contexto por hardware eficientemente ( $< 25\mu\text{s}$ ) [20]. Con esto, se pueden ejecutar concurrentemente dos warps distintos para esconder la latencia de las operaciones. En precisión doble, esto no es posible, así que hay solamente un warp corriendo a la vez.

Un SM cuenta con una memoria común de 64 KB que se puede usar de forma automática tanto como memoria compartida común a todos los *threads* como cache L1 para todos los accesos a memoria.

Fig. 2.3: Diagrama de bloques de GF100 Fermi. Tomado de [10].

Por como funciona un pipeline gráfico clásico, los SM se agrupan de a cuatro en GPCs (*Graphics Processing Cluster*) y no interactúa con el modelo de cómputo de CUDA. Un esquema de esta división global de los SM y cómo se comunican puede verse en la figura 2.3.

Todos los accesos a memoria global (la memoria por fuera del procesador) se realizan a través de la cache L1 de cada SM y a través de la L2 del todo el procesador. Esta L2 consiste de seis bancos compartidos de 128 KB. Estas caches se comunican de manera directa tanto con la DRAM propia de la placa como con el bus PCI Express por el cual pueden comunicarse dos placas entre sí, sin pasar por CPU, y son *write-through*, es decir cada escritura se hace tanto en la DRAM como en la memoria cache.

Como estos procesadores implementan el estándar IEEE754-2008, cuentan con operaciones de precisión simple y doble acorde al mismo, por lo cual los cálculos intermedios

en operaciones como FMA (*Fused Multiply-Add*), que toma tres operandos y devuelve el producto de dos de ellos sumado al tercero, no pierden precisión por redondeo.

### 2.1.2. Organización de la memoria

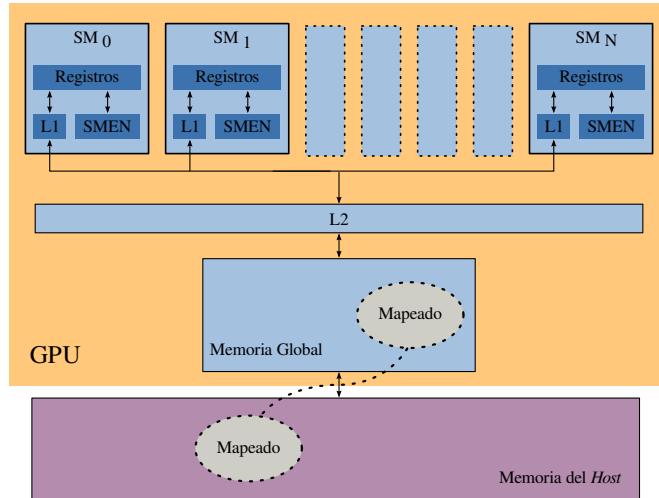

La memoria de la GPU es uno de los puntos cruciales de esta arquitectura, un esquema gráfico puede observarse en la figura 2.4. Esta se subdivide entre memorias on-chip y memorias on-board, de acuerdo a su ubicación y latencia de acceso, en cuatro categorías distintas:

- Registros

- Memoria local

- Memoria compartida

- Memoria global

Cada *thread* de ejecución cuenta con una cantidad limitada de registros de punto flotante de 32 bits con latencia de un par de ciclos de clock. A su vez, existe una cantidad finita de registros totales con los que cuenta un SM (oscila entre 16535 y 65535 registros). Debido a la baja latencia de acceso, son la clase principal de almacenamiento temporal.

La memoria local es una memoria propia de cada *thread*, y se encuentra almacenada dentro de la memoria global. Esta memoria es definida automáticamente por el compilador y sirve como área de almacenamiento cuando se acaban los registros: los valores anteriores se escriben a esta memoria, dejando los registros libres para nuevos valores en cálculos, y cuando se terminan estos cálculos se carga los valores originales nuevamente. Cuenta con las mismas desventajas que la memoria global, incluyendo su tiempo de acceso.

La memoria compartida, o *shared*, es una memoria que es visible para todos los *threads* dentro de un mismo SM. Cada *thread* puede escribir en cualquier parte de la memoria compartida dentro de su bloque y puede ser leído por cualquier otro *thread* de éste. Es una memoria muy rápida, on-chip, y que tarda aproximadamente 40 ciclos de acceso [21]. Esta memoria es compartida con la cache L1, la cual tiene capacidad de entre 16 KB y 64 KB configurable por software. Se encuentra dividida en 32 bancos de 2 KB de tamaño, permitiendo que cada uno de los 32 *threads* acceda independientemente a un float. Si hubiera conflicto, los accesos a ese banco se serializarían, aumentando la latencia de acceso a la memoria [13].

La memoria global es la memoria principal fuera del chip de la GPU. Ésta es de gran tamaño (de entre 1 GB y 12 GB) y es compartida por todos los SM de la GPU y los CPU que integran el sistema. Es decir, tanto los GPU como los CPU pueden invocar las funciones de CUDA para transferir datos entre la memoria de la placa y la memoria RAM de *host*. La latencia de acceso a la memoria global es de cientos de ciclos [21], sumamente lenta en comparación con el procesador. La memoria global también puede ser mapeada, o *pinneada*, para que exista una copia de esa reserva tanto en la memoria de la placa como en la memoria principal del procesador. El driver de CUDA mantiene la consistencia entre ambas de manera asíncrona, evitando la necesidad de hacer copias de memoria explícitas. No es ilimitada la cantidad de memoria mapeada posible, por lo que es importante saber elegir qué elementos se van a almacenar de esta manera.

Fig. 2.4: Esquema de la jerarquía de memorias en GPU, detallando de las disponibles en cada SM, la memoria compartida (SMEN), la L2 global, la memoria de la placa (global) y la mapeada entre el *host* y la placa de video. Tomado de [13].

Adicionalmente, la GPU cuenta con múltiples niveles de memorias cache para poder aminorar el hecho de que el principal cuello de botella del cómputo es la latencia en los accesos a memoria global. Estas se dividen en cuatro:

- Cache L1

- Cache L2

- Cache constante

- Cache de textura

La cache L1 es dedicada por SM. Esta cache fue introducida en la arquitectura Fermi y su diseño hace que también esté dedicada a la memoria compartida, por lo que es posible en tiempo de ejecución darle directivas a la GPU que asigne más memoria cache o más memoria compartida, permitiendo a los bloques tener mayores espacios de memorias compartidas o mayores *hit rates* de caches.

La cache L2 es común a todos los SM de la GPU, donde, a partir de Fermi en Nvidia, todos los accesos de lectura y escritura a memoria global y textura pasan a través de ésta [10].

La cache constante es una cache sobre la memoria global dedicada solamente a lecturas de memoria. Ésta es muy reducida (solo cuenta con 64 kB) y está optimizada para muchos accesos a la misma dirección. Cuando un *thread* lee esta memoria, se retransmite a los demás *threads* del warp que estén leyendo esa misma dirección, reduciendo el ancho de banda necesario. Si, en cambio, los *threads* leen distintas direcciones, los accesos se serializan. Cuando hay un *miss* de esta memoria, la lectura tiene el costo de una lectura de memoria global.

La cache de textura es una cache sobre la memoria global que presenta no solo localidad espacial, como la mayoría de las caches de procesadores normales (es decir, la cache contiene una porción consecutiva de la memoria principal), sino que se le puede agregar

el concepto de dimensiones, para poder modelar datos en más de una dimensión. Esto se adapta muy bien a los problemas de gráficos en 2D y 3D, y es una herramienta clave a la hora de minimizar los accesos a matrices no solo por filas sino por columnas. Esta cache se debe definir en momento de compilación en el código, ya que tiene límites espaciales (necesarios para poder definir áreas de memoria sobre la cual operar) y a su vez se debe acceder a los datos subyacentes a través de funciones específicas. Una característica adicional de esta cache es que como necesita resolver estos accesos no convencionales a la memoria, cuenta con una unidad propia de resolución de direcciones. Esta unidad tiene limitantes en cuanto a sus posibilidades, ya que no posee un ancho de banda suficiente como para resolver todos los accesos a memoria globales que podrían surgir, por lo cual su uso debe ser criterioso.

### 2.1.3. Esquema de paralelismo

Al ser una arquitectura masivamente paralela desde su concepción, CUDA presenta varios niveles de paralelismo, para agrupar lógicamente el cómputo y poder dividir físicamente su distribución. Los principales son:

- Bloques de *threads*

- Grilla de bloques

- Streams

- Múltiples placas

El paralelismo a nivel de bloque instancia una cantidad de *threads*, subdivididos lógicamente en 1D, 2D o 3D. Los *threads* internamente se agrupan de a 32, es decir, un *warp*. Cada uno de estos *threads* va a contar con una manera de identificarlos únicamente: un **blockId** y, dentro de cada bloque, su propio **threadId**. Además, van a correr simultáneamente en el mismo SM y van a ser puestos y sacados de ejecución de a un warp dinámicamente por el *scheduler* de hardware con que cuenta cada SM. Para compartir información entre ellos, se puede utilizar la memoria compartida o las instrucciones de comunicación de *threads intra-warp* (solo disponibles a partir de Kepler [11]).

El paralelismo a nivel de grilla determina una matriz de bloques de ejecución que partitiona el dominio del problema. El *GigaThread Scheduler* va a ejecutar cada bloque en un SM hasta el final de la ejecución de todos los *threads* de éste. Los bloques no comparten información entre sí. Por esto, no pueden ser sincronizados mediante memoria global ya que no se asegura el orden en el que serán puestos a correr, y un bloque mantiene su SM ocupado hasta que termine de ejecutar, bloqueando a los demás (es decir, no hay *preemption* en los SM).

El paralelismo de stream es una herramienta empleada para hacer trabajos concurrentes usando una sola placa. Esta técnica permite que múltiples kernels (unidades de código en CUDA) o copias de memoria independientes estén encolados, para que el driver pueda ejecutarlas simultáneamente si se están subutilizando los recursos, de forma de minimizar tiempo ocioso del dispositivo. Los streams permiten kernels concurrentes pero cuentan con importantes restricciones que generan sincronización implícita, lo cual hay que tener presente si se desea mantener el trabajo de forma paralela.

El paralelismo a nivel de placa consiste en poder distribuir la carga del problema entre distintas GPUs dispuestas en un mismo sistema compartiendo una memoria RAM

común como si fuera un software multithreaded tradicional. CUDA no cuenta con un modelo implícito de paralelismo entre distintas placas, pero es posible hacerlo manualmente eligiendo de manera explícita qué dispositivo usar. Las placas se pueden comunicar asíncronamente entre sí, tanto accediendo a las memorias globales de cada una como ejecutando código remotamente. En las versiones modernas del driver de CUDA, también pueden comunicarse directamente las placas entre sí a través de la red, permitiendo escalar multinodo fácilmente en un cluster de cómputo [13].

#### 2.1.4. Arquitectura Kepler

La arquitectura Kepler [11] fue presentada a fines del año 2012 y posee más del doble de transistores que su arquitectura predecesora (Fermi). Uno de los principales objetivos del diseño de la arquitectura Kepler fue el de mejorar el consumo de energía. Su procesador de 28 nm juega un rol fundamental en la reducción del consumo de energía, pero a su vez se realizaron varias modificaciones a la arquitectura de la GPU para lograr reducir aún más el consumo y lograr mantener un buen rendimiento, dando como resultado una mejora de 3x por watt con respecto a la arquitectura Fermi.

Otro de los objetivos del diseño fue el de incrementar de forma significativa el rendimiento de la aritmética de doble precisión. En efecto, la arquitectura Kepler proporciona más de 1 TFLOP en el rendimiento de operaciones de doble precisión con más del 80 % de eficiencia en las operaciones de multiplicaciones matriciales de doble precisión (DGEEM) contra 60 – 65 % en la arquitectura Fermi.

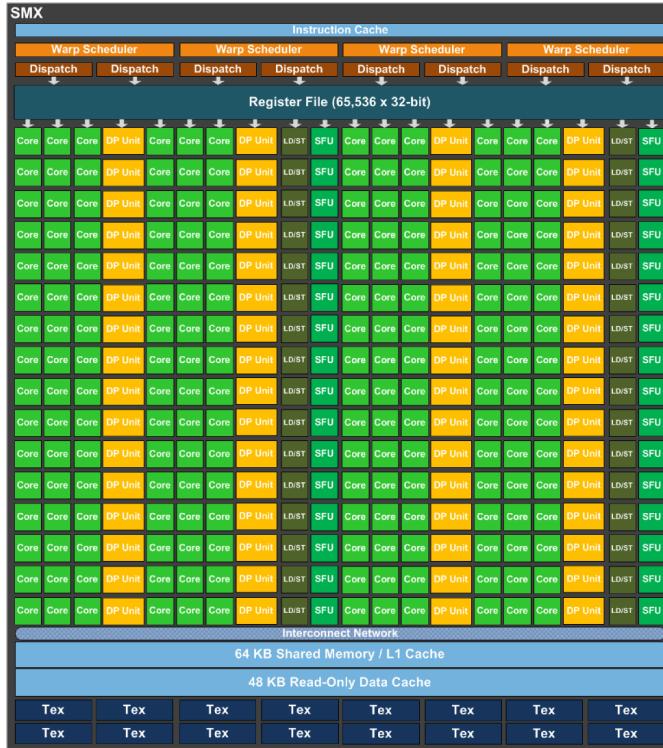

La arquitectura Kepler [11] es bastante parecida a la de Fermi, pero con una diferencia importante: La cantidad de SPs por Streaming Multiprocessor (llamados SMX en Kepler) se incrementan de 32 a 192. La frecuencia del reloj se decrementa de 1.5 GHz a 1 GHz continuando la tendencia de incrementar el poder de cómputo al utilizar mas núcleos que corren a menor frecuencia de reloj. Los puntos claves de la arquitectura incluyen:

- Un nuevo procesador SMX.

- Un subsistema de memoria mejorado, el cual ofrece capacidades adicionales de cache, más ancho de banda en la jerarquía y un sistema de I/O a memoria totalmente rediseñado y sustancialmente más rápido.

- Soporte de hardware en todo el diseño el cual permite nuevas capacidades en el modelo de programación.

Cada una de las unidades SMX contiene 192 núcleos CUDA de simple precisión, y cada núcleo tiene incorporadas unidades lógico-aritméticas. La arquitectura también respeta la norma IEEE 754-2008 respecto a la aritmética de simple y doble precisión que fue introducida en Fermi, incluyendo además las operaciones conocidas como multiply-add (FMA), que pueden resolver una multiplicación y una suma como si fuera una única instrucción. Las unidades SMX de Kepler también mantienen lo que se conoce como unidades de función especial (SFUs) las cuales sirven para aproximar de manera rápida operaciones transcendentales, con un total de 32 SFUs (8 veces más que en Fermi).

El warp scheduler de los SMX también presenta modificaciones. Bajo este esquema se puede programar un warp completo (32 threads) cada ciclo, cuando en Fermi el scheduler solo se podía programar 16 threads. Cada SMX ofrece cuatro schedulers para los warps y ocho unidades de despacho, permitiendo de esta manera que cuatro warps sean ejecutados simultáneamente. Por lo tanto, se puede programar la ejecución de 128 threads en

Fig. 2.5: Esquema de organización de los SMX en la arquitectura Kepler, aquí podemos ver los 192 núcleos de simple presición. Tomado de [11].

cada ciclo para los 192 núcleos. A diferencia de la arquitectura Fermi, la cual no permite que instrucciones de doble precisión sean emparejadas con otras instrucciones, la arquitectura Kepler permite que las instrucciones de doble precisión se emparejen con otras instrucciones.

El número de registros de memoria a los cuales puede acceder un thread se cuadriplicó, permitiendo que cada thread tenga acceso hasta 255 registros. Los kernels de CUDA que utilizan una gran cantidad de registros ahora pueden lograr aceleraciones sustanciales como resultado de la mayor cantidad de registros disponibles por subproceso. Para mejorar aún más el rendimiento, Kepler implementa un nuevo mezclador de instrucciones, el cual permite compartir datos entre los threads de un warp. El mezclador soporta referencias indexadas y ofrece una mejora en el uso de la memoria compartida ya que las operaciones de *load* y *store* son llevadas a cabo en un solo paso.

### Subsistema de memoria

La jerarquía de memoria en la arquitectura Kepler está organizada de manera similar a la de la arquitectura Fermi. La arquitectura soporta accesos a memoria unificados para *loads* y *stores* a través de una memoria cache L1 por cada multiprocesador SMX. La arquitectura Kepler también permite mediante directivas de compilador el uso de una memoria cache adicional para lectura de datos. Así como en la arquitectura Fermi, cada SMX tiene 64 kB de memoria *on-chip* la cual puede ser configurada como 48 kB de memoria compartida con 16 kB de cache L1, o como 16 kB de memoria compartida con 48 kB de memoria cache L1. Además, la arquitectura Kepler permite 32 kB / 32 kB divididos entre

memoria compartida y memoria cache L1.

El ancho de banda de la memoria compartida para operaciones que superan los 64 B fue duplicado en comparación con los SM de la arquitectura Fermi. Además de la memoria cache L1, la arquitectura Kepler introduce una memoria cache de 48 kB para datos de solo lectura. En la generación Fermi, la memoria cache de solo lectura era accesible por la unidad de texturas. En Kepler, la cache es accesible directamente por el SM para operaciones generales de carga de datos. Por otro lado, también dispone de una memoria cache L2 dedicada de 1536 kB, el doble que en las arquitecturas Fermi. El ancho de banda de la memoria cache L2 también se duplicó al doble con respecto a la arquitectura Fermi.

La eficiencia de la memoria de textura fue mejorada de forma significativa, cada una de las unidades SMX contiene 16 unidades de filtrado de texturas (cuatro veces más que la arquitectura Fermi). Además, la arquitectura Kepler modifica la forma en que se maneja el estado de las texturas. En la arquitectura Fermi, para que la GPU refiere a una textura, había que asignar un espacio de memoria de tamaño fijo previo a la ejecución de un kernel. Dicho espacio de memoria limita la cantidad de texturas sobre las cuales un kernel puede leer en tiempo de ejecución. En la arquitectura Kepler, se elimina este paso de asignación ya que el estado de la textura se almacena como un objeto en memoria y es el hardware el que se encarga de buscar los objetos bajo demanda. Esto elimina cualquier limitación en el número de texturas que pueden ser referenciadas por un kernel.

### Mejoras principales de la arquitectura Kepler

Las siguientes características de la arquitectura Kepler permiten un incremento en la utilización de la GPU, simplifican el diseño de programas que realizan cómputos en paralelo y ayuda a simplificar la creación de programas para que sean compatibles tanto en computadoras de escritorio como en supercomputadoras.

### Paralelismo dinámico

El paralelismo dinámico es una nueva característica de la arquitectura Kepler el cual permite a la GPU generar trabajos nuevos por su cuenta, sincronizar los resultados y controlar la programación de esos trabajos a través de hardware dedicado. Todo sin tener que incluir el uso del CPU del host. En arquitecturas anteriores, todo el trabajo que realizaban las GPUs era invocado desde el CPU del host, se esperaba a su finalización y por último se copiaban los resultados nuevamente al host. En las arquitecturas Kepler, un kernel puede realizar llamadas a otros kernels, crear streams, eventos y manejar las dependencias necesarias para procesar trabajo adicional sin necesidad de interactuar con la CPU del host. Esta innovación ayuda a los desarrolladores a crear y optimizar programas que tienen una gran dependencia de datos, también permite que una mayor cantidad de programas sean ejecutados directamente en la GPU. Esto permite que el CPU del host se encuentre libre para realizar tareas adicionales, o para que los sistemas se puedan configurar con CPU menos potentes para realizar la misma cantidad de trabajo. Esta nueva característica de los kernel de poder realizar trabajos adicionales le permite a los programadores realizar un mejor balance de los recursos en el diseño de sus programas y también poder concentrarse en las áreas del problema que requieren mayor poder de cómputo.

### Hyper-Q

Hyper-Q permite que múltiples núcleos de CPU del host puedan utilizar simultáneamente la misma GPU para realizar trabajos, de este modo se incrementa de forma significativa la utilización de la GPU y al mismo tiempo se reduce tiempo en el que el CPU del host se encuentra ocioso. Con Hyper-Q se incrementa el número total de conexiones (conocidas como *work queues*) entre el host y el distribuidor de trabajos de CUDA (CUDA Work Distributor o CWD) permitiendo un total de 32 conexiones en paralelo (en la arquitectura Fermi solo existe una sola conexión disponible).

### NVIDIA GPUDirect

NVIDIA GPUDirect se refiere a la capacidad que tienen las GPUs dentro de una computadora, o las GPUs en diferentes servidores en una red, de intercambiar datos sin tener que utilizar la memoria principal del host. Esta nueva característica mejora el rendimiento y reduce la latencia en la transferencia de datos, por otro lado reduce el ancho de banda permitiendo que la GPU se encuentre libre para realizar otras tareas.

#### 2.1.5. Arquitectura Maxwell

La primera generación de placas de video con arquitectura Maxwell fueron presentadas a principios de el año 2014 y contiene un conjunto de mejoras diseñadas para obtener un mayor rendimiento energético por watt. La primera GPU basada en la arquitectura Maxwell fue diseñada para trabajar en ambientes en donde el recurso de energía es limitado como en computadoras portátiles y computadoras personales [22].

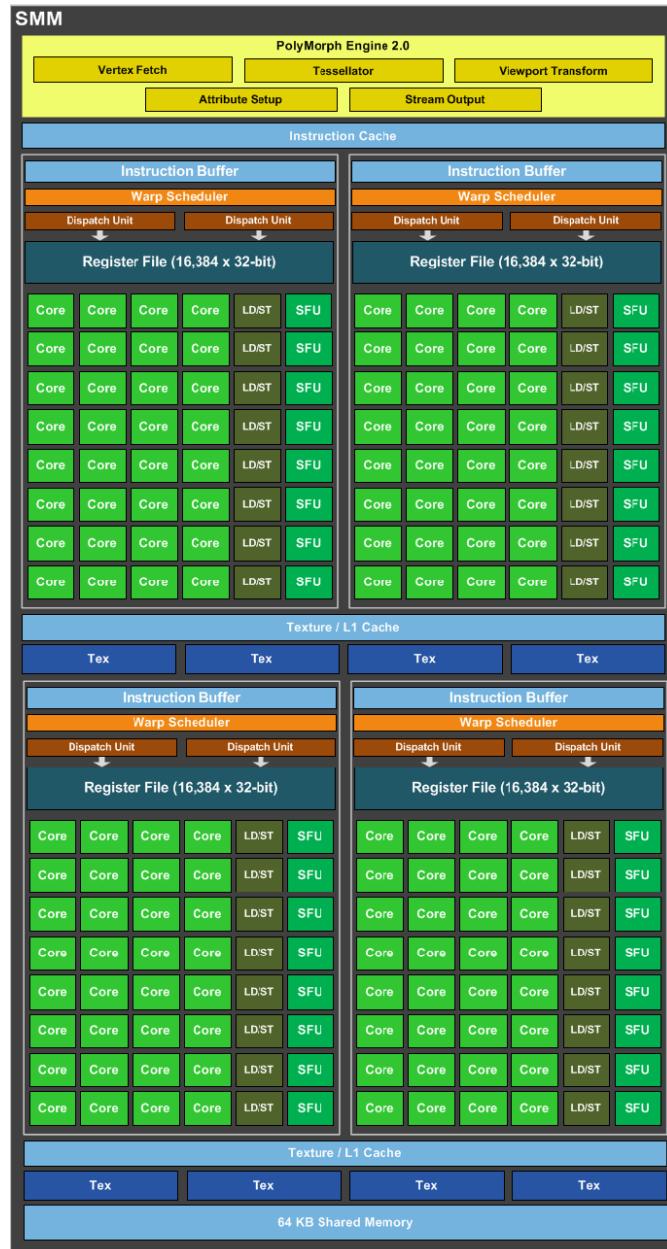

La arquitectura Maxwell presenta un nuevo diseño para los Streaming Multiprocessors (SM) el cual mejora de manera drástica el rendimiento por Watt. Mejoras para controlar la lógica de particionado, el balance de los trabajos, los schedulers, el número de instrucciones emitidas por ciclo de reloj entre otras permite que los SM de la arquitectura Maxwell (llamados SMM) superen ampliamante el rendimiento de los SM de la arquitectura Kepler.

La organización de los SM también sufrió modificaciones (ver figura 2.6). La cantidad de núcleos por SM fue reducida a una potencia de dos, dejando un total de 128 núcleos. Cada uno de los SMM se encuentra dividido en cuatro bloques de procesamiento los cuales a su vez tienen su propio buffer de instrucciones, su propio scheduler y cuenta con 32 núcleos. Este nuevo esquema de división simplifica el diseño, la lógica del scheduler, ahorra energía y reduce la latencia de los cómputos. Estos nuevos bloques de procesamiento comparten cuatro filtros de texturas y una memoria cache de texturas. Se combinaron las funciones de memoria cache L1 con las de memoria cache de texturas, y la memoria compartida se encuentra en una unidad separada la cual puede ser accedida por cada uno de los bloques.

Aunque el número total de núcleos por SM disminuyó de 192 en la arquitectura Kepler a 128 en la arquitectura Maxwell, gracias a las mejoras introducidas en esta nueva generación, el rendimiento por SMM es generalmente mayor al 10 % con respecto a los SMX de la arquitectura Kepler. Los SMM mantienen el mismo número de instrucciones por ciclo y reducen la latencia en las operaciones aritméticas con respecto a la arquitectura Kepler.

Así como los SMX, cada SMM contiene cuatro schedulers para los warps, pero a diferencia de los SMX, a cada uno de los núcleos SMM se les asigna un scheduler en particular. Dado que la cantidad de núcleos es una potencia de dos, el esquema de asignación de schedulers se ve simplificado ya que cada uno de los schedulers de los warps son asignados a

Fig. 2.6: Esquema de organización de los SMM en la arquitectura Maxwell. Tomado de [22].

un conjunto de núcleos de tamaño igual a la longitud de un warp.

Las capacidades de cómputo de los SMM de la arquitectura Maxwell son similares en muchos aspectos a las capacidades de cómputo de los SMX de la arquitectura Kepler, pero con algunas mejoras clave que apuntan a mejorar la eficiencia. El número de registros de memoria y la cantidad máxima de *warps* en un SMM son las mismas que en un SMX (64K con registros de 32-bits y 64 *warps*), así como el número de registros de memoria on-chip por thread (255). Sin embargo, el número máximo de threads activos por MP fue duplicado a 32 lo que da como resultado una mejora para los kernels que utilizan bloques con pocos threads (64 o menos). Otra mejora que presentan los SMM es que la latencia en la dependencia de instrucciones aritméticas fue reducida significativamente.

Los SMM tienen 64 kB de memoria compartida por SM, a diferencia de las arquitecturas Fermi y Kepler en las cuales los 64 kB de memoria son compartidos entre la memoria cache L1 y la memoria compartida. Esto es posible gracias a que la arquitectura Maxwell combina la funcionalidad de la memoria cache L1 y la de la memoria cache de texturas en una sola unidad.

La arquitectura Maxwell mantiene el *Paralelismo Dinámico* que fue introducido en la arquitectura Kepler que permite que los threads que se ejecutan en la GPU puedan ejecutar kernels sin necesidad de pasar por el CPU del host.

El tamaño de la memoria cache L2 fue incrementado a 2048 kB (contra 256 kB en la arquitectura Kepler) lo que permite tener una capacidad adicional de almacenamiento que puede ser utilizada para texturas y operaciones atómicas entre otras cosas. Al tener más memoria cache se reducen los accesos a la memoria principal y por lo tanto se reducen los cuellos de botella provocados por los accesos a memoria.

En resumen, toda la arquitectura fue rediseñada, los flujos de datos fueron optimizados, el ahorro de energía mejoró significativamente, por solo nombrar algunas de las modificaciones. Como resultado de todo este esfuerzo, la arquitectura Maxwell es capaz de brindar un rendimiento dos veces mayor al de sus predecesoras.

### 2.1.6. Arquitectura Pascal

En el año 2016 NVIDIA presenta la arquitectura Pascal la cual incluye tres nuevas características claves con respecto a las generaciones anteriores: Stacked DRAM, Memoria Unificada y NVLink. Stacked DRAM o Memoria 3D es una nueva característica por la cual se incluyen chips de memoria en el mismo módulo en donde se encuentra la GPU. Esto le permite a la GPU obtener datos de memoria mucho más rápido, incrementando el rendimiento y la performance. De esta manera es posible desarrollar una GPU más compacta y de mayor potencia para dispositivos pequeños. Como resultado, el ancho de banda de la memoria y la capacidad de cómputo es más de dos veces mayor, por otro lado el ahorro de energía es cuatro veces mayor que el de las arquitecturas predecesoras.

La *Memoria Unificada* consiste en permitirle al CPU del host acceder directamente a la memoria de la GPU y viceversa, de esta forma los desarrolladores se ahorran el paso de tener que reservar memoria entre ambos a la hora de escribir sus programas.

Con NVLink se incrementa el ancho de banda entre el CPU del host y la GPU, permitiendo que la transferencia de datos se dé a velocidades mayores a los 80 GB/s, comparado con los 16 GB/s de las arquitecturas predecesoras. De esta forma, la velocidad de las aplicaciones se encuentra menos restringida por la velocidad en la transferencia de los datos entre el CPU del host y la GPU.

### 2.1.7. Diferencias entre Tesla, Fermi, Kepler, Maxwell y Pascal

En la tabla 2.1 se presenta una comparación de los recursos que están más directamente relacionados a la *performance* de una GPU. Se puede apreciar el crecimiento notable del poder de cómputo debido a las tecnologías de fabricación, que permitieron aumentar la cantidad de transistores por unidad de superficie. También se puede comprobar que, a diferencia de las CPU, las arquitecturas GPU decidieron utilizar esos nuevos transistores disponibles para más núcleos de procesamiento, en vez de dedicarlos a aumentar las memorias cache, que crecieron mínimamente (comparando contra las caches de CPU).

| Características        | Tesla (GT200) | Fermi (GF100)   | Kepler (GK110)         | Maxwell (GM107) | Pascal (GP100)  |

|------------------------|---------------|-----------------|------------------------|-----------------|-----------------|

| Año introducción       | 2006          | 2010            | 2012                   | 2014            | 2016            |

| Transistores           | 1400 millones | 3000 millones   | 3500 millones          | 7100 millones   | 153000 millones |

| Tecnología fabricación | 65 nm         | 40 nm           | 28 nm                  | 28 nm           | 16 nm (FinFET)  |

| SMs                    | 30            | 16              | 15                     | 32              | 64              |

| SP / SM                | 8             | 32              | 192                    | 128             | 64              |

| Caché L1               | -             | 16 kB and 48 kB | 16 kB, 32 kB and 48 kB | 64 kB           | 64 kB           |

| Caché L2               | -             | 768 kB          | 1536 kB                | 2048 kB         | 4096 kB         |

| Memoria Shared/SM      | 16 kB         | 16 kB and 48 kB | 16 kB, 32 kB and 48 kB | 96 kB           | 64 kB           |

| Registros/Thread       | 63            | 63              | 255                    | 255             | 255             |

| Pico GFLOPS Simple     | 933           | 1345            | 3977                   | 4612            | 10600           |

| GFLOPS/Watt            | 3,95          | 5,38            | 15,9                   | 28,7            | 57,3            |

Tab. 2.1: Tabla comparativa de las características más prominentes de las diferentes versiones de arquitecturas CUDA.

La medida usada por Nvidia para publicitar la *performance* de estos dispositivos y poder compararlos entre sí, y contra CPU, son los GFLOPS. Ésta mide cuántas operaciones de punto flotante de precisión simple se pueden realizar por segundo. Los GFLOPs son utilizados también por los clusters en el ranking TOP500, en donde se ordenan de acuerdo a la *performance* medida usando un benchmark pre-establecido (i.e. LINPACK). No solo es notable cómo se cuadruplicó la *performance* (teórica) en solamente seis años, sino que aún más importante es como mejoró la *performance* por Watt. La tecnología de fabricación ha ayudado a la disminución del consumo, un problema que acechaba a los diseños Fermi, ya que sus consumos superiores a 200 W por dispositivo los hacían muy difíciles de refrigerar incluso en clusters de HPC. Se puede apreciar entonces la estrategia de mercado de Nvidia de introducirse en las supercomputadoras de todo el mundo, donde el consumo y la refrigeración son factores limitantes (mucho más aún que, por ejemplo, en computadoras de escritorio) [23].

### 2.1.8. CUDA, Herramientas de desarrollo, profiling, exploración

Para soportar una arquitectura masivamente paralela, se debe usar una ISA (*Instruction Set Architecture*) diseñada especialmente para el problema. En el caso de CUDA, esta ISA se denominada PTX y debe poder soportar conceptos fundamentales del cómputo GPGPU: grandes cantidades de registros, operaciones en punto flotante de precisión simple y doble, y FMA (fused multiply-add). Además, el código compilado para GPU debe ser agnóstico al dispositivo que lo va a ejecutar, por lo cual la parallelización no debe estar demasiado atada a éste, sino que el *dispatching* lo debe poder determinar el driver de la placa en tiempo de ejecución. Un último requerimiento clave de esta ISA es que debe

soportar hacer ajustes manuales, para poder construir partes claves de ciertas bibliotecas frecuentemente usadas (como las rutinas BLAS de álgebra lineal [10]).

El lenguaje CUDA es una extensión de C++, con ciertas características agregadas para poder expresar la subdivisión de las rutinas en *threads* y bloques, junto con mecanismos para especificar qué variables y funciones van a ejecutarse en la GPU y en el CPU. Una característica de CUDA es que todas las llamadas a los kernels de ejecución son asincrónicas, por lo que es relativamente sencillo solapar código en GPU y CPU. A su vez se cuenta con múltiples funciones opcionales, con distinta granularidad, que permiten esperar a que todas las llamadas asíncronas a GPU finalicen, agregando determinismo en forma de barreras de sincronización al lenguaje.

El código CUDA compila usando nvcc, una variante del GNU gcc que se encarga de generar el código PTX para las funciones que se van a ejecutar en las GPU. Este código objeto después se adosa normalmente con el resto del código que corre en CPU y se genera un binario ejecutable.

Nvidia, además, provee herramientas de profiling para explorar cómo se están utilizando los recursos durante la ejecución. Éstas son esenciales para optimizar, puesto que los limitantes de GPU son sumamente distintos a los de CPU, presentando dificultades conceptuales incluso para programadores experimentados. Las herramientas de profiling no solo muestran *runtime*, sino que sirven para ver dónde hay accesos a memoria excesivos, puntos de sincronización costosos, limitantes en los registros y como se superponen las llamadas asíncronas.

El uso de todas estas herramientas fue vital en este trabajo para poder entender cómo funciona la arquitectura en detalle, como medir *performance* y utilización, y cómo los cambios realizados impactaron en las distintas generaciones de dispositivos.

### 2.1.9. Requerimientos de un problema para GPGPU

Dada la organización de un procesador GPU, un problema debe exhibir al menos las siguientes características para que tenga potencialidad para poder aprovechar las características y recursos disponibles en esta arquitectura:

1. El problema debe tener una gran parte paralelizable.

2. El problema debe consistir, mayormente, de operaciones numéricas.

3. El problema debe poder ser modelado, en su mayor parte, utilizando arreglos o matrices.

4. La intensidad aritmética debe ser muy superior al tiempo de transferencia de datos.

El ítem 1 se refiere a que debe existir alguna forma de partir el problema en subproblemas que puedan realizarse simultáneamente, sin que haya dependencias de datos entre sí. Si el problema requiere partes seriales, lo ideal es que se las pueda dividir en partes independientes que sean etapas de una cadena de procesos, donde cada una de éstas exhiban características fuertemente paralelas. Como las arquitecturas masivamente paralelas tienen como desventaja una menor eficiencia por núcleo, si el problema no se puede dividir para maximizar la ocupación de todos los procesadores disponibles, va a resultar muy difícil superar en eficiencia a los procesadores seriales.

El ítem 2 habla acerca de que el método de resolución de los problemas debe provenir de una aplicación numérica o de gran carga aritmética. El set de instrucciones de las arquitecturas GPU están fuertemente influenciados por las aplicaciones 3D que las impulsaron en un principio. Éstas consisten mayormente de transformaciones de álgebra lineal para modelar iluminación, hacer *renders* o mover puntos de vistas. Todos estos problemas son inherentemente de punto flotante, por lo cual el set de instrucciones, las ALUs internas y los registros están optimizados para estos casos de uso.

El ítem 3 menciona que los problemas que mejor se pueden tratar en esta arquitectura se pueden representar como operaciones entre vectores o matrices de dos, tres o cuatro dimensiones. Las estructuras de datos no secuenciales en memoria incurren en múltiples accesos a memoria para recorrerlas y, en las arquitecturas GPU, pueden generar un importante cuello de botella. Además, suelen ser difíciles de paralelizar en múltiples subproblemas. Tener como parámetros de entrada matrices o arreglos que se puedan partir fácilmente producen en *overheads* mínimos de cómputo y permiten aprovechar mejor las memorias caches y las herramientas de *prefetching* que brinda el hardware.

Mientras tanto, el ítem 4 ataca uno de los puntos críticos de esta arquitectura. Para poder operar con datos, se requiere que estén en la memoria de la placa, no en la memoria de propósito general del host. Se debe, entonces, hacer copias explícitas entre las dos memorias, ya que ambas tienen espacios de direcciones independientes. Esta copia se realiza a través de buses que, a pesar de tener un gran *throughput*, también tienen una gran latencia (del orden de milisegundos). Por lo tanto, para minimizar el tiempo de ejecución de un programa usando GPUs, se debe considerar también el tiempo de transferencia de datos a la hora de determinar si el beneficio de computar en menor tiempo lo justifica. Las nuevas versiones de CUDA buscan brindar nuevas herramientas para simplificar este requerimiento, proveyendo espacio de direccionamiento único y memoria unificada [13], pero siguen siendo copias de memoria a través de los buses (aunque asincrónicas).

Estas características limitan enormemente la clase de problemas que una GPU puede afrontar, y suelen ser una buena heurística para determinar de antemano si vale la pena invertir el tiempo necesario para la implementación y el ajuste fino.

### 2.1.10. Diferencia entre CPU y GPU, procesadores especulativos

Hasta ahora, solo se consideraron a las GPUs de forma aislada, observando las prestaciones del hardware y una aproximación a la manera en que se escriben los programas para esta arquitectura. La esencia de la GPU se puede apreciar mejor comparándola contra los motivos de la evolución de CPU, y analizando los problemas que se fueron enfrentando los diseños siguiendo la historia de los componentes que fueron apareciendo en éstos.

Lo clave es observar el siguiente patrón que se da en el universo CPU: “*no desechar algo que pudieramos necesitar pronto*”, “*intentar predecir el futuro de los condicionales*”, “*intentar correr múltiples instrucciones a la vez porque puede llegar a bloquear alguna de ellas*”.

Todos estos problemas han convertido al CPU en un dispositivo que gira alrededor de la especulación de los valores futuros que pueden tener las ejecuciones y de la probable reutilización de datos. En un CPU moderno (por ejemplo, el Intel Xeon E7-8800 [24]) las unidades que verdaderamente realizan las operaciones lógico-aritméticas (las ALU) son muy pocas en comparación con la cantidad utilizadas para las operaciones de soporte.

En contraste, los dispositivos GPU son verdaderos procesadores de cómputo masivo. Están diseñados para resolver constantemente operaciones muy bien definidas (instruccio-

nes de punto flotante con precisión simple). Comparativamente con una CPU, las ALU de las GPU son bastante pobres y lentas. No funcionan a las mismas velocidades de clock (rára vez superan 1.1 GHz y sus SPs deben estar sincronizados entre sí. Pero la gran ventaja se encuentra en la cantidad.

Una CPU cuenta con pocas ALU por core, dependiendo de la cantidad de cores y del tamaño de sus operaciones SIMD, suele ser alrededor de 16 cores por *die* de x86 es el tope de línea ofrecido actualmente, procesando de a 32 bytes simultáneamente. Una GPU cuenta con miles de ALUs en total (más de 2500 CUDA cores en una **Tesla K20** [12]). El diseño de esta arquitectura concibe la escalabilidad cuantitativa de las unidades de cómputo como la característica esencial a tener, tanto por su énfasis fundamental, las aplicaciones gráficas, como para su aspecto de coprocesador numérico de propósito general.

Por contrapartida, las GPUs disponen de pocas unidades de soporte del procesamiento. Éstas no disponen de pipelines especulativos, el tamaño de las caches son mucho más pequeñas que las de una CPU, la latencia a las memorias principales de la GPU están a centenas de clocks de distancia, etc. La arquitectura supone que siempre va a tener más trabajo disponible para realizar, por lo cual, en vez de intentar solucionar las falencias de un grupo de *threads*, directamente pone al grupo en espera para más adelante y continúa procesando otro *warp* de *threads*. Se puede notar que durante el diseño de la arquitectura CUDA, buscaron resolver el problema del cómputo masivo pensando en hacer más cuentas a la vez recalculando datos, si fuera necesario. Esto es una marcada diferencia con respecto a los CPU, que están pensados en rehacer el menor trabajo posible e intentar mantener todos los datos que pueda en las memorias caches masivas.

Nuevamente, en este punto se puede apreciar el legado histórico de los CPU. Al tener que poder soportar cualquier aplicación, no pueden enfocarse de lleno en una sola problemática. Pero con las arquitecturas GPU, el hecho de no tener que diseñar un procesador de propósito general compatible con versiones anteriores, permitió un cambio radical a la hora de concebir una arquitectura de gran *throughput* auxiliar al procesador, no reemplazándolo sino más bien adicionando poder de cómputo [25].

Las arquitecturas Tesla, Fermi y Kepler conciben el diseño de un procesador de alto desempeño. Su meta principal es poder soportar un alto nivel de paralelismo mediante el uso de procesadores simétricos, pero tomando la fuerte restricción de “*no siempre tiene que andar bien*”. Es decir, los diseñadores suponen que el código que van a ejecutar está bien adaptado a la arquitectura y no disponen casi de mecanismos en el procesador para dar optimizaciones post-compilación. Relajar esta restricción permite romper con el modelo de cómputo de CPU y definir nuevas estrategias de paralelismo, que no siempre se adaptan bien a todos los problemas, pero para el subconjunto de los desafíos que se presentan en el área de HPC y de video juegos han probado ser un cambio paradigmático.

### 2.1.11. Idoneidad para la tarea

El problema enfrentado en este trabajo cuenta con múltiples operaciones matemáticas y gran volumen de cálculo. En particular, las operaciones del cálculo de funcionales constituyen los principales cuellos de botella en la aplicación analizada.

Para obtener los valores numéricos de densidad buscados en los distintos puntos, se deben obtener las derivadas primera y segunda, lo cual implica hacer múltiples operaciones de multiplicación matricial. Este tipo de problemas está estudiado fuertemente en la literatura debido a la multiplicidad de aplicaciones de diferentes campos que requieren de operaciones de álgebra lineal.

Como LIO es un proyecto de resolución numérica de QM/MM, los problemas enfrentados son casi, en su totalidad, operaciones de punto flotante.

Luego, dadas las características de contar con un fuerte nivel de paralelismo en los cuellos de botella y de ser operaciones mayormente de punto flotante, se determinó que el uso de GPGPU para este problema era promisorio, en comparación con arquitecturas de propósito general con menos poder de cómputo. La exploración original de esta arquitectura trajo buenos resultados [4], por lo que se prosiguió su análisis como un camino prometedor [26].

### 3. HERRAMIENTAS

#### 3.1. Herramientas

En esta sección vamos a mencionar las distintas herramientas que se utilizaron para intentar realizar la traducción automática del código de los funcionales de Libxc para que se puedan ejecutar en GPU. Dado que estamos intentando realizar una traducción automática de código, necesitamos herramientas que generen código para arquitecturas de hardware específicas (en nuestro caso para CUDA). Una de las más conocidas es el conjunto de herramientas provistas por LLVM. Se optó por utilizar LLVM por varias razones, las cuales vamos a describir más adelante. Se va a explicar qué es el compilador `clang` y su conjunto de bibliotecas, que son de especial interés para este trabajo. Por último, vamos a profundizar en la herramienta utilizada para generar el código de máquina específico para la arquitectura CUDA a través del uso del compilador `llc`.

##### 3.1.1. LLVM

La infraestructura del compilador LLVM [27] tiene sus orígenes en la Universidad de Illinois y fue desarrollado con el objetivo de tener un compilador moderno que soporte simultáneamente compilación estática y dinámica para lenguajes de programación arbitrarios. El proyecto LLVM comenzó en el año 2000 bajo la supervisión de Chris Lattner y Vikram Adve. El nombre LLVM proviene de *low level virtual machine*, pero a medida que crecía el alcance del proyecto, fue modificado para no generar confusión dado que el proyecto tenía muy poco que ver con las máquinas virtuales tradicionales. Hoy en día, LLVM es el nombre que se utiliza para denotar todo el conjunto de productos relacionados con el proyecto.

LLVM es un proyecto de código abierto, implementado en C++, que se puede utilizar bajo la licencia “UIUC” BSD-style. Es multiplataforma y funciona tanto en Windows, Mac, Linux, como en Solaris. Dentro de la familia de proyectos de LLVM, podemos encontrar varios subproyectos derivados de éste que son utilizados tanto en aplicaciones de código abierto como así también en muchos proyectos cerrados. Un ejemplo es el compilador `nvcc` de Nvidia, el cual está basado en LLVM.

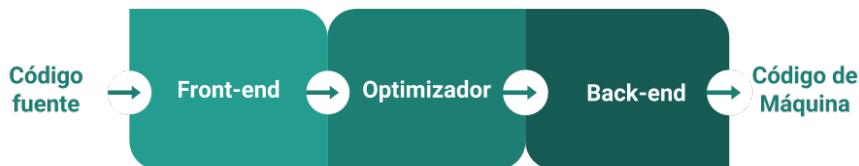

Fig. 3.1: Ejemplo de un diseño de tres fases tradicional.

Desde sus comienzos en el año 2000, LLVM fue diseñado como un conjunto de bibliotecas, enfatizando el desarrollo de interfaces bien definidas. LLVM utiliza el tradicional diseño

de compilación de tres fases, las cuales consisten en un *front-end*, un *optimizador* y un *backend*, tal como se muestra en el diagrama de la figura 3.1.

La representación interna (RI) de LLVM es un conjunto de instrucciones virtuales de bajo nivel similares a RISC (que a su vez es muy similar al código assembler). La RI del código fuente de un lenguaje de programación compilado con LLVM está diseñada para proveer optimizaciones y análisis de código a un nivel intermedio. En el código 3.1, se puede ver un pequeño ejemplo de código LLVM en formato de RI correspondiente al código C del listado 3.2.

```

define i32 @add(i32 %a, i32 %b) {

entry:

%tmp1 = add i32 %a, %b

ret i32 %tmp1

}

```

Listing 3.1: Ejemplo de código RI

```

unsigned add(unsigned a, unsigned b) {

return a+b;

}

```

Listing 3.2: Ejemplo de código C

El diseño de LLVM hace posible definir las tareas de las tres fases de manera clara. El *front-end* realiza la tarea de pre-procesamiento (como en el caso de la familia de lenguajes C), el análisis léxico, el parseo y las validaciones semánticas. Luego de este proceso, convierte el código fuente a código RI (en esta etapa el código no tiene por qué ser optimizado). En el siguiente paso del proceso, el optimizador recibe el código RI, le aplica optimizaciones y envía el resultado al *back-end*. El *back-end* convierte el código RI a código de máquina o a *byte-code* dependiendo de la arquitectura para la cual se quiere generar el código final.

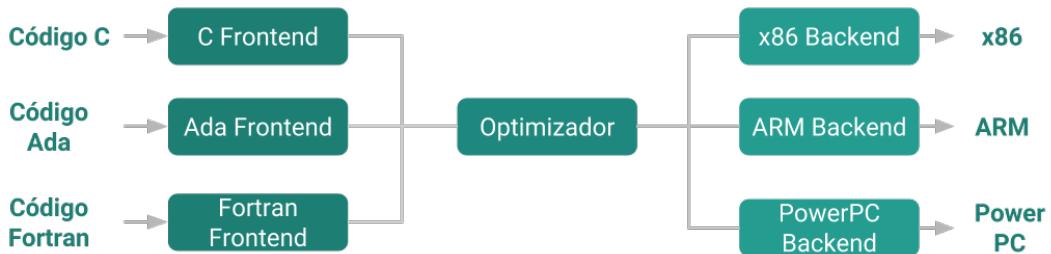

Un efecto de este diseño es que cuando se crea un nuevo *front-end* en LLVM para un nuevo lenguaje, puede que ya exista un optimizador y uno o varios *back-ends* disponibles. Por ejemplo, se puede compilar un nuevo lenguaje A para las arquitecturas de destino B, C y D, si existen *back-ends* en LLVM para B, C y D. Esto se ilustra en la figura 3.2, los únicos requisitos para crear un nuevo *front-end* son que el lenguaje de entrada pueda ser representado en código RI. Este proceso también funciona a la inversa: cuando se crea un nuevo *back-end*, cada lenguaje de programación que cuenta con una implementación de LLVM puede ser compilado para ese *back-end*. El diseño también implica que una implementación de una nueva optimización afectará a todos los lenguajes de programación que tengan implementado un *front-end* y un *back-end* en LLVM, lo cual resulta en un alto grado de reutilización de código. Este diseño reduce drásticamente el esfuerzo de desarrollo requerido para crear un nuevo compilador, dado que la mayoría del trabajo ya se encuentra realizado.

## Optimizaciones

Las arquitecturas de la CPU como de las GPU presentan diferencias sustanciales debido a que realizan trabajos diferentes. Por ejemplo, las CPU puede realizar operaciones típicas como ser, predicciones de saltos o ejecuciones fuera de orden, pero en cambio, las GPUs no realizan ninguna de estas operaciones. Debido a estas diferencias, las optimizaciones pensadas para una CPU pueden no ser adecuadas para una GPU.

LLVM provee varias optimizaciones generales para GPU y también realiza optimizaciones específicas para las GPUs de arquitectura CUDA. A continuación describimos las optimizaciones más importantes que presenta LLVM para GPU,

- Optimizaciones escalares directas: esta optimización elimina la redundancia en el código.

- Inferir espacios de memoria: esta optimización ayuda a inferir los espacios de memoria de una dirección de memoria, de esta manera el *backend* puede emitir *loads* y *stores* de manera más rápida.

- Eliminación de ciclos y funciones en línea: la eliminación de ciclos y el reemplazo de funciones en línea es mucho más importante en la optimización de código para GPU que para CPU, esto se debe a que los saltos en el código de la GPU tienden a ser más costosos.

- Análisis de alias en espacios de memoria: el análisis de alias asegura que no existan dos punteros apuntando a la misma dirección de memoria.

- Divisiones de 64 bits: la división de enteros de 64 bits es mucho más lenta que la división de enteros de 32 bits para las GPUs de NVidia. Esta optimización intenta determinar si el divisor y el dividendo pueden, siempre que sea posible, representarse con un número de 32 bits en tiempo de ejecución.

Fig. 3.2: Módulos en el diseño de tres fases.

### 3.1.2. Clang

**Clang** es uno de los subproyectos de LLVM que fue creado para ser un *front-end* para varios de los lenguajes de la familia C. Es compatible con los lenguajes C, C++, **objective C** y **objective C++**. Está diseñado para ser compatible con **gcc** y también puede ser utilizado como su reemplazo directo, lo que simplifica una migración de **gcc** a **Clang**. La arquitectura basada en bibliotecas propuesta para **Clang**, permite que los nuevos desarrolladores puedan contribuir sin que deban tener conocimiento alguno de la base de código completa, solo necesitan tener conocimiento de la parte en la que están trabajando.

**Clang** provee soporte para varios frameworks como **OpenMP**, **OpenCL** y provee extensiones de lenguajes para **CUDA** de Nvidia. Este último soporte es el que vamos a utilizar para poder realizar una traducción del código de los funcionales de **Libxc** a código que se ejecute directamente en la placa de video.

### 3.1.3. LLC

Dentro del conjunto de herramientas que trae LLVM se encuentra el compilador `llc`, que se encarga de compilar código intermedio generado con `Clang` a código assembler de un arquitectura específica. El código assembler generado con esta herramienta puede ser compilado nuevamente con herramientas de assembler y linkers nativos del lenguaje para generar un archivo ejecutable.

Para el presente trabajo, vamos a utilizar el compilador `llc` en la etapa final de la traducción del código de los funcionales de Libxc para generar el código assembler para CUDA (`nvptx`), linkearlo y generar los archivos ejecutables. De esta manera vamos a intentar definir un procedimiento automático para la traducción de código que se ejecuta en CPU a código listo para ser ejecutado en GPU.

## 4. IMPLEMENTACIÓN

### 4.1. Implementación existente

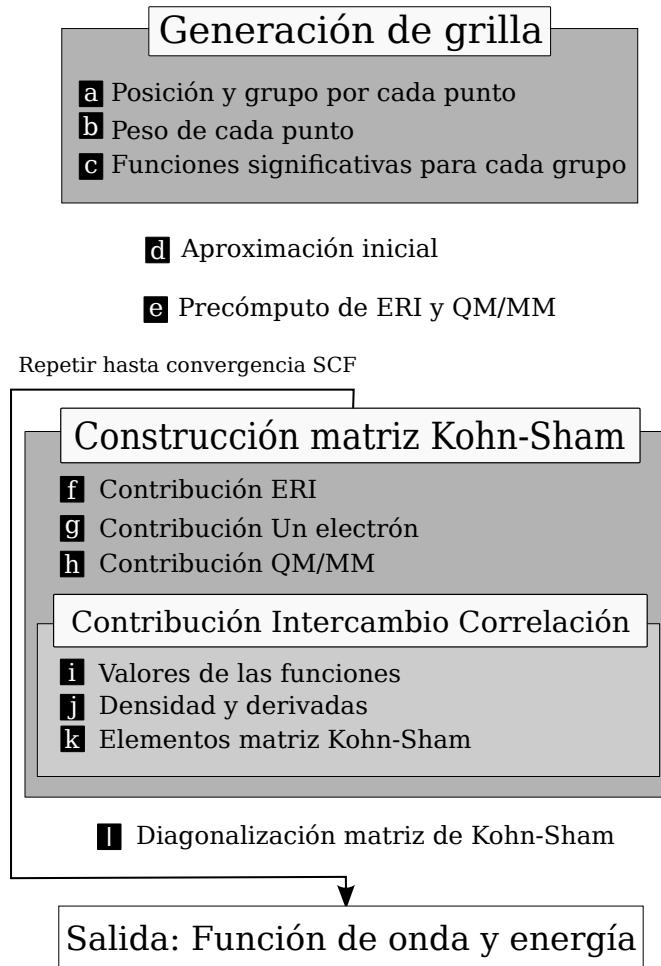

Antes de describir las modificaciones realizadas sobre la aplicación existente, nos centraremos en los pasos que componen la obtención de la función de onda mediante la construcción de la matriz de Kohn-Sham.

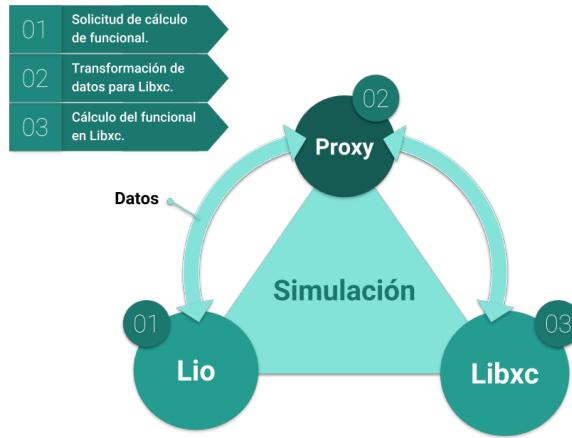

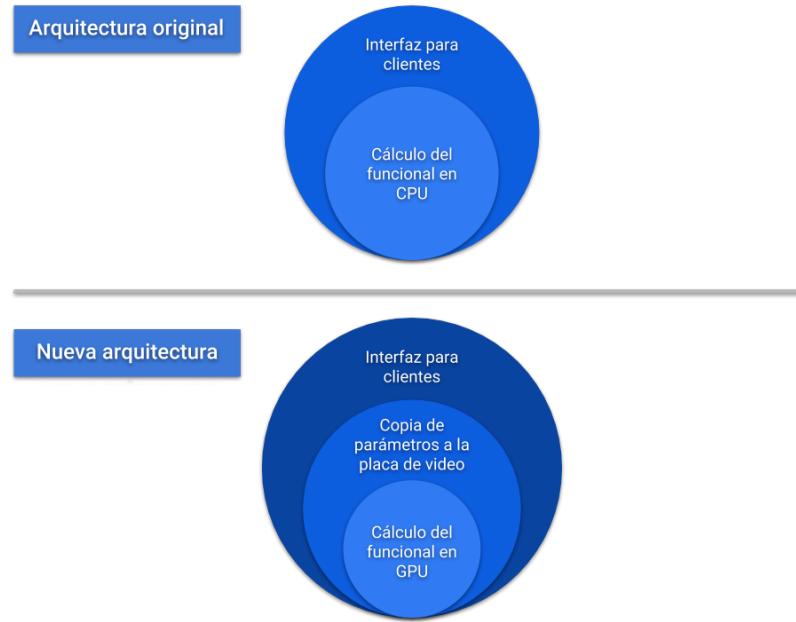

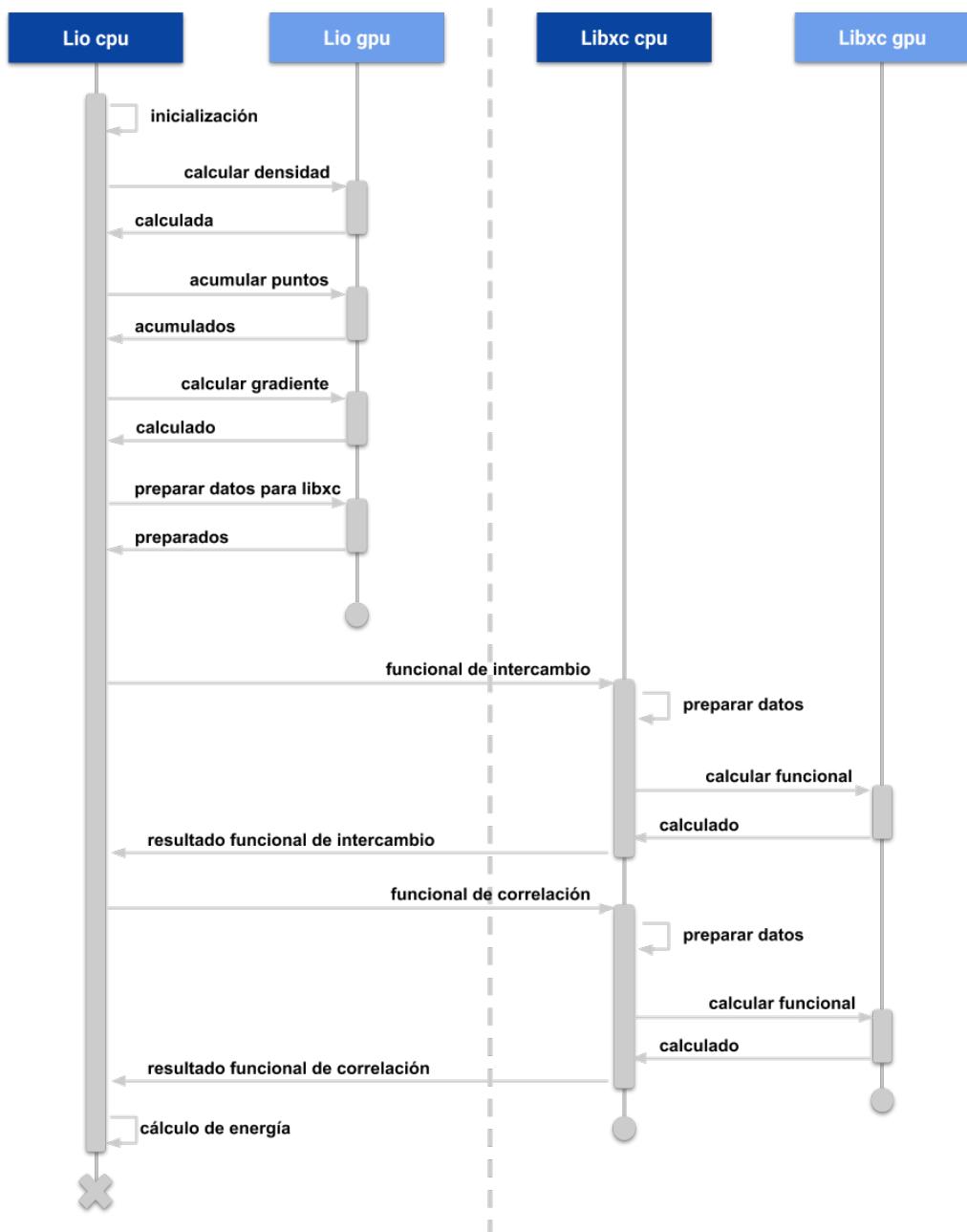

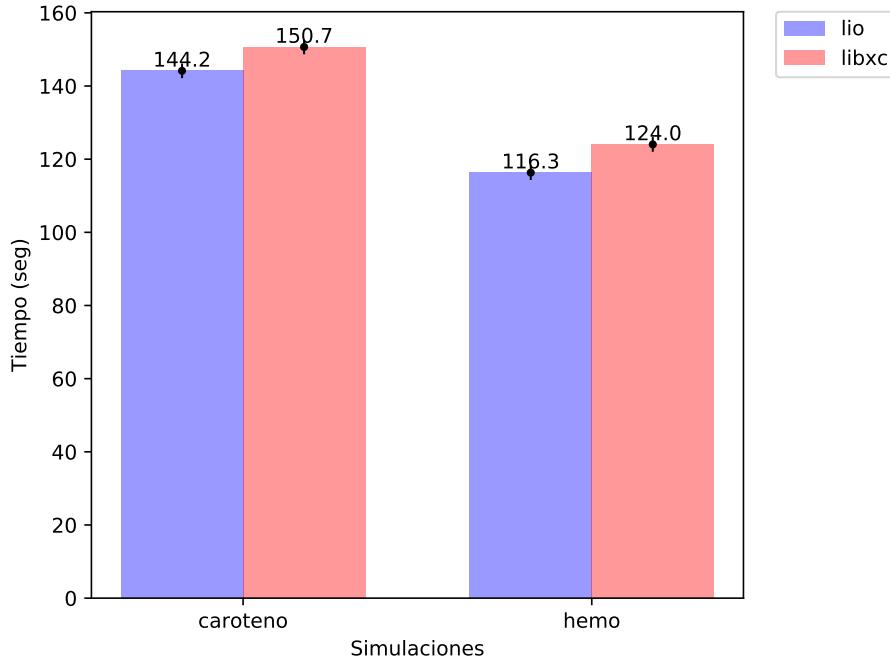

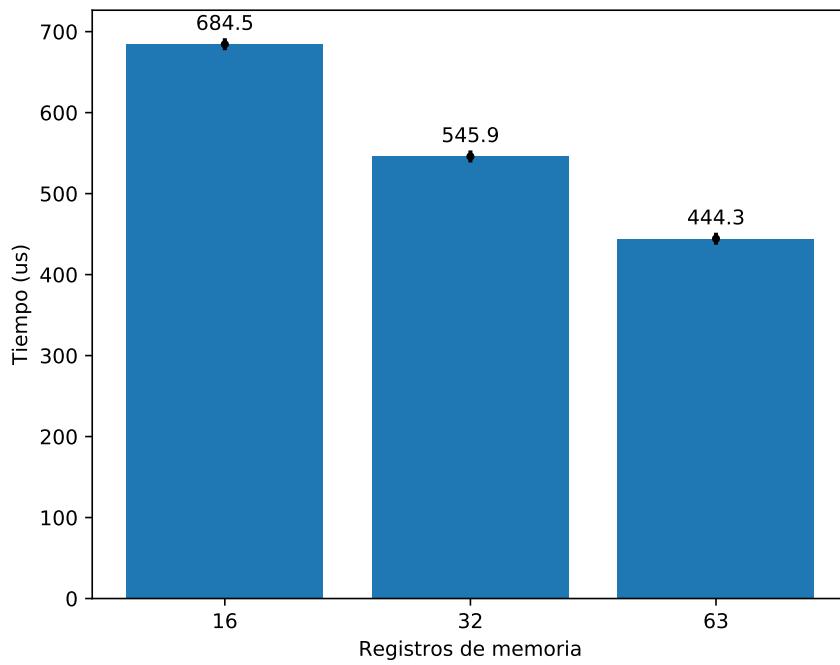

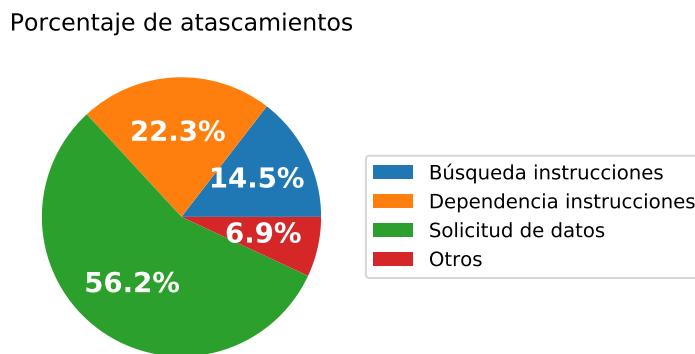

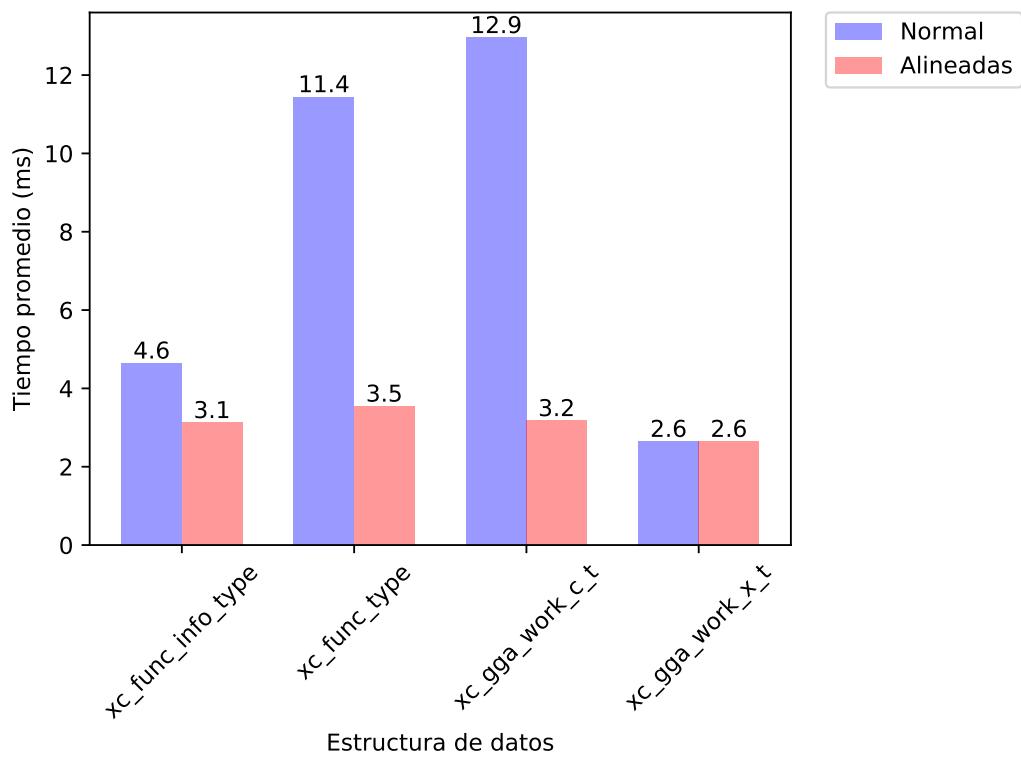

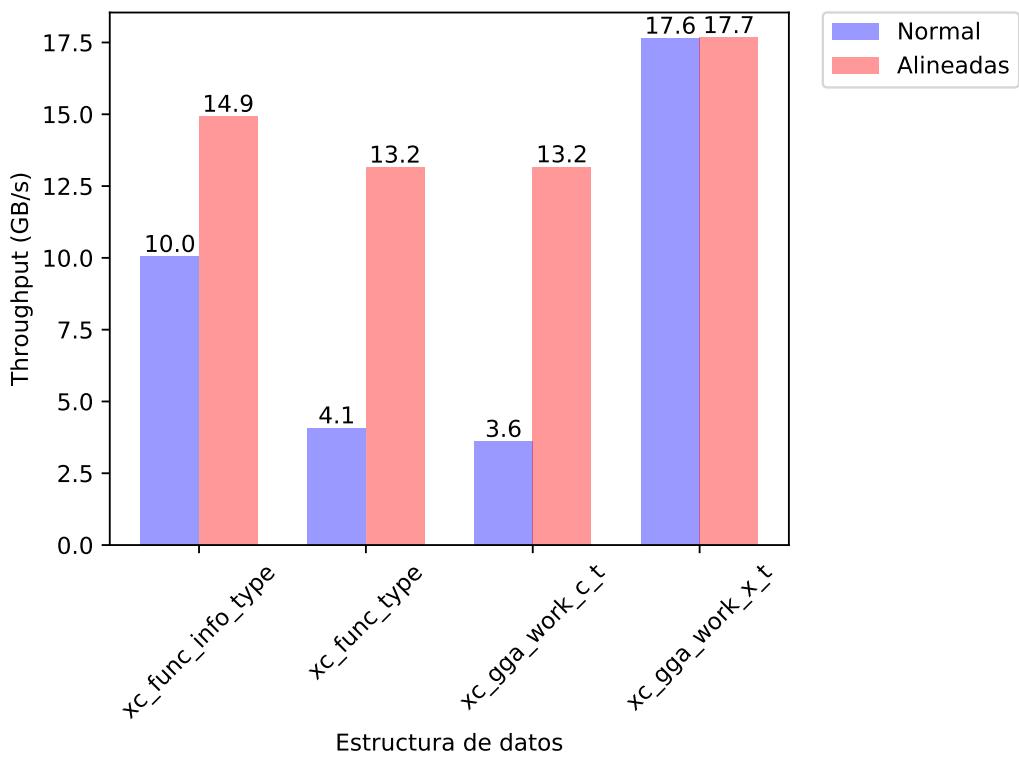

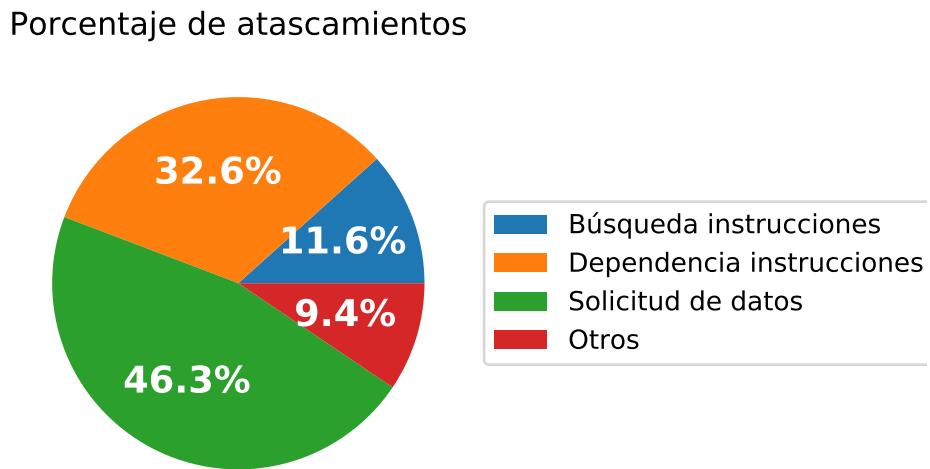

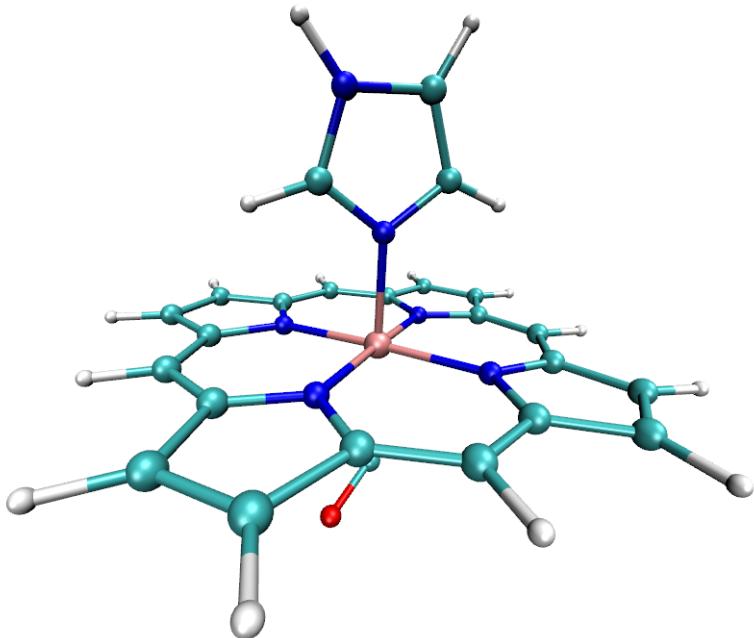

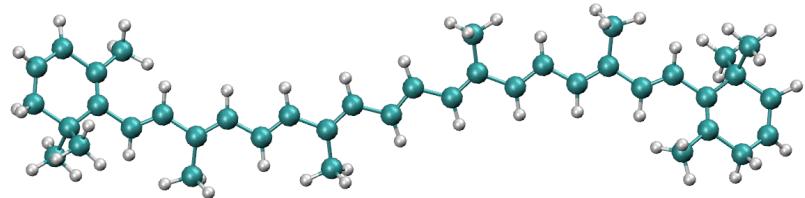

Fig. 4.1: Pasos del cálculo de DFT realizado por LIO.