UNIVERSIDAD DE BUENOS AIRES

FACULTAD DE CIENCIAS EXACTAS Y NATURALES

DEPARTAMENTO DE COMPUTACIÓN

# Avances en el uso eficiente de sistemas multi-softcores en FPGAs

Tesis de Licenciatura en Ciencias de la Computación

Daniel Claverino

Director: David Alejandro González Marquez

Codirector: Esteban Mocskos

Buenos Aires, 2023

## Resumen

Desde hace años, el avance tecnológico en la fabricación de circuitos integrados ha permitido implementar múltiples procesadores en una misma pastilla con una creciente cantidad de núcleos, memoria e, inclusive, contener unidades funcionales con distinto grado de especialización. Sin embargo, a la hora de resolver problemas específicos, los procesadores de propósito general pueden ser superados por **aceleradores**, que son sistemas especialmente diseñados. Los más comunes son los aceleradores de vídeo que permiten, por ejemplo, procesar imágenes o descomprimir un flujo (*stream*) de vídeo de forma muy eficiente.

Las **FPGAs** (*Field-Programmable Gate Array*) surgen como plataformas que permiten implementar soluciones de hardware programable, es decir, hardware que puede ser modificado o rediseñado por el usuario sin necesidad de reemplazar el circuito integrado. Consisten en una grilla de celdas de distinta especialización que pueden conectarse de diversas formas, resultando en una plataforma con alta flexibilidad.

Las FPGAs resultan un camino válido para el diseño, prototipado y construcción de hardware y, en particular, aceleradores. Siempre dentro de sus limitaciones de recursos, permiten implementar hardware y se puede lograr un alto grado de paralelismo.

Dado este nivel de flexibilidad, un componente que se implementa en FPGA recibe el nombre de **softcore**. Estos pueden ir desde una máquina de estados o un sumador, hasta procesadores multi-core con varios niveles de cache. El límite dependerá de la cantidad de celdas y las formas de conexión disponibles, que es fija para una FPGA dada.

El presente trabajo busca avanzar en técnicas que permitan el uso eficiente de múltiples *softcores* dentro de una FPGA, proponiendo un *framework* que permitirá estudiar distintos sistemas de procesamiento. Haremos especial uso del **MicroBlaze**, uno de los *softcores* más utilizados, desarrollado por Xilinx y creado específicamente para su uso en FPGAs.

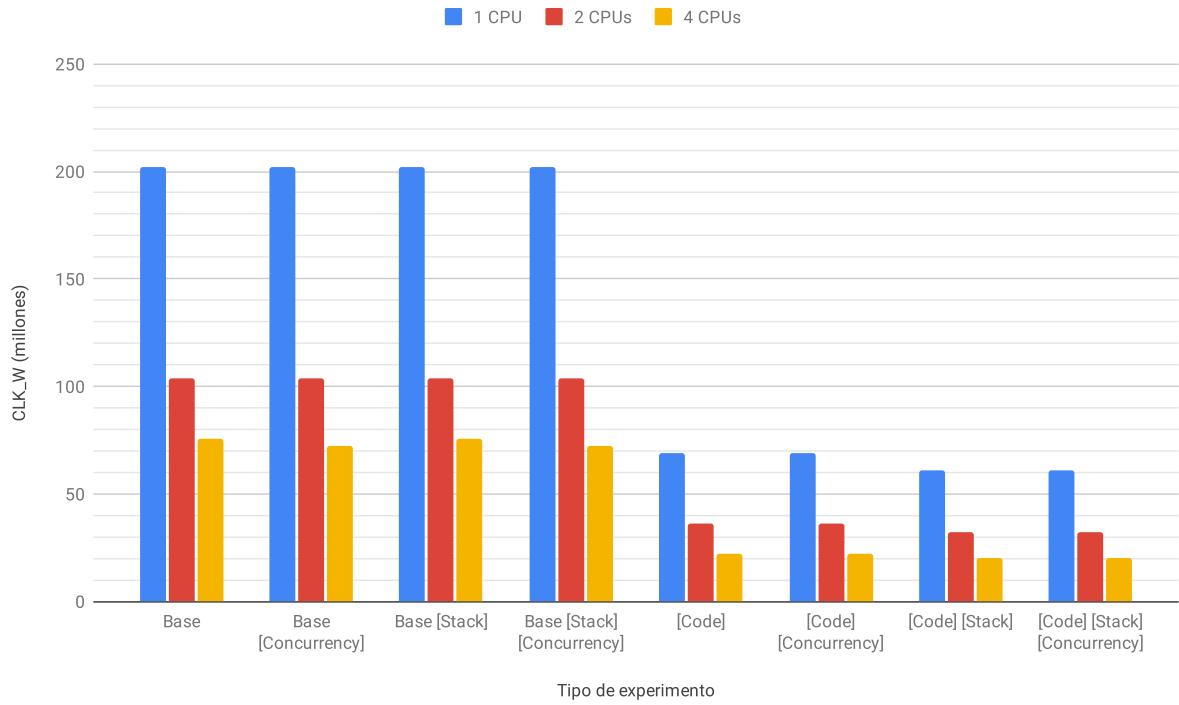

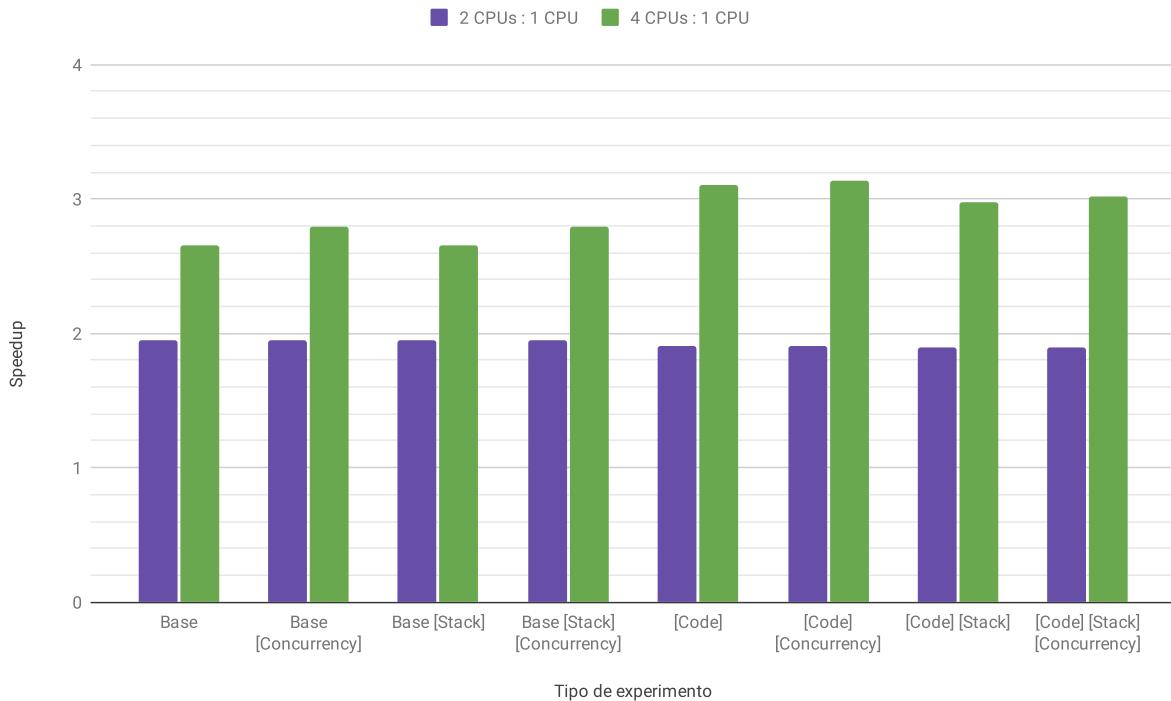

Una de las principales limitaciones de los sistemas basados en *softcores* es el acceso a memoria. Partiendo de este punto y utilizando bloques RAM de FPGA (BRAM), se propone estudiar un conjunto de estrategias de uso de la memoria: usar el *stack* en BRAM, correr código del programa en BRAM, y correr código de funciones de sincronización en BRAM. Esto implica ejecutar programas cuyos accesos a memoria utilizan distintas memorias, cada una con características distintas (BRAM y Cache+DDR).

Respecto a las tres formas de uso de BRAM propuestas, notamos que mover y correr código de funciones de sincronización en BRAM no genera mejoras significativas salvo en casos donde hay muchos llamados o varios procesadores en espera. Dependiendo del algoritmo y su implementación, usar el stack en BRAM puede ir desde tener poco efecto a tener un impacto significativo en el desempeño, por encima de mover las funciones de sincronización. Finalmente, mover y correr código del algoritmo en BRAM genera el mayor impacto positivo en el rendimiento. Este impacto puede verse reducido si hay partes del código de uso frecuente que no se han movido a BRAM y continúan en memoria principal.

Tener control del hardware nos permite implementar soluciones que se ajusten al problema a resolver. Trabajar desde una capa de abstracción baja implica que los desarrolladores deben manejar detalles de muy bajo nivel, como los procesadores mismos, su interconexión, y la distribución de memoria utilizando distintos tipos de memoria.

**Palabras claves:** FPGA, SMP, BRAM, *softcore*, MicroBlaze, memoria, cache, *stack*, *spin-lock*, performance.

## Abstract

For years, technological advances in the manufacture of integrated circuits have allowed the implementation of multiple processors on the same chip with an increasing number of cores, memory, and even functional units with different degrees of specialization. However, when it comes to solving specific problems, general-purpose processors can be outperformed by accelerators, which are specially designed systems.

The most common are video accelerators that allow, for example, to process images or decompress a video stream very efficiently.

**FPGAs** (*Field-Programmable Gate Array*) are platforms allowing programmable hardware implementation. The user can modify or redesign this hardware while using the same chip. FPGAs are composed of a variety of specialized cells distributed on a grid. These cells can be connected in different ways, resulting in a highly flexible platform.

FPGAs are a valid path for hardware design, prototyping, and implementation. It is possible to implement several hardware components within their fixed and limited resources. Their nature favors highly parallel components and efficient access to I/O external events. Accelerators are one such particular piece of hardware.

Given this flexibility, a component implemented on an FPGA is called **softcore**. These can go from a state machine or an adder to a multi-core processor with multiple cache levels, but some restrictions still apply. The number of cells and available connections are fixed on an FPGA limiting what can be implemented.

In this thesis, we aim to study efficient ways of running multiple softcores on an FPGA. We propose a framework that allows studying a wide range of processing systems, and we use it to implement one particular multi-core system. We use Xilinx's MicroBlaze, one of the most widely used softcore and specifically created to be deployed on FPGAs.

One limitation of softcore systems is memory access. Having this in mind, we use RAM Blocks (BRAM) to study different memory usage strategies: point the stack to BRAM, execute program code on BRAM, and execute synchronization code on BRAM. This implies running programs where memory accesses are done to different memory types, each with its characteristics (BRAM and Cache+DDR).

Regarding the three proposed BRAM uses, we found moving and executing synchronization code on BRAM to yield no significant improvements except in heavy synchronization cases or where processors were competing too strongly with memory access. Depending on the algorithm and its implementation, stack on BRAM results ranged from no impact to a significant performance improvement, even over the prior case. Lastly, moving and executing program code on BRAM showed the most positive impact on the performance of the three strategies. The latter's results were reduced when the program was not completely moved to BRAM and frequently executed code was still executed on other memory.

Controlling the hardware lets us implement a specifically designed solution to a problem. Working on a low-abstraction layer implies developers need to handle low-level details, such as processors, the interconnection between them, and memory distribution using different memory types.

**Keywords:** FPGA, SMP, BRAM, softcore, MicroBlaze, memory, cache, stack, spin-lock, performance.

# Agradecimientos

A mi familia, que conozco desde chico y siempre estuvo presente.

A David, mi director de tesis, por la propuesta de investigación, el seguimiento y particularmente el trato humano.

A los profesores de la facultad que me acompañaron en este camino y me incentivarón a aprender más y más.

A los números primos, que no voy a enumerar porque seguramente me olvide alguno.

A mi perro, que no sabe leer pero sí sabe hacerme reír.

*A mi mamá.*

# Índice general

|                                                       |           |

|-------------------------------------------------------|-----------|

| <b>1. Introducción</b>                                | <b>9</b>  |

| 1.1. Motivación . . . . .                             | 12        |

| 1.2. Objetivos del trabajo . . . . .                  | 13        |

| 1.3. Trabajo relacionado . . . . .                    | 13        |

| 1.4. FPGA . . . . .                                   | 15        |

| 1.4.1. Tipos de celdas . . . . .                      | 15        |

| 1.4.2. Interconectividad . . . . .                    | 17        |

| 1.4.3. PL y PS . . . . .                              | 18        |

| 1.4.4. Limitaciones . . . . .                         | 19        |

| 1.4.5. Tipos y usos . . . . .                         | 19        |

| 1.4.6. Diseño . . . . .                               | 20        |

| 1.5. Plataforma . . . . .                             | 23        |

| 1.5.1. Hardware . . . . .                             | 23        |

| 1.5.2. Vivado . . . . .                               | 23        |

| 1.5.3. MicroBlaze . . . . .                           | 24        |

| 1.5.4. Otras herramientas . . . . .                   | 26        |

| <b>2. Infraestructura desarrollada</b>                | <b>28</b> |

| 2.1. Arquitectura . . . . .                           | 28        |

| 2.2. Arquitectura (Hardware) . . . . .                | 30        |

| 2.2.1. Uso de Memoria . . . . .                       | 31        |

| 2.2.2. MicroBlaze . . . . .                           | 32        |

| 2.2.3. Cache L2 . . . . .                             | 34        |

| 2.2.4. Softcore AXI Controller . . . . .              | 35        |

| 2.2.5. Softcore Controller . . . . .                  | 38        |

| 2.2.6. Consideraciones . . . . .                      | 41        |

| 2.3. Arquitectura (Software) . . . . .                | 43        |

| 2.3.1. Programas . . . . .                            | 45        |

| 2.3.2. Compilación . . . . .                          | 48        |

| 2.3.3. Generación de Comandos . . . . .               | 49        |

| 2.3.4. Preparación para ejecución . . . . .           | 53        |

| 2.3.5. Ejecución . . . . .                            | 54        |

| 2.3.6. Chequeo y parseo de resultados . . . . .       | 57        |

| <b>3. Algoritmos y experimentos</b>                   | <b>58</b> |

| 3.1. Técnica . . . . .                                | 58        |

| 3.2. Algoritmos trivialmente paralelizables . . . . . | 64        |

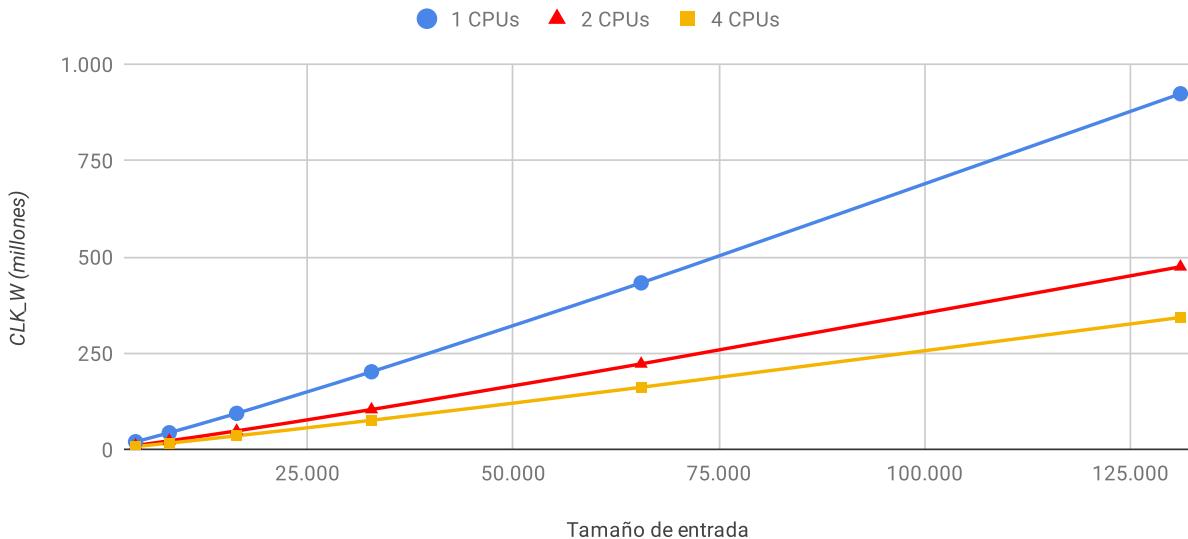

| 3.2.1. Experimentos . . . . .                         | 65        |

| 3.2.2. Resultados y Análisis . . . . .                | 66        |

|                                             |            |

|---------------------------------------------|------------|

| 3.2.3. Conclusión . . . . .                 | 73         |

| 3.3. Multiplicación de matrices . . . . .   | 74         |

| 3.3.1. Técnica de paralelizado . . . . .    | 75         |

| 3.3.2. Experimentos . . . . .               | 76         |

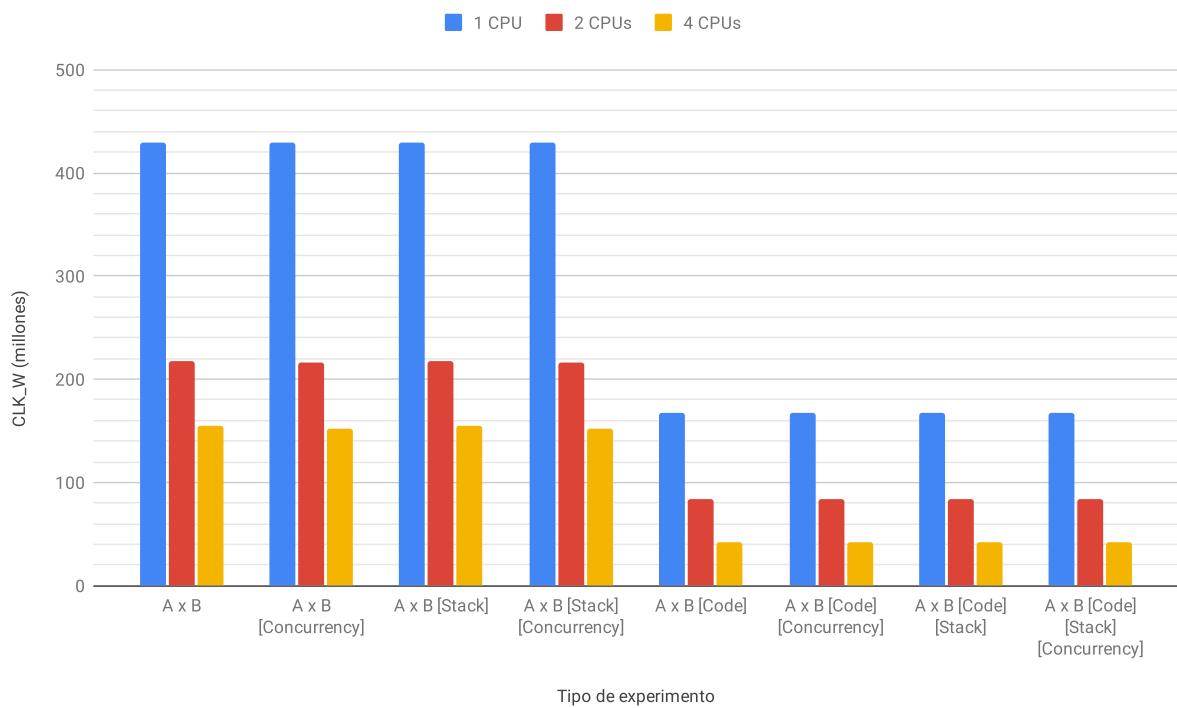

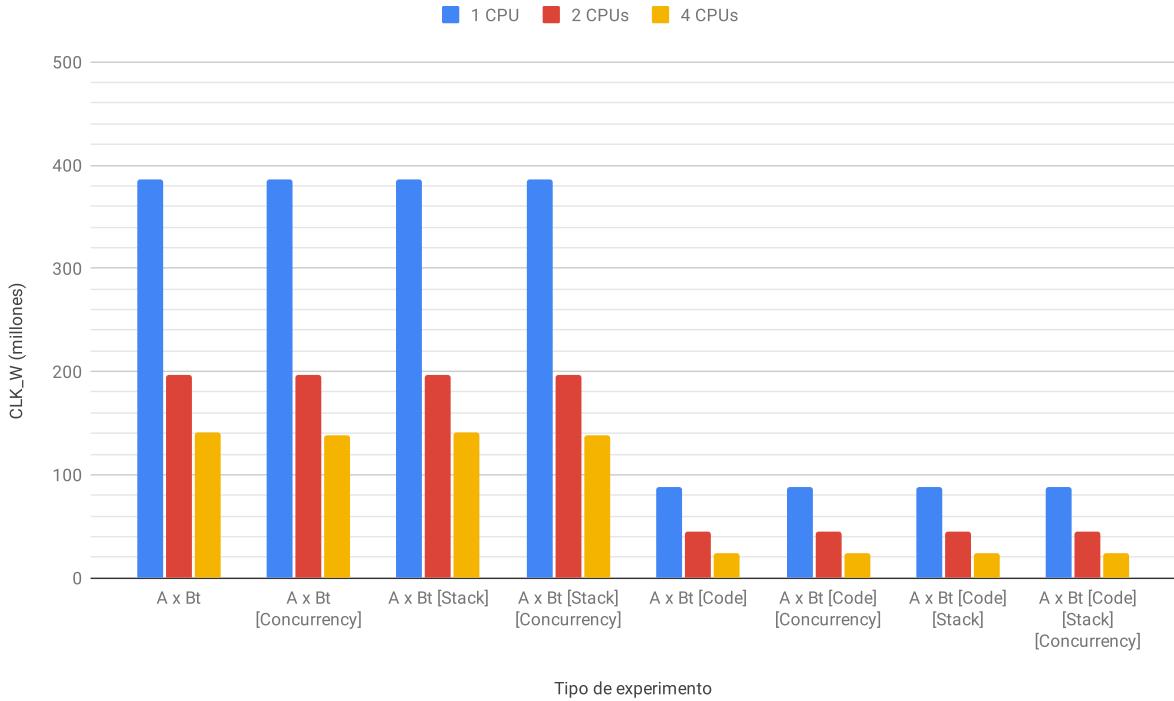

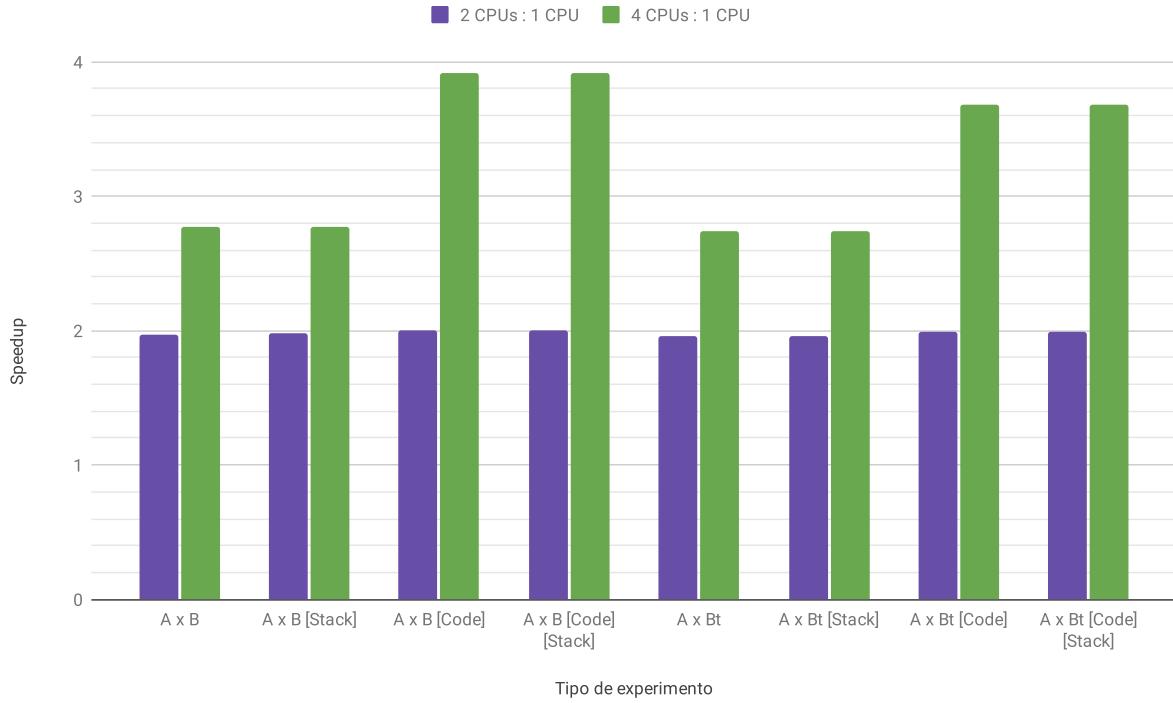

| 3.3.3. Resultados . . . . .                 | 76         |

| 3.3.4. Conclusión . . . . .                 | 79         |

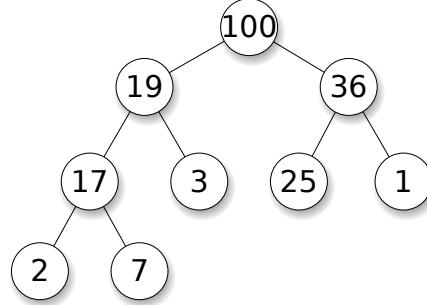

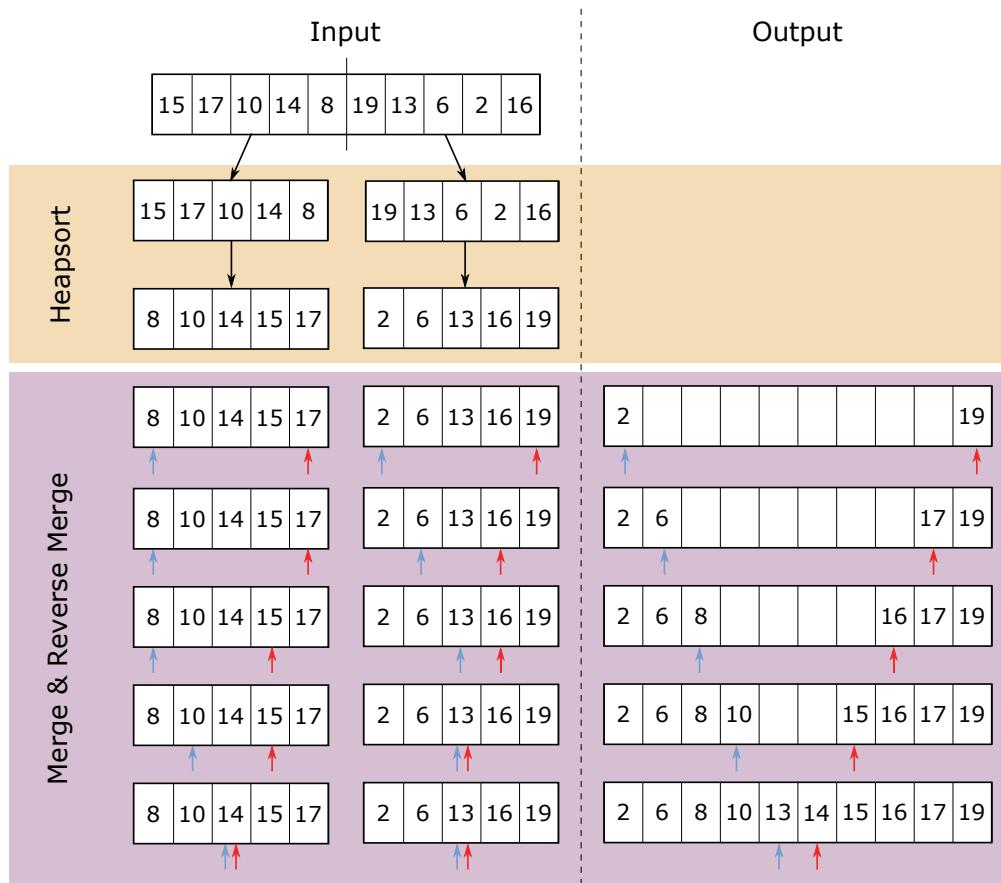

| 3.4. Heapsort . . . . .                     | 81         |

| 3.4.1. Técnica de paralelización . . . . .  | 83         |

| 3.4.2. Experimentos . . . . .               | 84         |

| 3.4.3. Resultados . . . . .                 | 84         |

| 3.4.4. Conclusión . . . . .                 | 87         |

| 3.5. FFT - Fast Fourier Transform . . . . . | 88         |

| 3.5.1. Introducción . . . . .               | 88         |

| 3.5.2. Técnica de paralelización . . . . .  | 89         |

| 3.5.3. Funciones intrínsecas . . . . .      | 94         |

| 3.5.4. Experimentos . . . . .               | 94         |

| 3.5.5. Resultados y análisis . . . . .      | 96         |

| 3.5.6. Conclusión . . . . .                 | 101        |

| 3.6. Resumen . . . . .                      | 102        |

| <b>4. Conclusiones</b>                      | <b>103</b> |

| 4.1. Futuro trabajo . . . . .               | 104        |

# Capítulo 1

## Introducción

El avance tecnológico en la fabricación de circuitos integrados permite alcanzar niveles de integración cada vez mayores, permitiendo implementar múltiples procesadores en una misma pastilla con mayor cantidad de núcleos, memoria, o incluso mejores interfaces. Estos procesadores pueden ser de propósito general o incluso tener diferente grado de especialización dentro de un sistema de cómputo heterogéneo, optimizando su uso para reducir el gasto energético. Algunos de estos cuentan con múltiples unidades funcionales que permiten la ejecución de operaciones en paralelo. Un ejemplo paradigmático son las instrucciones vectoriales, clasificadas como SIMD (*Single Instruction Multiple Data*), que permiten aplicar la misma operación a varios elementos de un vector simultáneamente. Otros cuentan, incluso, con instrucciones especiales para cálculos no triviales, como por ejemplo encriptación, descompresión, o incluso para el procesamiento de audio y video. También, pueden llegar a ejecutar las operaciones fuera de orden, cambiando la secuencia original del programa para poder procesarlas más eficientemente pero de forma tal que se preserve la coherencia entre ellas.

Si bien esto tiende a mejorar los tiempos de cómputo, un procesador de propósito general está diseñado para lidiar con cualquier tipo de carga de trabajo (*workload*) sin considerar sus potenciales características distintivas que podrían permitir alguna clase de optimización. Por eso, a la hora de resolver problemas específicos, los procesadores de propósito general pueden ser superados por sistemas especialmente diseñados para propósitos específicos.

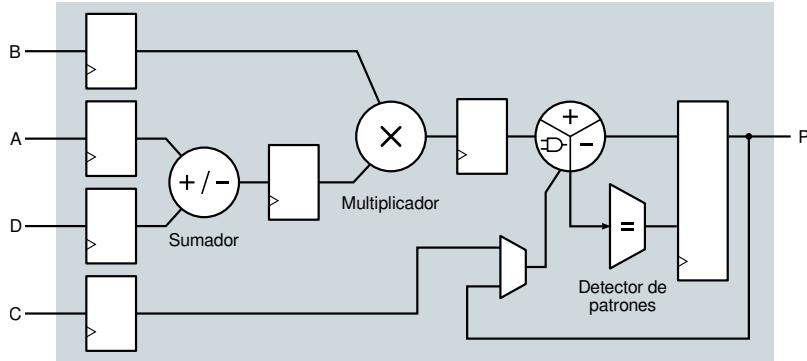

En este lugar entran en juego los **aceleradores**. Los más comunes son los aceleradores de vídeo que permiten, por ejemplo, procesar imágenes o descomprimir un flujo (*stream*) de vídeo de forma muy eficiente sin consumir recursos del procesador principal.

Un acelerador de vídeo contiene una gran cantidad de procesadores que pueden operar simultáneamente, realizando las mismas operaciones sobre una gran cantidad de datos. Esta masiva capacidad de cómputo paralelo resulta muy útil a la hora de trabajar con imágenes o señales, resultando incluso atractiva para otros problemas como muchos de los que aparecen en diferentes áreas del cómputo científico.

No obstante, esta ventaja no es aprovechable en todos los contextos. Por ejemplo, cuando el problema requiere que el código tome distintos caminos para distintas partes de su entrada, es decir, el flujo del programa diverge y para algunas partes de su entrada toma diferentes caminos. Otro caso en los que estos aceleradores no pueden ser aprovechados es cuando la cantidad de datos de entrada a procesar es limitada y los recursos de cómputo que posee son sub-utilizados.

A la hora de diseñar hardware que solucione eficientemente un problema, tenemos que tener en cuenta que el resultado será poco flexible o estará limitado a una familia de problemas. Por ejemplo, un procesador que implementa instrucciones para evaluar funciones de

*hash*, estará limitado a las funciones de *hash* implementadas, algunas de las cuales pueden compartir parte de la implementación. Si se desea cambiar o agregar otras funciones de *hash*, es posible que ya no se pueda hacer uso de la operatoria común a las instrucciones de *hash* ya existentes.

A pesar de todo, el hardware no necesariamente está libre de errores y es posible que se descubran, por ejemplo, problemas de seguridad. Tal es el caso de algunas vulnerabilidades presentes en ciertos procesadores modernos que pueden ser explotadas por Spectre [1] y Meltdown [2]. El hardware, habitualmente, no puede cambiarse una vez que ha sido producido, pero si éste fuera maleable entonces sería posible modificarlo para ajustarse ante estas eventualidades, potencialmente con poco impacto. Dicho esto, vulnerabilidades como las mencionadas, se podrían mitigar con una simple actualización de software, pero con una caída drástica en la desempeño del procesador.

Esta y otras situaciones se vuelven más críticas cuando la tarea que se realiza es muy específica, los límites de desempeño son aún mayores, y el costo del equipo es muy alto, como podría ser una antena de telefonía, un sistema de control de una planta industrial o un sistema de navegación aéreo.

Los **ASICs** (*Application-Specific Integrated Circuits*) suelen ser una forma eficiente y compacta de implementar hardware de propósito específico. Sin embargo, resultan muy rígidos una vez fabricados y sus costos de producción son altos, ya que habitualmente se trata de una relativamente baja cantidad de unidades producidas. Típicamente, utilizan tecnología **MOS** (*metal-oxide-semiconductor*) y pueden manejar circuitos complejos de millones de compuertas lógicas. Un **ASIC** puede llegar a incluir microprocesadores enteros, bloques de memoria, y otras unidades funcionales.

En contraste, las **FPGAs** (*Field-Programmable Gate Array*) consisten en una grilla de celdas de distinta especialización que pueden conectarse de diversas formas, obteniendo un sistema mucho más flexible. Las celdas implementan desde tablas lógicas y bloques de memoria hasta operaciones complejas como multiplicación y acumulación.

Si bien la **FPGA** puede integrarse en un **ASIC**, el *routing* que indica cómo se conectan sus celdas, así como la configuración de cada celda no están fijos. Esta información se almacena y se lee desde una memoria que puede ser modificada, permitiendo alterar la lógica del circuito y su funcionalidad.

Al implementar hardware sobre estas celdas mediante una configuración modificable estamos sacrificando eficiencia a cambio de un enorme grado de flexibilidad, especialmente si se lo compara con la implementación fija de un **ASIC**. A su vez, las **FPGAs** aparecen como una opción extremadamente útil para explorar nuevos diseños y soluciones, ayudando a reducir los costos y tiempos de desarrollo. En contraposición, implementar hardware en una **FPGA** es más complejo que hacerlo directamente en hardware, pero así como existen herramientas para generar una implementación en un **ASIC** a partir de un diseño de alto nivel, también existen herramientas similares que generan una configuración apropiada para que un hardware se implemente en **FPGA**.

Cuando se trata de hardware que está implementado en una **FPGA**, realizar una actualización sería, entonces, una cuestión de cambiar el diseño y permitir que las herramientas calculen el nuevo *routing* y la configuración de celdas adecuada. Es decir, una actualización de hardware se podría lograr mediante una *sencilla* actualización de software.

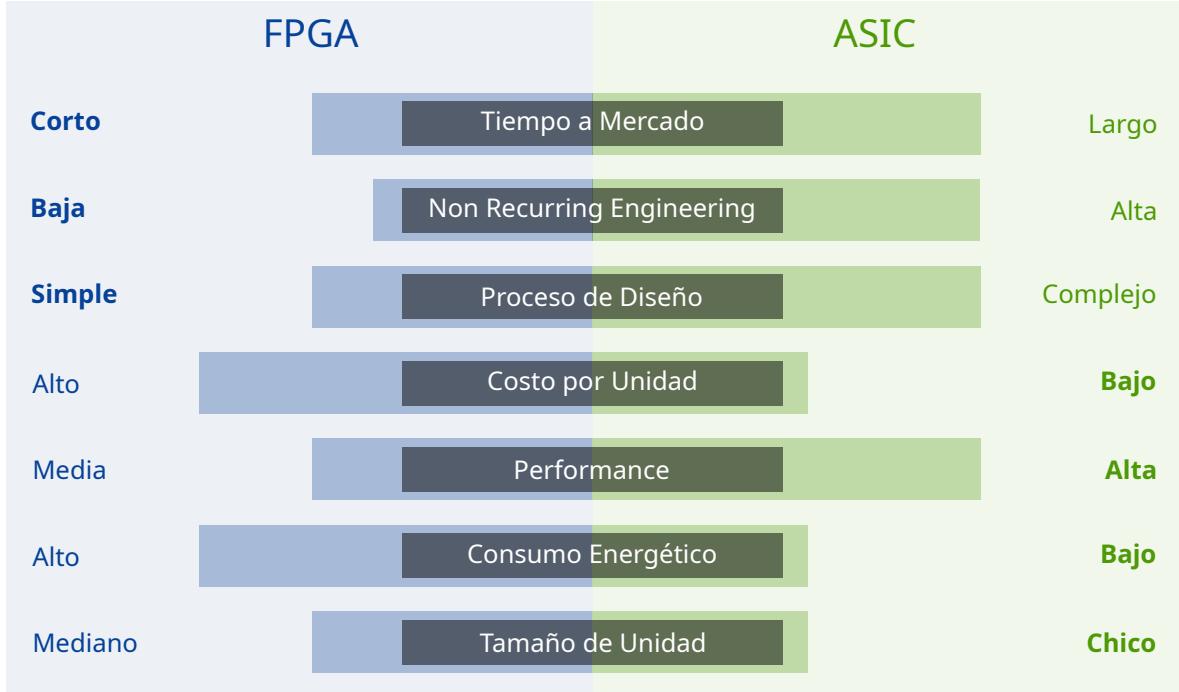

Figura 1.1: Comparación entre **FPGA** y **ASIC**. Se destacan los puntos favorables a cada tecnología en negrita.

En la figura 1.1 podemos ver un diagrama que compara distintas características entre **FPGA** y **ASIC**. Factores como el tiempo a mercado, *non recurring engineering*<sup>1</sup> y el proceso de diseño son puntos favorables de las FPGAs. En cambio, factores como el costo por unidad, la *performance*, el consumo energético y el tamaño de unidad son favorecidos por los **ASIC**.

Dado este grado de flexibilidad, un componente que se implementa en **FPGA** recibe el nombre de **softcore**. Pueden ir desde hardware relativamente simple como puede ser una máquina de estados o un sumador, hasta procesadores *multi-core* con varios niveles de *cache*. El límite dependerá de la cantidad de celdas disponibles, que es fija para una **FPGA** dada.

Supongamos que tenemos un diseño de un componente que puede realizar una tarea de cómputo de manera muy eficiente, de forma tal que un sistema podría hacer la delegación (*offloading*) de la tarea, y quisiéramos explorar distintas variantes de este acelerador usando una **FPGA**. Podríamos utilizar la misma **FPGA** como punto de contacto con el sistema principal y diseñar el hardware necesario para la comunicación.

En este escenario, sería posible que necesitemos de un conjunto de *softcores* para resolver nuestro problema y uno de ellos podría ser un procesador. Al ser un *softcore*, existe la posibilidad de realizarle modificaciones hasta ajustarlo a nuestras necesidades, e incluso actualizarlo si éstas cambian con el tiempo.

Las **FPGAs** resultan un camino válido para el diseño, prototipado y construcción de aceleradores: permiten implementar hardware para realizar el procedimiento que se desee, siempre dentro de sus limitaciones de recursos. Más aún, esto se puede lograr con un alto grado de paralelismo y con la posibilidad de acceder eficientemente a eventos externos de entrada-salida.

---

<sup>1</sup>El costo total de las etapas de creación de un producto: investigación, diseño, desarrollo y testeo.

## 1.1. Motivación

En la actualidad, la mayor parte de los procesadores de uso general son multi-núcleo (*multi-core*). Una manera de aprovecharlos es utilizar algoritmos paralelos, especialmente útiles a la hora de procesar grandes volúmenes de datos.

Existen FPGAs disponibles comercialmente que permiten implementar procesadores *multi-core*, teniendo capacidad suficiente para añadir distintos tipos de unidades funcionales, memoria *cache*, o incluso un *pipeline* de varias etapas.

Algunos de estos procesadores implementables en FPGA están restringidos a una plataforma específica (chips de Xilinx o de Altera, por ejemplo), otros son de código abierto, y algunos están basados en procesadores existentes.

Hajduk [3] da un ejemplo de esto último con el objetivo de correr código aplicativo real y que puede aprovecharse de la flexibilidad de una FPGA. Allí diseñan y analizan tres variantes de un microcontrolador de 8 bits para FPGA basado en la familia PIC16 de Microchip que resulta ser entre 4 y 8 veces más rápido.

Hay diversos trabajos que exploran los usos de una FPGA aplicados a distintos campos.

En el área médica podemos nombrar una implementación basada en RISC-V para aplicaciones biomédicas de bajo consumo por Garcia-Ramirez et al. [4].

Un interesante producto de consumo se propone en el trabajo de Echanobe et al. [5], donde diseñan y evalúan un multiprocesador embebido para controlar parámetros ambientales en una casa inteligente y que aprende de las preferencias del usuario.

Para el área de investigación y desarrollo destacamos el trabajo de Nolting et al. [6] en donde presentan una técnica novedosa de hardware dinámicamente configurable durante la ejecución de un programa, y Liu et al. [7] donde evalúan aceleradores híbridos de hardware para inteligencia artificial con FPGAs.

Estos pocos ejemplos ponen de manifiesto el alcance de soluciones provistas por FPGAs.

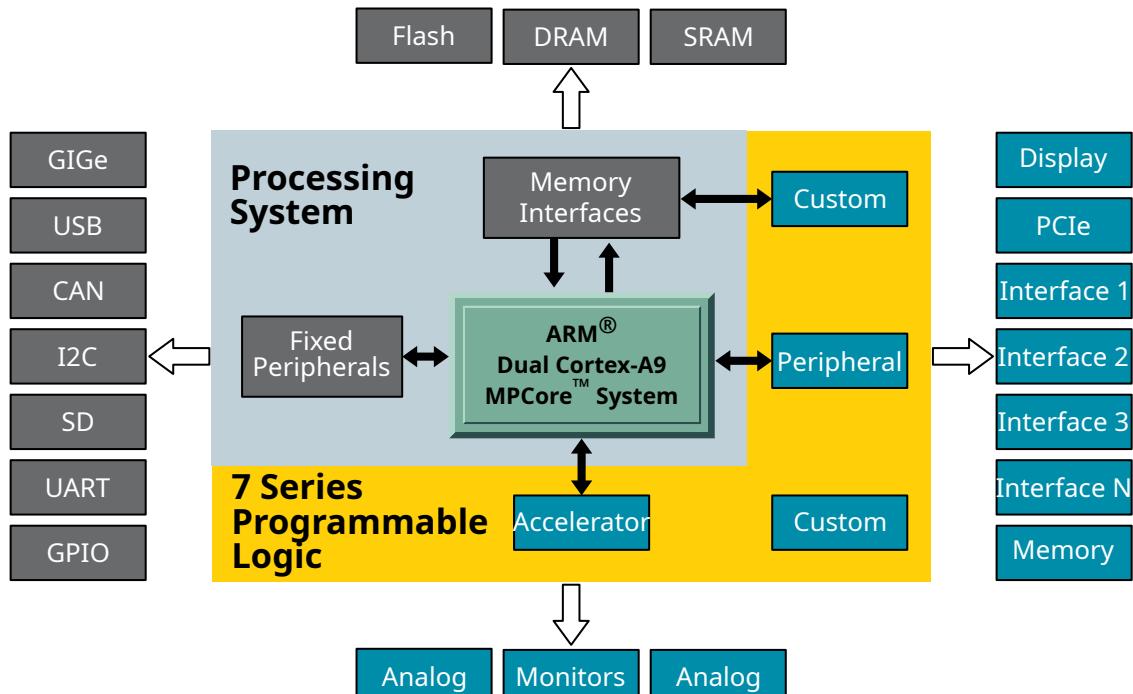

Con los recursos existentes hoy en día, las FPGAs suelen estar embebidas en un híbrido que posee además una parte “dura”. Esta parte no maleable puede incluir un procesador implementado en *chip* (como un ARM), bloques de conversión Analógico/Digital, puertos de entrada/salida y hardware adicional.

Este tipo de híbridos resulta ser el caso ideal para utilizar una FPGA como un acelerador para el procesador principal (que correspondería a la parte mencionada como dura).

En estas configuraciones existen restricciones como el ancho de banda de acceso a memoria, las unidades funcionales pre-implementadas o la cantidad de puertos de entrada/salida que limitan el funcionamiento de este tipo de dispositivos. Si bien los procesadores tradicionales (**ASIC**) actuales también tienen estas limitaciones, suelen estar órdenes de magnitud por encima de lo disponible en una FPGA (ver figura 1.1).

Dadas estas limitaciones, si se quiere ejecutar código paralelizado dentro de una FPGA, una de las opciones es implementar múltiples procesadores completos (*softcores*) con un sistema de interconexión.

Uno de los tipos de celdas más comunes en FPGA son los que implementan bloques de memoria (BRAM). Esta memoria cuenta con una muy reducida latencia, lo que permite su uso en la implementación de *caches*.

Dada la posibilidad de implementar memorias en FPGA, algunos *softcores* prediseñados implementan internamente o contienen puertos especiales que permiten acceder de manera eficiente a una BRAM configurable por el diseñador.

Tomando como punto de partida las prestaciones que presenta este tipo de hardware y considerando la necesidad de ejecutar código dentro de la FPGA, se propone estudiar formas de hacer esto mismo, poniendo foco en el uso eficiente de la memoria.

## 1.2. Objetivos del trabajo

Este trabajo tiene como objetivo general,

*Avanzar en técnicas que permitan el uso eficiente de múltiples softcores dentro de una FPGA.*

Para alcanzar este objetivo se proponen las siguientes metas:

1. Desarrollar un *framework* de evaluación de múltiples *softcores* escalable, que permita considerar distintos sistemas y configuraciones, minimizando los cambios requeridos.

2. Identificar fuentes de las limitaciones en eficiencia y en la capacidad de escalar en sistemas multicores basados en *softcores*.

3. Proponer formas de mejorar la eficiencia de programas de propósito general sobre múltiples *softcores*.

El estudio busca hacer foco en el uso eficiente de la memoria. En particular, vamos a añadir una BRAM aislada a cada *softcore*. Analizaremos varias formas de aprovechar esta memoria estática para mejorar la performance de distintos programas.

## 1.3. Trabajo relacionado

Uno de los *softcores* más utilizados es el MicroBlaze, desarrollado por Xilinx y creado específicamente para su uso en FPGAs. En Matthews et al. [8] se extienden varios MicroBlaze para correr Linux SMP (*Symmetrical MultiProcessing*), un sistema operativo utilizado en procesadores comunes. Allí detallan los inconvenientes a la hora de interconectar varios MicroBlaze para soportar dicho sistema operativo. Entre ellos se encuentran las interrupciones, MMU (*Memory Management Unit*), *timers* y operaciones atómicas.

En esta tesis se considerarán algunos de los problemas mencionados en ese trabajo, haciendo foco en el uso de operaciones atómicas (herramientas fundamentales para la implementación de mecanismos de sincronización). En nuestro caso particular, la coherencia entre procesadores está garantizada por el uso del protocolo ACE [9]. Esto nos permite implementar funciones de sincronización por software, a diferencia de Matthews et al. [8], donde garantizan la atomicidad mediante un bloque de hardware específicamente diseñado para implementar un árbitro.

Por otro lado, la configuración para inicializar los *softcores* es diferente. En Matthews et al. [8] los MicroBlaze ejecutan código de *firmware* precargado en BRAM y reciben una señal de interrupción de otro procesador cuando son necesarios. En nuestro trabajo, en cambio, todos los MicroBlaze comienzan ejecutando el mismo código directamente en memoria principal, logrando un comportamiento determinístico en el encendido del sistema.

Adicionalmente, en este trabajo utilizamos LMB (*Local Memory Bus*) para comunicar cada MicroBlaze con una memoria BRAM aislada y OPB (*On-chip Peripheral Bus*) para conectar cada procesador a una *cache* L2. Bečvář et al. [10] evaluaron todas estas interfaces, junto con *Fast Simplex Link* o FSL (canales unidireccionales diseñados para conectar un MicroBlaze con aceleradores de hardware), donde conectaron un coprocesador con el MicroBlaze. Se observó que LMB y FSL son similares en desempeño, ambas presentando mejoras respecto de OPB, y con un menor uso del área de FPGA en el caso de FSL.

Otro ejemplo que ilustra el uso de Microblaze es el caso de Cvikel et al. [11], donde se implementa un detector de pulsos para un ECG. Esta implementación se compara entre un procesador PowerPC integrado contra un MicroBlaze, y se llega a la conclusión que para la aplicación realizada no es necesario un microprocesador de alto desempeño como el PowerPC ya que el MicroBlaze resulta suficiente.

El entorno utilizado es similar a los experimentos realizados en este trabajo, la señal de entrada que el MicroBlaze debe procesar está en memoria DDR junto con el código del programa. Este código es lo suficientemente grande como para no entrar completo en una memoria BRAM, por lo cual se hace uso del OPB. Además utilizan el LMB para acceder a una BRAM dedicada para el MicroBlaze. Esta memoria se utiliza para mantener un *stack* y un *heap*.

Es posible que, de poder particionar el código y siguiendo el espíritu de nuestro trabajo, se pueda hacer que el procesador copie las partes de uso más frecuente a BRAM o las vaya intercambiando a medida que necesitan ejecutar. Hacer esto en conjunto con usar una *cache* de instrucciones podría llegar a reducir los accesos a memoria y mejorar la performance.

Una comparación general entre *softcores*, así como un análisis comparativo de performance entre MicroBlaze de Xilinx y LEON3 (procesador open-source que implementa el set de instrucciones SPARC V8 desarrollado por Sun Microsystems) puede verse en Makni et al. [12].

Como observación interesante, se destaca que el uso de recursos de FPGA resultó similar entre ambos procesadores. Esta diferencia es levemente menor para el LEON3 en general, con la excepción de un uso importante de LUTs (*Look-Up tables*) debido a una FPU más completa.

Por otro lado, el trabajo analiza los tiempos de ejecución para un JPEG encoder y decoder utilizando una arquitectura de 1, 2 y 4 MicroBlaze contra una similar con LEON3, resultando el *single-core* MicroBlaze 2 veces más rápido que su contraparte y 3 veces más rápido para el caso *quad-core*. En dicha arquitectura los *softcores* tienen una relación *master-slave* similar a la de nuestro trabajo, donde uno de ellos se encarga de informar a los demás cuando deben comenzar a ejecutar sus tareas.

En el libro *The Zynq Book* [13], se describe con detalle la plataforma Zynq-7000 de Xilinx (utilizada en este trabajo) y se ofrece una comparación entre un MicroBlaze implementado en la FPGA y un ARM *dual-core* incluído en la plataforma, teniendo el *dual-core* aproximadamente 20 veces más capacidad de procesamiento que el *softcore* (5000 DMIPS vs 260 DMIPS)<sup>2</sup>.

Advierten en el texto que las diferencias en la performance pueden deberse a un set de instrucciones más extenso para el ARM, una FPU de precisión doble (la del MicroBlaze es de

---

<sup>2</sup>DMIPS o *Dhrystone Millions of Instructions Per Second* es la cantidad de operaciones por segundo que alcanza un procesador corriendo el test standard Dhrystone. Este test está especialmente diseñado para que el procesador corra un conjunto representativo de operaciones sin ser representativo de una aplicación real.

precisión simple), una configuración de *cache* de dos niveles (el *softcore* permite configurar sólo un nivel), y a que se trata de una comparación entre un *dual-core* (ARM) y un *single-core* (el MicroBlaze). Es posible que esta brecha se reduzca para una arquitectura *multi-core* de MicroBlaze y para aplicaciones restringidas a punto flotante de precisión simple.

Si al lector le interesa conocer más sobre la plataforma, el libro también detalla el proceso de diseño de hardware para FPGA, y ofrece varias aplicaciones que hacen uso de una FPGA, entre otros puntos relevantes.

Por último, se hace mención al *benchmark* Dhrystone [14] como un ejemplo de *benchmark* sintético. Este tipo de *benchmark* tiene la intención de evaluar una o más características del sistema, procesador o compilador mediante programas simples que ayudan a cubrir estadísticamente los usos que sean relevantes.

La performance obtenida, sin embargo, no es necesariamente indicativa de la que habría para una aplicación real.

Otro tipo de *benchmark* es el de aplicación completa, donde utilizan código de algoritmos reales (comunes y de uso frecuente). Un punto intermedio es un *benchmark* de sólo algoritmos, en el cual se comparan algoritmos en áreas de aplicación especiales.

En nuestro trabajo haremos uso de estos dos últimos tipos de *benchmark* para analizar la diferencia de performance entre las distintas variantes. Principalmente porque es necesario entender el código que estamos ejecutando y cómo aplicar en éste las técnicas de optimización.

## 1.4. FPGA

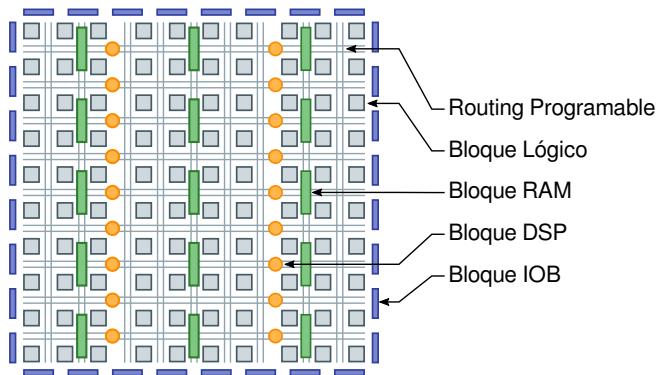

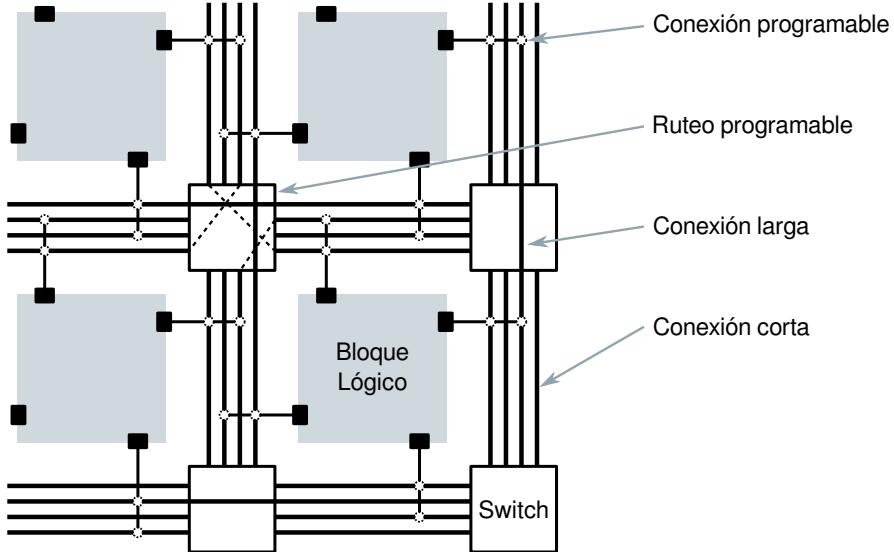

Como mencionamos anteriormente, una FPGA (*Field-Programmable Gate Array*) consiste en una grilla de celdas de distinta especialización que pueden conectarse de diversas formas (Figura 1.2).

En esta sección entraremos en más detalle. Hablaremos sobre los tipos de celdas más comunes, así como las conexiones disponibles en la grilla, hasta las aplicaciones y limitaciones de las FPGAs. Además, introduciremos detalles del proceso de diseño, terminologías y protocolos útiles.

### 1.4.1. Tipos de celdas

Existen diferentes tipos de celdas, cada una diseñada para resolver un problema específico. A continuación se describen los tipos básicos de celdas que se pueden encontrar dentro de una FPGA.

Figura 1.2: Estructura básica de una FPGA

## CLB

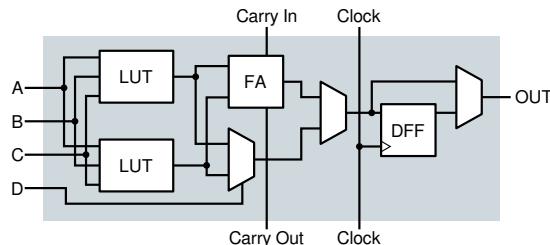

Cada celda lógica configurable (CLB, *Configurable Logic Block*) puede tener LUTs (*Look-Up Table*) de N bits, así como multiplexores, *flip-flops* y otros componentes lógicos (Figura 1.3). Las CLB pueden ser tan simples o tan complejas como sean diseñadas por el fabricante. Son la unidad lógica más básica de la FPGA y suelen ser los bloques de mayor presencia dentro del circuito integrado.

Figura 1.3: Una celda lógica con una LUT de 4 bits, un sumador *full-adder* (FA), un *flip-flop* D (DFF) y varios multiplexores.

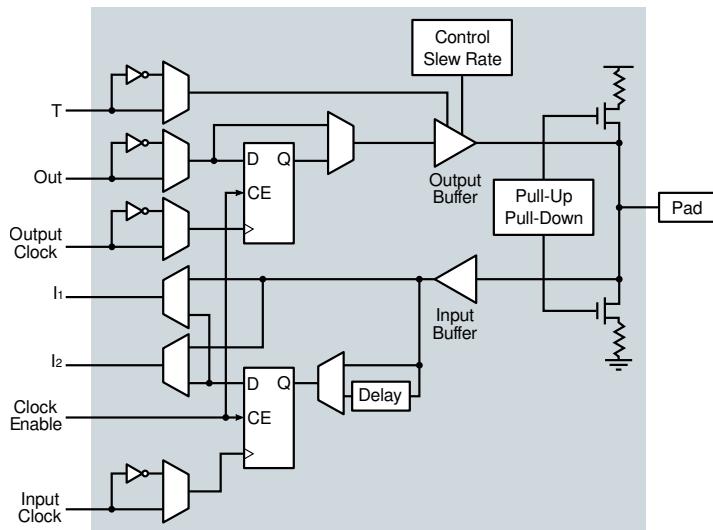

## BRAM, DSP, IOB

La mayoría de las FPGAs modernas contienen otros tipos de bloques además de los CLB. Estos están especializados para implementar ciertas operaciones de manera rápida y eficiente, o bien cubrir otros usos. Entre ellos destacamos los bloques de RAM (*Block RAM* o BRAM), bloques para procesamiento digital (DSP, *Digital Signal Processing*) y bloques de entrada/salida (IOB, *Input-Output Block*)[15].

Figura 1.4: Diagrama de un IOB.

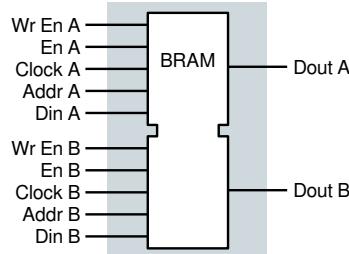

A la hora de implementar la *cache* L1 de un procesador, si bien teóricamente se pueden usar los *flip-flops* de las CLB, su cantidad limitada haría inviable alcanzar un tamaño útil. Más aún, se estarían desaprovechando los otros componentes de la celda. Si en cambio se utilizan bloques BRAM (figura 1.6), estaremos aprovechando un componente especializado para esta tarea, y con mucha mayor capacidad.

Por otra parte, una de las operaciones más utilizadas del procesamiento digital es la multiplicación y acumulación (MAC, *Multiplier-Accumulator*). Los bloques DSP permiten

resolver estas operaciones sin sacrificar grandes cantidades de celdas lógicas (figura 1.5). Un componente que puede hacer uso de bloques DSP es una FPU (*Floating Point Unit*).

Finalmente, hay ocasiones en las que se busca interactuar con algún componente externo a la FPGA. Por ejemplo, un botón o interruptor, un LED, o alguna otra señal digital. Los IOB permiten implementar esta interfaz como puertos (Figura 1.4).

Figura 1.5: Diagrama de un bloque DSP implementando un multiplicador y acumulador de 48 bits.

Figura 1.6: Diagrama de puertos de un BRAM que soporta escritura / lectura simultánea.

### 1.4.2. Interconectividad

Como ya mencionamos, los bloques o celdas están dispuestos en forma de grilla. La salida de una celda puede conectarse con la entrada de otra, o continuar su camino hacia la próxima celda. Los *switches* son los elementos que definen estas conexiones, encontrándose en las esquinas de cada celda en la grilla (figura 1.7).

Hay distintos tipos de líneas (o cables) que llegan a los *switches*. Se distinguen principalmente por su longitud en términos de cuántas celdas atraviesan. Existen además líneas que están dedicadas a señales específicas. Un ejemplo de esto son las señales de sincronización o *clock* (*CLK*).

Es posible que un mismo *clock* se utilice en varias celdas, tal vez distribuidas en distintas áreas de la FPGA, requiriéndose que la señal sea lo más “simultánea” posible. Hay tipos de líneas “globales” o de *routing* global que distribuyen una señal de *clock* con bajo *skew*.

Mucho antes de alcanzar el 100 % del uso de bloques<sup>3</sup>, la arquitectura de grilla suele ser el mayor limitante para implementar un diseño en FPGA [16, 17], ya sea por la falta de conexiones o por los *delays* que se introducen al aumentar la complejidad de las rutas que deben tomar las señales.

<sup>3</sup>En este caso nos referimos a todos los tipos de bloques disponibles. Es común que no pueda implementarse un diseño particular porque la FPGA utilizada no posee suficientes bloques especializados como DSP o BRAM.

Figura 1.7: Diagrama de una parte de la grilla.

### 1.4.3. PL y PS

Dentro del mismo chip que contiene la FPGA pueden existir otros circuitos integrados como procesadores o controladores, a los que se accede utilizando una interfaz dedicada. Este tipo de arquitecturas divide el circuito integrado en dos partes: la “flexible” que permite programar el hardware, también llamada PL (*Programmable Logic*), y su contraparte “dura” con componentes embebidos, denominada PS (*Processing System*).

En un sistema de procesamiento, se podría dedicar la parte PS a hacer operaciones de carácter serializado, típica de los procesadores, y utilizar la gran capacidad de procesamiento paralelo de la PL para problemas específicos.

Figura 1.8: Un chip con una FPGA y un ARM integrado. La zona amarilla corresponde a la parte PL.

Las interfaces disponibles podrían permitir, por ejemplo, conectar la lógica programable al controlador de memoria, a señales externas e incluso a señales del mismo procesador (figura 1.8).

Un ejemplo que utiliza ambas partes (tanto la lógica programable como el sistema de procesamiento) podría ser un sistema de post-procesador de video en tiempo real. Por un lado, se utilizaría la PL para implementar filtros por hardware y, por el otro, el procesador en la PS se ocuparía de ejecutar un sistema operativo donde se correría software ya existente para la transmisión del vídeo.

#### 1.4.4. Limitaciones

La FPGA utiliza celdas para implementar hardware. Las celdas están compuestas por varios componentes (LUT, FF, multiplexores, etc) lo que les aporta un grado de configurabilidad. Comparando con una implementación directa, esto implica una mayor cantidad de componentes. El *routing* además introduce retardos que suman mayores limitaciones a las implementaciones en FPGAs. Todo esto se traduce en una mayor área de chip, mayor consumo energético, y peor *performance* que una implementación nativa en hardware utilizando un ASIC (figura 1.1).

El problema de la temporalidad entre eventos (o *timing*) se debe tener en cuenta durante la implementación de cualquier diseño. A la hora de elegir las celdas y definir el *routing* de las señales, el proceso debe garantizar que el *timing* no supere ciertos límites. Esto puede devenir en un proceso lento y es posible, incluso, que no encuentre una solución. Es decir, que no haya una implementación válida en la FPGA disponible.

Una problemática asociada al *timing* es la frecuencia final de trabajo que tendrá un diseño una vez implementado. Esta frecuencia máxima de trabajo no puede ser asignada a *priori*, sino que será resultado de cómo fue implementado el diseño.

En ASIC, en cambio, al no depender de una arquitectura de grilla, hay mayor libertad a la hora de definir los componentes, sus ubicaciones e interconexiones. Esta libertad desemboca en una gama de implementaciones prohibitivas para FPGA donde el *timing* y la frecuencia de trabajo, por ejemplo, pueden adecuarse a las necesidades.

Implementaciones sobre distintos dispositivos pueden utilizar más celdas de algún tipo particular, dependiendo de sus características, incluso, tipos de celdas distintos, llevando a una diferencia de desempeño que impacta directamente sobre el resultado implementado y que no depende directamente del diseño del mismo.

Por último, se considera la limitante del área disponible. No se podrá implementar un diseño si el proceso requiere el uso de componentes cuyo número supera los disponibles en la FPGA.

#### 1.4.5. Tipos y usos

Considerando que el área del chip es limitada, existen en el mercado múltiples tipos de FPGAs. Cada una se caracteriza por las prestaciones con las que cuenta, su frecuencia de trabajo, grado de especialización y tamaño.

Si contáramos con una FPGA con una gran cantidad de BRAM, podríamos aprovecharla en casos que hagan uso intensivo de la memoria. En cambio, dado el menor espacio en el chip para otros bloques (lógicos, DSP, IOB, etc), las tareas que requieran más cómputo o mayor complejidad podrían no ser implementables.

Por otro lado, si es necesaria una FPGA para monitorear eventos externos y controlar dispositivos, se buscaría un diseño con gran cantidad de bloques IOB.

Su facilidad de reconfigurabilidad la hacen una plataforma indispensable para prototipar nuevos microprocesadores o microcontroladores antes de su implementación final en ASIC, más rápida y eficiente pero donde es muy costoso hacer cambios posteriores. También sirven como una herramienta de estudio, siendo posible implementar en una FPGA procesadores o piezas de hardware ya existentes.

En ocasiones, se necesita una solución de hardware embebido que excede a un microcontrolador, pero que es demasiado compleja de implementar con otros componentes (por ejemplo, una interfaz para comunicar dos circuitos integrados). Por otra parte, hay procesos que son muy lentos al ser ejecutados en un procesador estándar, o quizás no se dispone de una GPU o un procesador con suficientes núcleos. Es incluso posible que la tarea que se busca implementar no sea tan compleja como para requerir su uso.

Las FPGAs proveen una opción configurable, rápida (implementada en hardware) y altamente paralelizable.

#### 1.4.6. Diseño

Para implementar una solución en FPGA, se puede recurrir tanto a la codificación en un lenguaje de descripción de hardware, como al uso de una herramienta de diseño en bloques de alto nivel. Generalmente en diseños complejos se requiere hacer uso de ambos enfoques.

Ejemplos de lenguajes de descripción de hardware son **Verilog** y **VHDL**. El primero es más reciente y está basado en el lenguaje de programación C. VHDL es más explícito en cuanto a su sintaxis y está basado en los lenguajes Ada y Pascal. Ambos HDL (*Hardware Description Language*) son utilizados ampliamente en la industria.

Software como Vivado (de Xilinx) o Quartus (de Altera) cuentan con una interfaz gráfica que permite armar diseños con bloques e incluso implementar bloques mediante HDL. Este tipo de herramientas permiten establecer las conexiones entre los distintos bloques (*IP Cores*) disponibles, ya sea hacia puertos externos (entrada/salida), o hacia otros *IP Cores*. Si bien el diseño en bloques es luego traducido a HDL, facilita la etapa de diseño al permitirle al diseñador abstraer módulos y tratarlos como una caja negra.

Se le dice **síntesis** al proceso que toma una descripción en HDL y genera un circuito lógico (*netlist*) compuesto por compuertas, *flip-flops* y otros elementos interconectados. Además, verifica la sintaxis y analiza que el diseño sea optimizado para la arquitectura elegida (FPGA o ASIC). En este punto se puede obtener un estimado de los recursos necesarios para implementarlo en ésta.

El proceso de **implementación** se divide en tres partes:

- **Translate:** En primer lugar, se combina la *netlist* con restricciones físicas como los puertos (pines, *switches*, botones, etc) y restricciones de *timing*.

- **Map:** Luego, se mapea el circuito dividiéndolo en sub bloques que pueden asignarse a los bloques que dispone la FPGA elegida.

- **Place and Route:** Finalmente, se ubican estos sub bloques en la FPGA y se hace el *routing* respetando las restricciones.

Puede hacerse una verificación durante varias de estas etapas. Por ejemplo, se puede hacer una simulación del comportamiento del diseño a partir del HDL previo a la síntesis. También se puede simular el circuito generado en la etapa *Translate*, o luego de la etapa de *Place and Route*.

El último paso que resta es programar la FPGA. Para ello se traduce a *bitstream* el diseño generado en la etapa de implementación (un formato que la FPGA comprende). Dependiendo del tipo de FPGA, se puede requerir de una memoria no volátil externa, o incluir una en el mismo chip. En cualquier caso, este *bitstream* deberá ser escrito en memoria y la FPGA podrá finalmente ser configurada con nuestro diseño.

## IP Core

Un *IP Core* (*Intellectual Property Core*) consiste básicamente en una entidad con puertos de entrada (*slave*) y de salida (*master*) sobre la que pueden especificarse interacciones entre las señales, ya sea mediante otros *IP Core* interconectados, o utilizando HDL.

Para que *IP cores* con cierto grado de complejidad puedan comunicarse entre sí, generalmente se hace uso de un protocolo llamado **AXI** (o su variante **ACE**, que garantiza coherencia). También pueden implementarse interfaces con protocolos personalizados.

## AXI

**AXI** proviene de sus siglas en inglés (*Advanced eXtensible Interface*), siendo su última versión **AXI4**. Es parte del estándar **ARM AMBA 3.0** que fue originalmente desarrollado por ARM para usarse en microcontroladores. Tras revisiones y extensiones se ha convertido en un estándar de comunicación entre componentes de un chip [13].

Cuenta con tres variantes:

- **AXI4**: Comunicación entre varios dispositivos de alta *performance* utilizando mapeos en memoria. Es decir, se reserva un rango de direcciones al cual se puede leer o escribir para comunicarse con otro dispositivo. Con una dirección base permite hasta 256 palabras (words) enviadas en *burst*.

- **AXI4 Lite**: Comunicación simplificada, también utilizando mapeos en memoria. No permite *burst*.

- **AXI4 Stream**: Comunicación rápida entre dos dispositivos y sin utilizar mapeo en memoria. Soporta *burst* sin restricción.

## ACE

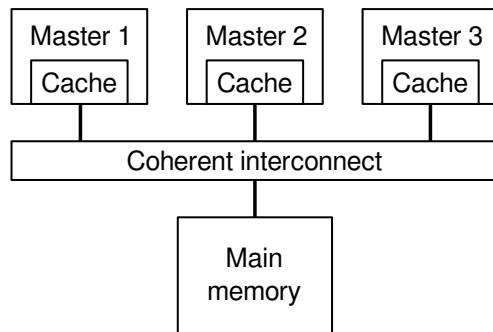

La variante **ACE** es una extensión de **AXI4** con soporte para la intercomunicación entre *caches* con coherencia por hardware [9]. Esto permite, por ejemplo, que varios dispositivos puedan leer y escribir información compartida cuando el valor más reciente no se encuentra necesariamente en la memoria principal.

Figura 1.9: Diagrama de conexión ACE.

El protocolo ACE asegura que todos los *masters* accederán a la última modificación realizada en cualquier dirección mapeada. Este comportamiento se logra forzando la existencia de una sola copia del valor luego de una modificación, y permitiendo que cada *master* obtenga una copia para su *cache* local.

El protocolo permite la implementación de una política *write-back* o *write-through*.

Para comprobar la multiplicidad de copias de un valor, el protocolo ACE agrega un bus auxiliar (*snoop bus*). Este bus permite la comunicación entre los *masters* para verificar quiénes tienen una copia del valor de una dirección, si es que la tienen. Esto permite identificar si existe una copia del dato y, en consecuencia, invalidarla para que otra de las *caches* pueda utilizarla. La operación requiere un mecanismo de transacciones distribuidas sobre las *caches*, que también es implementado sobre el *snoop bus* para garantizar la invalidación y escritura exclusiva.

## Softcore processor

Un *Softcore processor* es un caso particular de *IP Core*. Se trata de un microprocesador que puede ser implementado en FPGA, es decir que puede ser sintetizado.

Existen múltiples ejemplos de este tipo de procesadores, entre los que podemos destacar el Picoblaze (8 bits, de código abierto) y el MicroBlaze (32 bits y 64 bits) de Xilinx, así como también el Rocket Chip<sup>4</sup> que implementa el set de instrucciones de RISC-V.

Si bien todos estos ejemplos son catalogados de *softcores*, encontramos diferencias entre ellos: de la misma forma que existen microcontroladores y procesadores distintos, hay *softcores* para uso específico y otros de uso general. Algunos permiten configurarse para cumplir requerimientos específicos, como la reducción de espacio utilizado en la FPGA, mejor desempeño, o incluso una ISA (*Instruction Set Architecture*) ampliable. También podemos encontrar *Softcore processors* con versiones de código abierto o cerrado, siendo ambas implementables en FPGA.

En este trabajo vamos a utilizar MicroBlaze, del cual hablaremos más en detalle en las secciones subsiguientes.

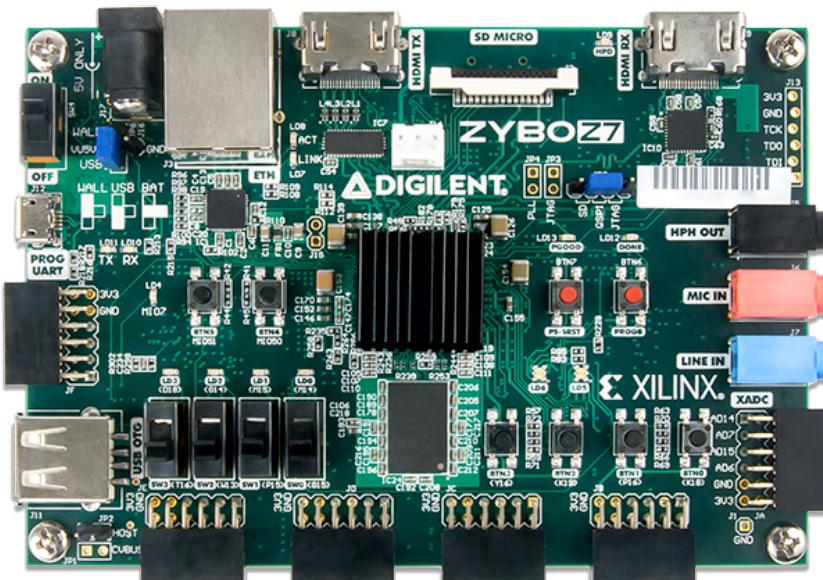

Figura 1.10: Zybo Z7 de Digilent

---

<sup>4</sup><https://github.com/chipsalliance/rocket-chip>

## 1.5. Plataforma

Para este trabajo se utilizó el *Development Board Zybo Z7* de Digilent<sup>5</sup> (figura 1.10).

Si bien existen plataformas de desarrollo más potentes, se eligió la presente porque contiene una FPGA con recursos suficientes para poder implementar múltiples MicroBlaze. Contiene, además, un ARM *dual-core* capaz de correr un sistema operativo, y desde el cual es posible programar la FPGA. Este tipo de FPGAs híbridas resultan ideales para realizar los experimentos planteados en este trabajo.

### 1.5.1. Hardware

Las características principales de la plataforma de desarrollo elegida son<sup>6</sup>:

- Alimentación por conector de 5 V, USB o batería.

- 1 GB de RAM DDR3 @ 1066 MHz.

- microSD.

- USB y Ethernet.

- HDMI de entrada y salida.

- Salida de audio en forma de headphone jack, line in, mic in.

- Chip XC7Z020-1CLG400C que integra:

- ARM Cortex-A9 dual core de 667 MHz.

- FPGA equivalente a una Artix-7

- 106,400 flip flops

- 630 kB de Block RAM.

- 56,200 LUTs de 6 bits.

- 220 DSPs.

- Varios I/O conectados al ARM o FPGA.

- Botones, switches, LEDs, algunos conectados al ARM.

### 1.5.2. Vivado

El software utilizado en este trabajo para construir los diagramas de bloques que permiten conectar los *IP Cores*, sintetizar y generar el *bitstream* necesario para configurar la FPGA fue Vivado 2018.3.

Vivado provee una galería de diversos *IP Cores* con distintos grados de configuración que pueden ser utilizados en cualquier desarrollo. Por ejemplo: multiplexores, procesadores, caches, y controladores de memoria. Ejemplos que además de estar pre-diseñados pueden ser implementados de forma eficiente en el hardware específico que se tenga disponible.

También permite crear *IP Cores* básicos con una cantidad definible puertos AXI de entrada/salida. Si bien la implementación de estos puertos es compleja por la cantidad de señales y la complejidad del protocolo, Vivado genera código en Verilog o VHDL de manera automática durante la creación del *IP Core*. El diseñador tiene libertad de hacer las modificaciones que crea adecuadas sobre el código.

<sup>5</sup><https://reference.digilentinc.com/reference/programmable-logic/zybo-z7/start>

<sup>6</sup>Zybo Z7 Board Reference Manual

El software ofrece al usuario la posibilidad de ajustar los parámetros de cada etapa (síntesis, implementación, generación de *bitstream*). Por ejemplo, es posible definir una prioridad que optimice el uso de área a expensas del *timing*. Incluso se le puede incrementar el tiempo dedicado a los procesos de síntesis e implementación a fin de encontrar una mejor solución.

Vivado permite simular la implementación antes de que sea programada en el dispositivo. Posee además un IDE específico para implementar y debuggear código sobre MicroBlaze. El programa queda compilado como un archivo .elf y se carga en la memoria BRAM asociada al MicroBlaze, dentro del *bitstream*.

Si bien esto puede ser suficiente para otros desarrollos (como sistemas embebidos), en este trabajo estamos haciendo uso de la FPGA como acelerador y requerimos tanto del sistema operativo en el ARM como del acceso a memoria DDR por parte de la FPGA, los cuales escapan el uso del IDE y exceden el alcance del simulador.

### 1.5.3. MicroBlaze

El MicroBlaze [18] es un *softcore processor* RISC de Xilinx<sup>7</sup>. No es *open source* pero está disponible para su implementación en FPGAs de Xilinx de manera gratuita.

Posee su versión de un GNU *toolchain*, permitiendo compilar, linkear y debuggear programas en C y C++. Tener una *toolchain* es fundamental para desarrollos complejos, ya que estandariza la mayor parte del código a escribir y simplifica la generación de programas. Esto permite, además, poder cambiar de *softcore processor* por otro que también posea una GNU *toolchain* y correr los mismos programas, con modificaciones menores.

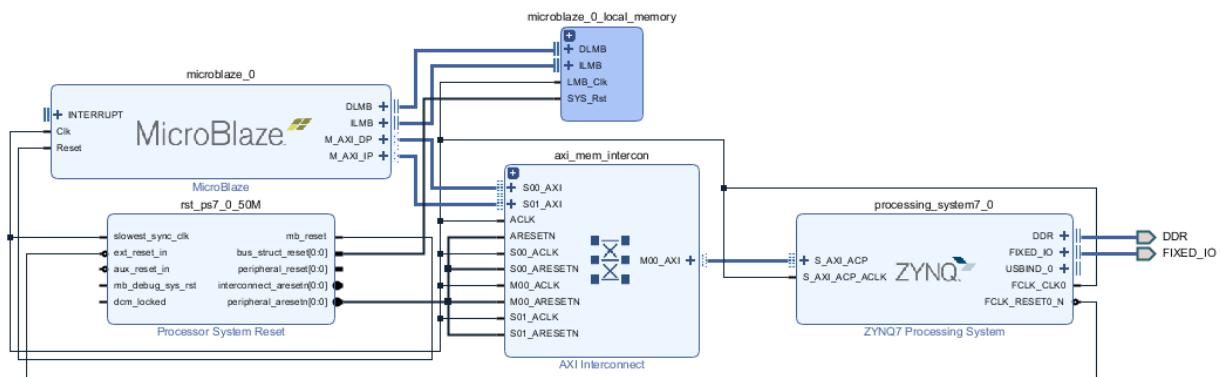

Es un *IP Core* configurable en varios sentidos, lo que permite su uso en diversos proyectos. En la figura 1.11 podemos ver un ejemplo de su representación en Vivado.

Utilizamos la configuración por defecto con algunos cambios: sin interfaz de *debug* y con el agregado de dos buses ACE independientes para datos (M\_ACE\_DC) e instrucciones (M\_ACE\_IC). La configuración por defecto incluye puertos independientes para acceder a una memoria local (DLMB, ILMB), señales de *Clock* (Clk) y *Reset*. El puerto INTERRUPT permite atender interrupciones externas que no utilizaremos en este trabajo y no puede ser ocultado.

En la Sección 2.2.2 veremos la configuración elegida para este trabajo. En [19] se presenta el *IP Core* con mayor detalle.

Figura 1.11: Ejemplo de *IP Core* MicroBlaze en Vivado configurado para su uso en este trabajo. A la izquierda están los puertos de control (*slave*) y a la derecha se encuentran los de acceso a memoria (*master*).

<sup>7</sup><https://www.xilinx.com/products/design-tools/microblaze.html>

A fines ilustrativos, destacamos el siguiente listado de opciones disponibles:

- 32 bits o 64 bits de tamaño de palabra.

- Implementación priorizando menor uso de área en la FPGA, mejor *performance* o mayor frecuencia.

- Pipeline 3-stage, 5-stage o 8-stage.

- ISA básica o con instrucciones adicionales como multiplicación y división entera (entre otras).

- FPU opcional: básica (operaciones aritméticas y de comparación), extendida (conversión *int-float* e instrucción raíz cuadrada).

- *Cache* opcional L1 para instrucciones y/o data.

- *Branch prediction* y *branch cache* opcionales.

- MMU opcional (Memoria Virtual).

- Bus de memoria local (BRAM) opcional.

- Bus AXI o ACE para data e instrucciones externas

- Interfaz de *debug* por hardware.

En la figura 1.12 podemos ver un ejemplo de diagrama de bloques autogenerado por Vivado a la hora de agregar un MicroBlaze sin *IP Core debugger*, junto con las conexiones entre *IP Cores* que Vivado puede realizar automáticamente. Entre ellas, se destaca la BRAM (`microblaze_0_local_memory`) que queda conectada con los puertos DLMB y ILMB.

Los puertos M\_AXI\_DP y M\_AXI\_IP son puertos AXI4 que en la figura 1.11 reemplazamos por variantes ACE.

A esto le agregamos una conexión con la memoria DDR utilizando interconectores AXI (`axi_mem_intercon`).

El *IP Core ZYNQ* representa la interfaz con el ARM y el resto del hardware integrado, denominada PS. *Processor System Reset* permite manejar el *reset* de todo el sistema (el AXI Interconnect, el MicroBlaze, la BRAM)<sup>8</sup>.

Figura 1.12: Diagrama de bloques con un MicroBlaze. Incluye una BRAM (`microblaze_0_local_memory`) y acceso a memoria DDR mediante un interconector AXI (`axi_mem_intercon`) conectado al puerto ACP del *IP Core ZYNQ*.

<sup>8</sup><https://docs.xilinx.com/v/u/en-US/pg164-proc-sys-reset>

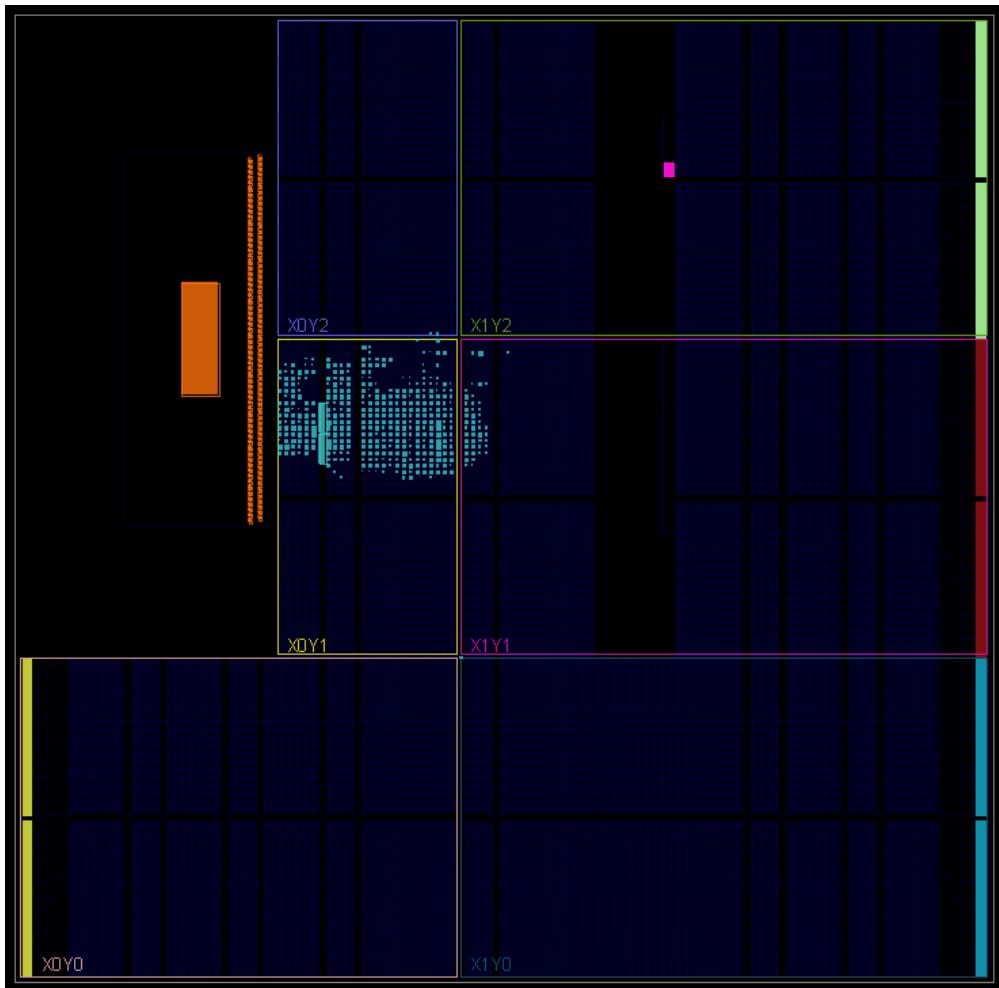

La figura 1.13 muestra la implementación del diseño marcando las celdas que van a utilizarse y mostrando el área total disponible de la FPGA.

En la mayoría de los casos, no tendremos un 100 % del uso del área, aún en diseños más complejos. Esto se debe, como mencionamos previamente, a restricciones de *timing*, o incluso a que ciertos tipos de celdas con menor disponibilidad (por ejemplo, las BRAM o las DSP) quedan totalmente utilizadas, lo cual impide implementar el diseño.

Figura 1.13: Representación del resultado de sintetizar e implementar el diagrama visto en la figura 1.12. Se muestran las celdas que quedaron configuradas (CLB, DSP, etc), las más largas correspondiendo a BRAM. Otras celdas pueden estar siendo parcial o totalmente utilizadas.

#### 1.5.4. Otras herramientas

Partimos del trabajo realizado por Ichiro Kawazome, que se encuentra disponible en su repositorio de github<sup>9</sup>. El repositorio contiene una serie de ejemplos de interacción entre el ARM y la FPGA para diferentes tipos de hardware. En particular rescatamos los siguientes elementos que nos resultaron útiles para la realización de este trabajo:

- Una imagen completa del file system con un kernel de Linux compilado para el hardware utilizado.

---

<sup>9</sup><https://github.com/ikwzm/FPGA-SoC-Linux>

- Drivers y servicios que permiten reprogramar la FPGA desde *userspace* o modificar el *device tree* del *kernel* sin tener que reiniciar.

- Un proyecto en Vivado implementando un DMA (*Direct Memory Access*) en un *IP Core*, incluyendo drivers de Linux que lo utilizan.

El contenido del repositorio resultó ser un buen punto de partida durante el desarrollo de este trabajo. Los servicios y diseños existentes para la FPGA fueron estudiados para comprender cómo funciona la comunicación entre un programa desde *userspace* en el ARM y un *IP Core* en la capa PL.

Con esta base, se procedió a desarrollar las herramientas de software y hardware necesarias para el trabajo.

# Capítulo 2

## Infraestructura desarrollada

Al implementar el hardware, tenemos un increíble grado de control sobre las capacidades y limitaciones de nuestro sistema final. Esto incluye múltiple escenarios que no estaríamos considerando de tener que utilizar un hardware fijo.

Esta situación es similar a escribir código en un lenguaje de alto nivel donde, por ejemplo, nos vemos obligados a interactuar con un *garbage collector*; en comparación con desarrollar en un lenguaje de bajo nivel donde el manejo de memoria es explícito.

Siendo que estamos tratando la capa más baja en un sistema de cómputo, queda en nosotros, tomando el papel de diseñadores, implementar la arquitectura del sistema.

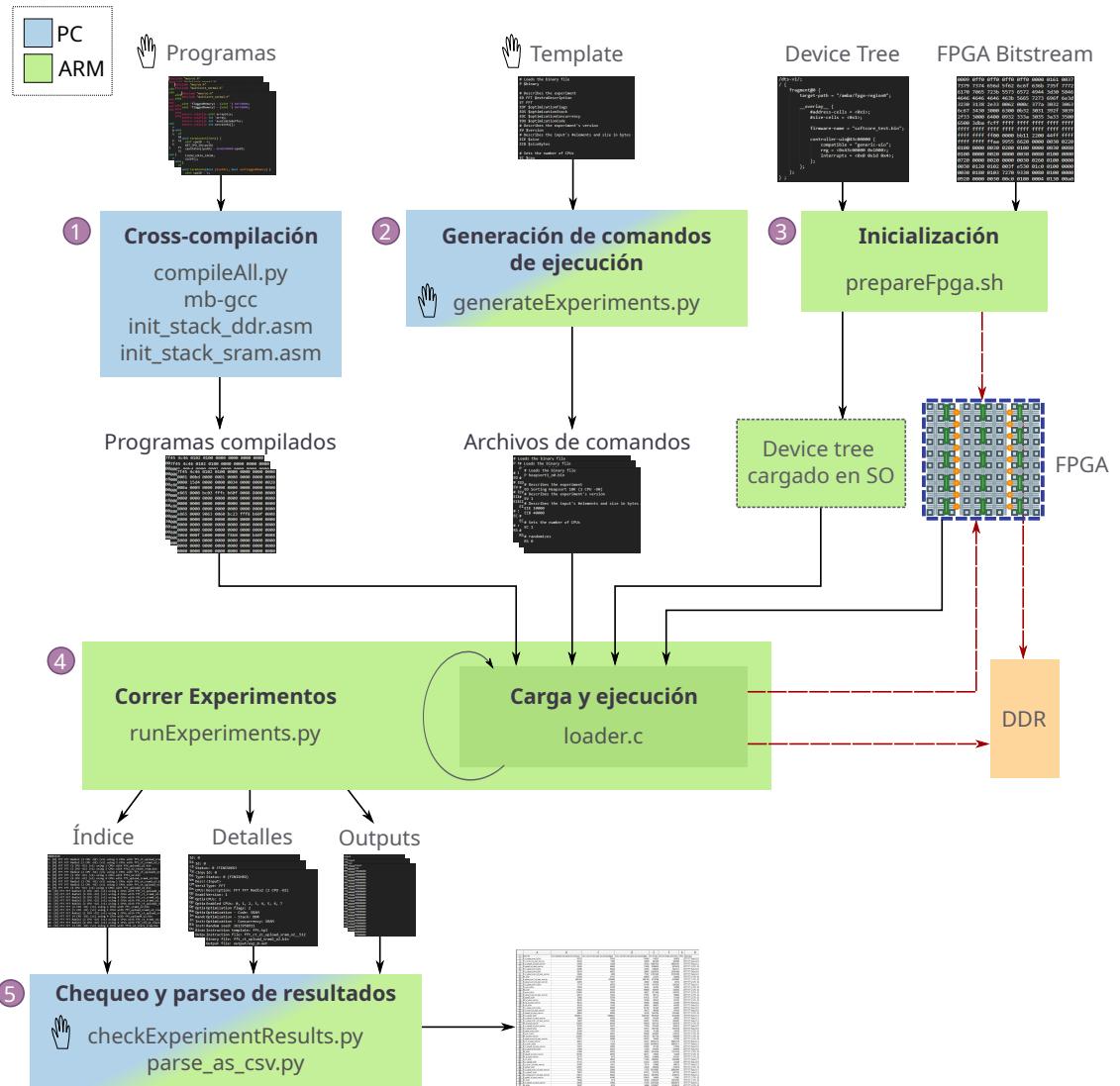

En este capítulo presentamos la arquitectura propuesta. Comenzaremos con una visión general en la sección 2.1 para luego separar la explicación desde el punto de vista del hardware (sección 2.2) y del software (sección 2.3).

### 2.1. Arquitectura

Tomaremos las siguientes máximas de diseño:

- **Utilizar SMP (*Symmetric Multi-Processor*)**. Nos interesa utilizar un sistema *multi-core* bajo un único tipo de procesador. En este caso, será el MicroBlaze de Xilinx.

- **Mantener flags de concurrencia en memoria externa**. Si bien hay módulos de hardware que implementan mutex y semáforos sin depender en memoria externa, no los utilizaremos en este trabajo. Nos interesa entender los cuellos de botella que existen con este método y si podemos mejorar el desempeño para programas con distintos grados de sincronización.

- **Utilizar BRAM aislada e individual**. Cada CPU (o *core*) tendrá un módulo de BRAM disponible para su uso individual e inaccesible para el resto. El programa en ejecución será quien defina cómo se utiliza.

- **Manejar datos de entrada/salida en memoria externa**. El programa y sus datos de entrada estarán disponibles en memoria externa al momento de iniciar la ejecución. La salida deberá escribirse a memoria externa.

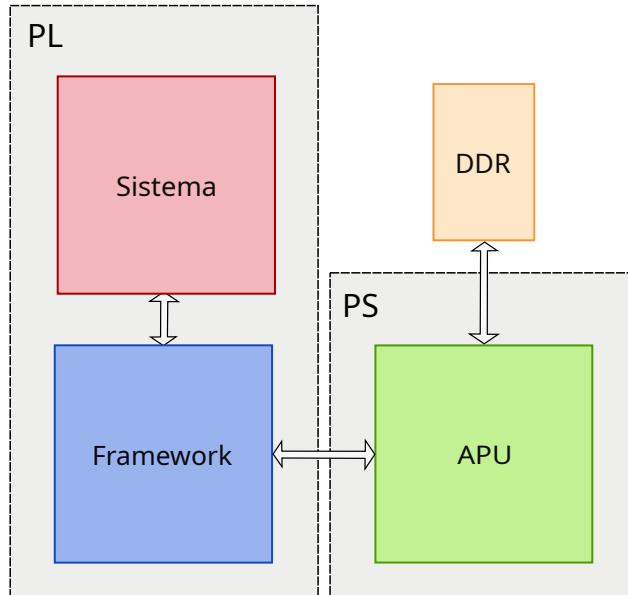

Llamaremos **Sistema** a un conjunto de *softcores* simétricos (SMP) donde cada uno tendrá acceso a un módulo de BRAM de manera independiente, y donde todos los *softcores* estarán conectados a una *cache L2*.

Llamaremos **Framework** al resto de los componentes en la FPGA que sirven de puente entre el **Sistema** y el **ARM**.

La **APU** (Application Processor Unit) comprende al par de procesadores **ARM** y provee una interfaz para la parte PL. Esta interfaz puede usarse para comunicar la parte PL con el **ARM**. Además permite acceder a memoria principal de manera coherente.

La figura 2.1 muestra estos componentes, junto con la memoria principal (**DDR**, externa a la FPGA), y da una visión general de su interconectividad.

Figura 2.1: Diagrama de alto nivel de la arquitectura a implementar. Las flechas indican la existencia de una o más señales (o buses) entre los componentes. Se indica si estos se encuentran en la capa PL, en la capa PS, o son externos.

El **Sistema** estará limitado en su interacción a señales de entrada mínimos (**CLK**, **RST**), así como a un único puerto de salida que utiliza una interfaz AXI para acceder a memoria principal. Esto nos permite abstraernos del tipo de *softcore* y nivel de *cache* utilizado.

Hacer uso de las señales de **CLK** y **RST** nos permitirá iniciar, pausar y resetear el **Sistema** a elección. Tener control sobre ellas nos permite, a su vez, medir el tiempo de ejecución con una precisión de ciclos de *clock*.

Si bien el *softcore* utilizado provee una interfaz de *debug*, no haremos uso de la misma porque no resulta lo suficientemente genérica y otros *softcores* podrían implementarla de forma diferente. Por otro lado, tampoco es necesario acceder a interrupciones ya que vamos a estar midiendo desempeño y no requerimos modificar el flujo de ejecución del programa del *softcore*.

Desde el punto de vista del **ARM**, utilizaremos el sistema operativo dentro del **ARM** para carga, puesta en marcha y monitoreo del programa a correr, así como la extracción de resultados y su chequeo. El programa a correr será cargado en memoria principal (**DDR**) con el **Sistema** desactivado.

El **Framework** estará monitoreando accesos a memoria principal por parte del **Sistema**. Esto permite que los programas puedan notificar su progreso y finalización mediante un mecanismo genérico. Tras activar el **Sistema**, el programa en ejecución hará accesos a posiciones de memoria distinguidas que permitirán notificar al **ARM** la transición entre distintas etapas de su ejecución.

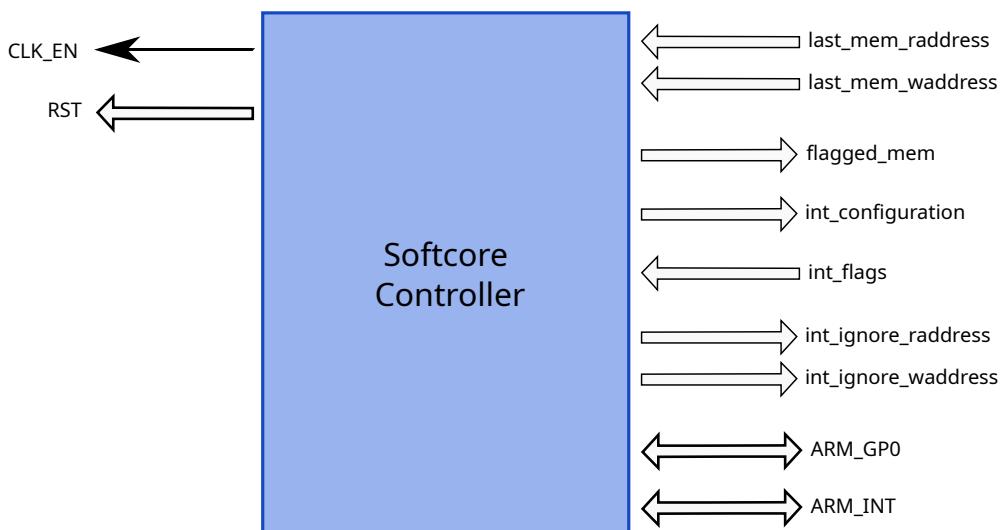

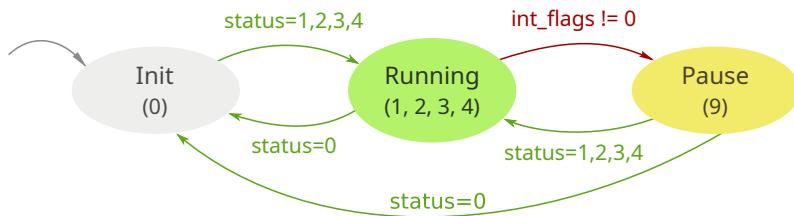

Para esto desarrollamos e implementamos dos *IP Cores*: un **Softcore AXI Controller** que nos permite monitorear los accesos a memoria principal, y un **Softcore Controller** con el cual el **ARM** interactúa para configurar el **Framework**, así como para activar, pausar y resetear el **Sistema** según sea necesario.

A continuación, y con el fin de ordenar los puntos a tratar en el presente capítulo, se plantea una división en términos de hardware y software.

La parte hardware trata sobre la implementación en la FPGA, es decir, el **Sistema** junto con los *IP cores* mencionados anteriormente. Además, detalla la forma en que se administrará la memoria principal entre el **ARM** y el **Sistema**.

La parte de software trata sobre las herramientas que nos permitirán la implementación, carga en memoria, ejecución y análisis de resultados de los experimentos.

## 2.2. Arquitectura (Hardware)

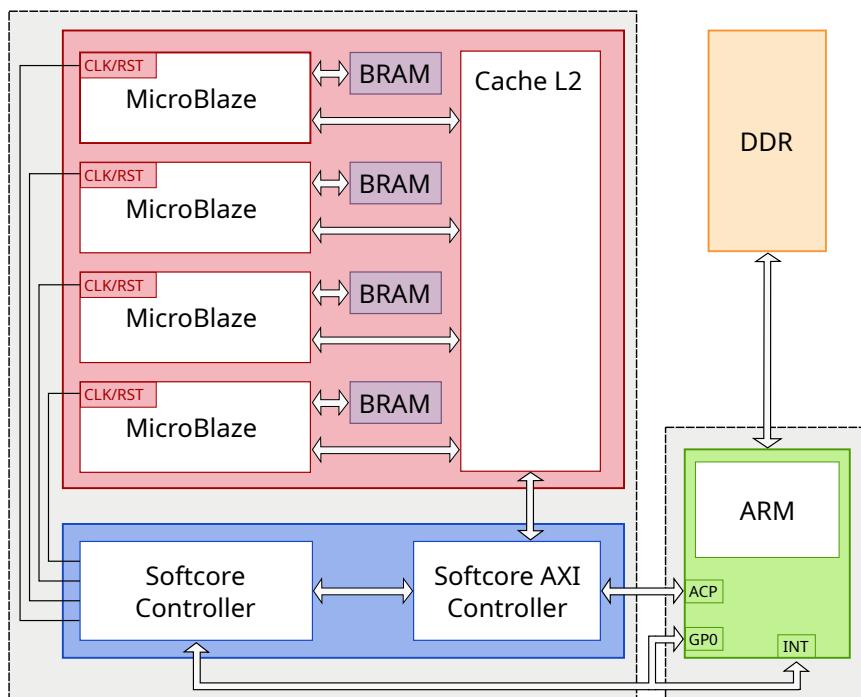

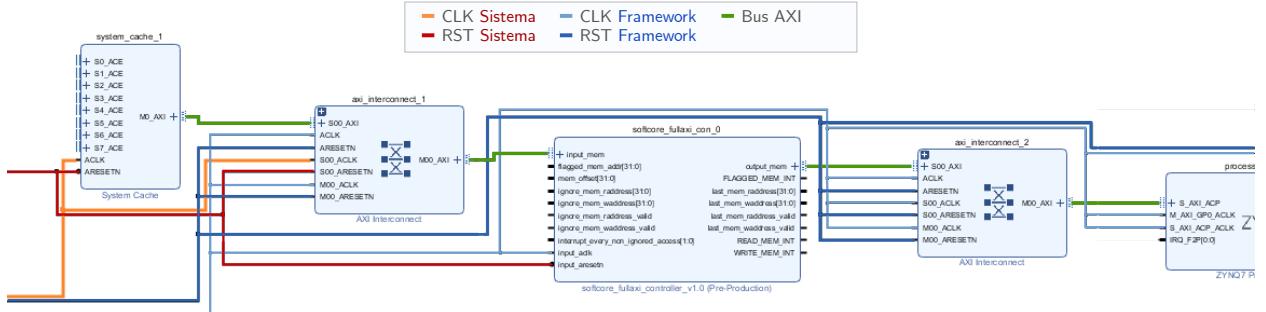

En la figura 2.2 podemos observar el detalle de tres de los componentes vistos en la figura 2.1.

El **APU** (Application Processor Unit) contiene el **ARM** y provee una interfaz para la capa PL de la cual vamos a utilizar tres puertos:

- El puerto **ACP** (Acceleration Coherency Port) provee un acceso AXI a la memoria principal que garantiza coherencia con el **ARM**.

- El puerto **INT** permite generar interrupciones hacia el **ARM**. Estas interrupciones informan al **ARM** de eventos como la transición entre etapas descrita en la introducción de este Capítulo.

- El puerto **GP0** (General Purpose 0) sirve de canal de comunicación desde el **ARM**. Esta comunicación usa el protocolo AXI y le permite leer y escribir registros dentro del **Softcore Controller**.

Figura 2.2: Diagrama visto en la figura 2.1 con el detalle de los componentes utilizados. **CLK/RST**, **ACP**, **GP0** e **INT** son puertos de sus componentes respectivos. Las flechas indican la existencia de una vía de comunicación entre los componentes. Las líneas simples indican una comunicación en forma de señales.

El **Framework** está compuesto por los ya mencionados **IP Cores Softcore Controller** y **Softcore AXI Controller**. En cambio, el denominado **Sistema** está compuesto por **IP Cores** provistos por Xilinx: cuatro **MicroBlaze**, cada uno con su módulo de **BRAM**, y una **cache L2**.

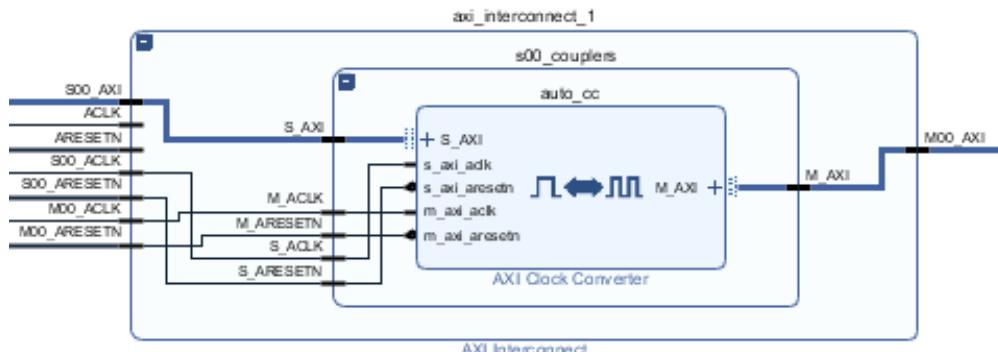

Las señales de **CLK** (*Clock*) y **RST** (*Reset*) de los **MicroBlaze** están controladas por el **Softcore Controller**. La **L2** se comunica con la **DDR** mediante el **Softcore AXI Controller**, quien redirecciona todas las transacciones AXI al puerto **ACP**, agregando un offset a la dirección de memoria (el cual explicaremos más adelante).

El **Softcore Controller** y el **Softcore AXI Controller** se comunican entre sí para configurar qué direcciones de memoria y/o tipos de acceso generarán eventos. Estos eventos nos permitirán identificar las transiciones de etapa del programa, las cuales iremos detallando durante el resto del Capítulo.

Un punto a destacar es que si bien utilizamos el puerto **ACP**, este sólo garantiza coherencia de lectura/escritura con el **ARM**<sup>1</sup>. Es decir, si se hace un acceso de lectura, el resultado será el mismo desde el punto de vista del **ARM**. Si se hace una escritura, el dato en las **cache** del **ARM** (de estar ahí) será invalidado y tendrá que buscarlo en la **DDR**.

Es importante mencionar que esto **no implica** que la parte PL utilizando este puerto tiene coherencia con el **ARM**. Por ejemplo, una cache conectada al puerto **ACP** debe hacer un *flush* para que el **ARM** y la **DDR** estén al tanto de los cambios que hace. De la misma forma, escrituras del **ARM** a **DDR** no son notificadas por el puerto **ACP** (el protocolo AXI no maneja coherencia).

Ambos puntos fueron tomados en cuenta y el *workaround* elegido está explicado más adelante.

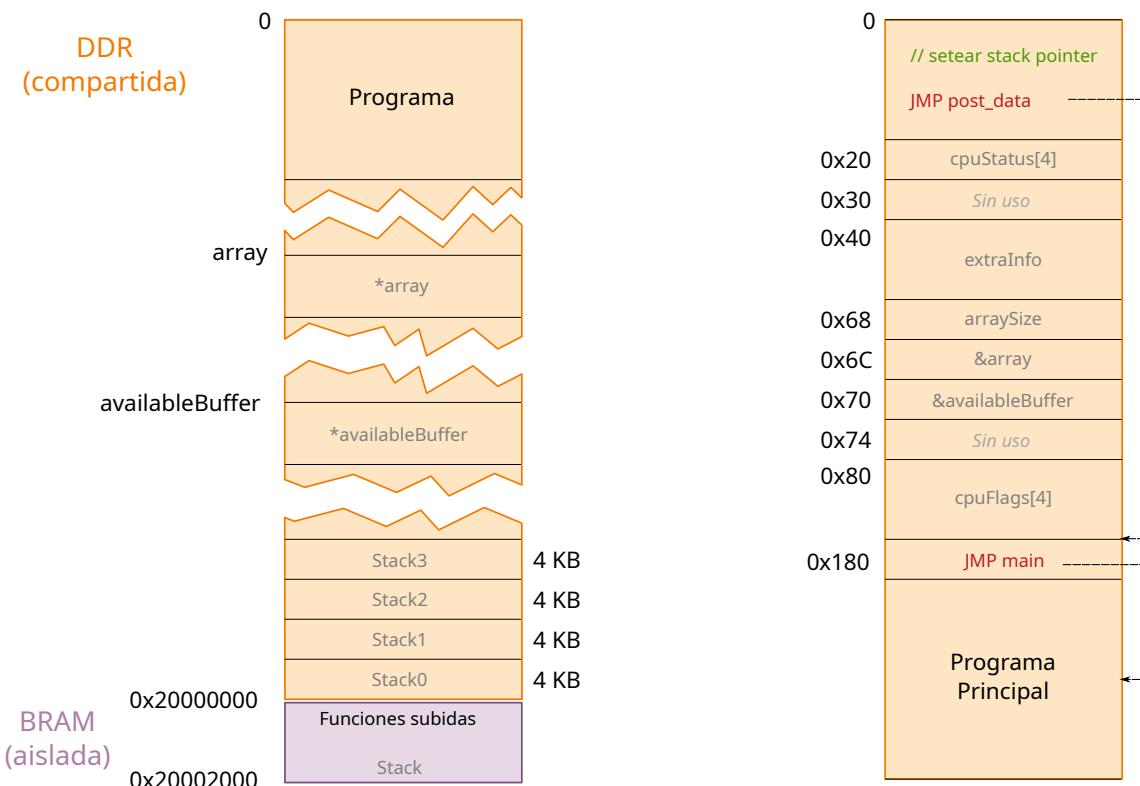

## 2.2.1. Uso de Memoria

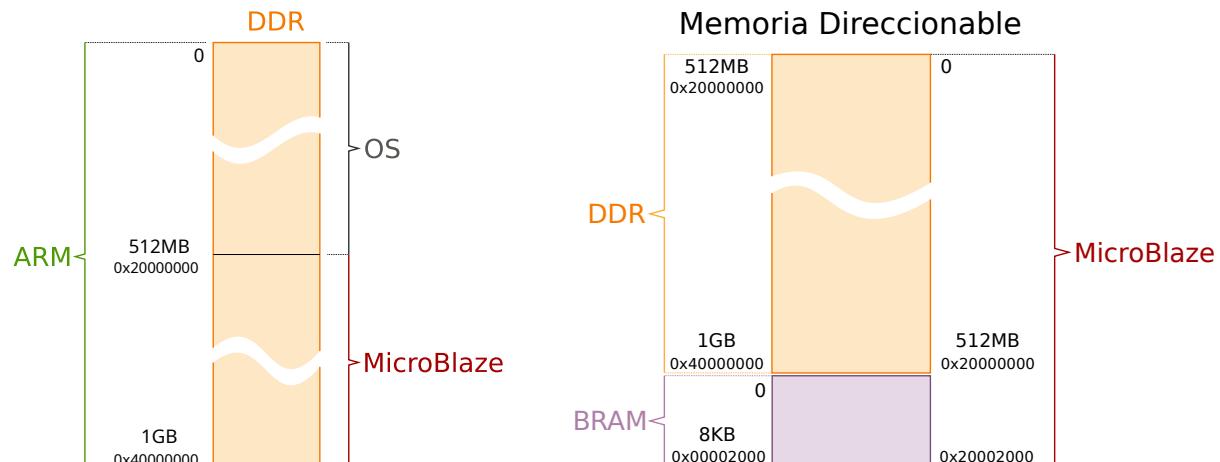

Figura 2.3: Uso de memoria.

<sup>1</sup>El **APU** provee otros puertos de acceso directo a memoria que no tienen coherencia con el **ARM** pero que requieren implementar sincronización y coherencia por software.

## DDR

La memoria **DDR** total disponible en la placa es de 1 GB. Si bien el **ARM** tiene acceso total, para evitar conflictos entre los *softcores* y el sistema operativo se reconfiguró el kernel de manera que utilice únicamente los primeros 512 MB. La fracción de memoria sobrante será accedida solo para cargar programas con sus *inputs* y para leer la salida de la ejecución. Los *softcores* solo tienen acceso a la parte superior de la memoria, es decir a los 512 MB más altos, indicados en la figura 2.3a.

El **Softcore AXI Controller** se ocupa, entre otras tareas, de agregar un *offset* de 0x20000000 a la memoria que direccionan los *softcores* (los 512 MB altos del 1 GB de la memoria). Esta diferencia puede observarse en la figura 2.3b.

Gracias a este *offset*, el acceso a la parte alta de la memoria resultará transparente para los **MicroBlaze**, los cuales estarán configurados para iniciar la ejecución desde la dirección 0x00000000. Este offset, sumado a que el protocolo AXI permite limitar las direcciones accesibles por puerto, permite restringir a los *softcores* de forma que no puedan acceder a los primeros 512 MB de memoria **DDR**.

## BRAM

Como vimos en la figura 2.2 y hemos mencionamos previamente, cada **MicroBlaze** tiene una **BRAM** propia de 8 kB (sugerida por Vivado para el *softcore*), aunque podría configurarse una memoria de 4 kB, 16 kB, 32 kB, 64 kB y 128 kB. En la figura 2.3b se ilustra cómo se encuentra mapeada esta memoria a partir de la dirección 0x20000000 (inmediatamente después de los 512 MB del espacio de direccionamiento de los **MicroBlaze**).

A pesar de operar en el mismo espacio de direccionamiento, las **BRAM** no estarán conectadas al **MicroBlaze** por medio de un bus AXI. Utilizan, en cambio, un bus rápido y especializado llamado LMB (*Local Memory Bus*), el cual posee un protocolo más simple y tiene latencia mínima (1 ciclo de *clock*).

### 2.2.2. MicroBlaze

Buscamos una configuración que permita experimentar sobre un *softcore* que posea buen desempeño, capaz de ejecutar una amplia variedad de programas mono-tarea pero en múltiples cores.

Para ello, optamos por un **MicroBlaze** de 32 bit, big-endian, con una *cache* L1 de 8 kB para instrucciones y otra L1 de 8 kB para datos, ambas con líneas de cuatro palabras.

En la configuración del procesador se priorizó el rendimiento, utilizando una *cache* adicional para la predicción de saltos (*branches*). Por otro lado, se utilizó un ISA con todas las extensiones por hardware permitidas, contando con una FPU de 32 bit que permite realizar operaciones de punto flotante de precisión simple por hardware. Para el caso de las operaciones con doble precisión, éstas deberán ser simuladas por software.

Los programas serán ejecutados como monotarea, con el nivel de privilegio máximo desde la primera instrucción a ejecutar (posición 0 de memoria) y sin intervención de un kernel o sistema operativo. Tampoco nos interesa proteger ni limitar el acceso a memoria. Por ello no dispondremos de una MMU ni de ningún tipo de protección de memoria.

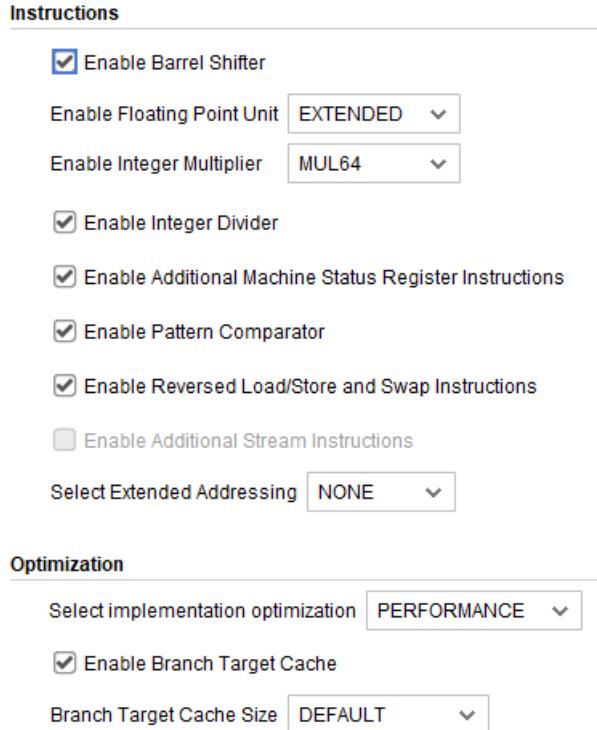

En la figura 2.4 se ilustra una de las pantallas de configuración que provee Vivado para el MicroBlaze. En [19] se exponen estas y otras configuraciones con más detalle.

Se seleccionó esta pantalla en particular porque provee las configuraciones generales para el procesador.

Figura 2.4: Configuración elegida de ISA y optimizaciones de MicroBlaze.

A fin de exponer con mayor detalle las opciones de la figura 2.4, se describe a continuación cada una de ellas:

- **Barrel Shifter:** Habilita instrucciones de bit shifting. Puede mejorar la *performance* pero aumenta el tamaño del procesador.

- **Enable Floating Point Unit:** Habilita instrucciones de punto flotante. Aumenta drásticamente el tamaño del procesador.

- **NONE:** Sin instrucciones de punto flotante por hardware.

- **BASIC:** Instrucciones para operaciones básicas de punto flotante (suma, resta, multiplicación, división, comparación).

- **EXTENDED:** Incluye las operaciones básicas, agrega la instrucción para calcular raíz cuadrada e instrucciones de conversión entre enteros y punto flotante.

- **Enable Integer Multiplier:** Habilita instrucciones de multiplicación. Aumenta el uso de bloques DSP.

- **NONE:** Sin instrucciones de multiplicación por hardware.

- **MUL32:** Instrucciones de multiplicación de 32 bit.

- **MUL64:** Instrucciones de multiplicación de 32 bit y 64 bit.

- **Integer Divider:** Habilita instrucciones de división entera.

- **Enable Additional Machine Status Register Instructions:** Habilita instrucciones que permiten setear el valor de bits específicos en los registros de máquina (MSR).

- **Pattern Comparator:** Habilita instrucciones de comparación. Por ejemplo, PCMPBF devuelve la posición del primer byte que comparten dos palabras. Otro ejemplo es la instrucción CLZ que calcula la cantidad de ceros a la izquierda.

- **Reversed Load/Store and Swap Instructions:** Habilita instrucciones load/store/swap utilizadas en datos con diferente *endianness* (en nuestro caso serían para datos *little-endian*).

- **Extended Addressing:** Habilita extensiones de las instrucciones load/store para que puedan exceder el direccionamiento por defecto (en nuestro caso, siendo un procesador de 32 bit, serían 4 GB).

- **Implementation Optimization:** Factores a optimizar.

- **PERFORMANCE:** Optimizar *performance* computacional. Utiliza un five-stage pipeline. Es el setting recomendado por Vivado, sugiriendo que las otras alternativas deberían considerarse sólo para casos muy específicos.

- **AREA:** Reducir el área utilizada en la FPGA. Utiliza un three-stage pipeline con menor throughput de instrucciones. No está disponible en sistemas con MMU, Branch *cache* o ACE, entre otros.

- **FREQUENCY:** Aumenta la frecuencia final del MicroBlaze. Utiliza un eight-stage pipeline. Se recomienda para alcanzar una frecuencia objetivo, particularmente cuando se utiliza memoria externa basada en *cache*, MMU o mucha memoria LMB (BRAM).

- **Branch Target Cache:** Habilita la predicción y el *caching* de branches de ejecución.

- **Branch Target Cache Size:** Cantidad de entradas. 1024 por defecto. 8 como mínimo. 2048 como máximo.

- **Fault Tolerance:** Se agrega paridad y soporte de ECC (Error Correcting Codes) a la BRAM en el LMB. Protege ante un bit flip en la BRAM.

Junto con el resto de los componentes, logramos insertar cuatro **MicroBlaze** con estas configuraciones manteniendo *delays* y *timings* en un rango seguro, según el reporte obtenido en Vivado. Buscamos equipar a los **MicroBlaze** con el soporte necesario para resolver cualquier programa general o numérico de asegurar su desempeño.

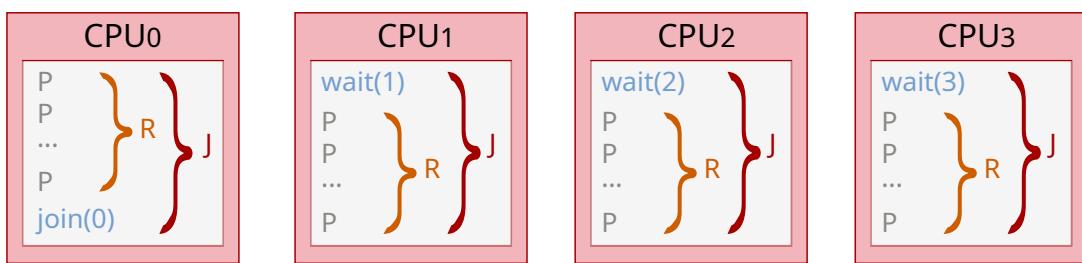

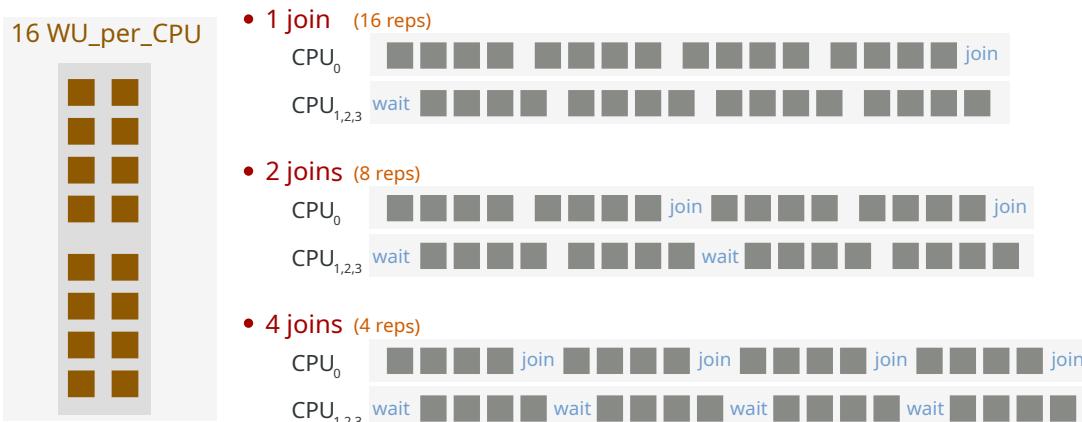

Para poder identificar cada *softcore* en tiempo de ejecución, se les configuró un identificador de 0 a 3 que puede leerse por código vía el registro RPVR1. Esto nos permite diferenciarlos fácilmente y, de ser necesario, asignarles tareas de manera directa. En ocasiones nos referiremos a los cuatro *softcores* como CPU0, CPU1, CPU2 y CPU3, siendo el “Main CPU” CPU0 (generalmente).

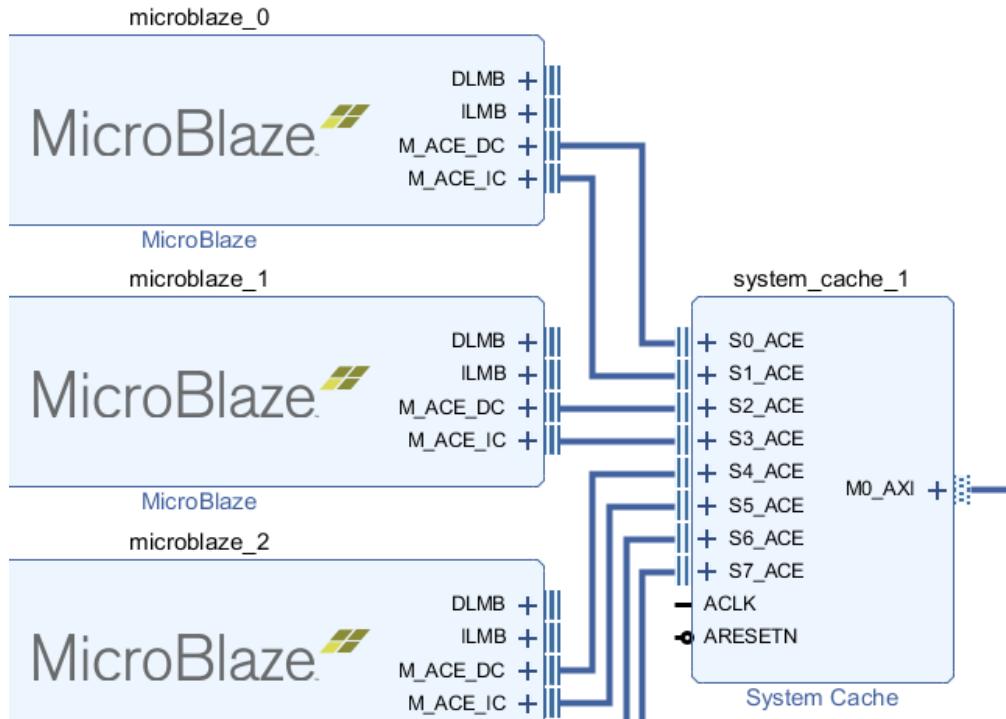

### 2.2.3. Cache L2

La **cache L2** es compartida por todos los *softcores*. Fue configurada como una memoria de 32 kB con dos líneas de 64 B. La comunicación desde los *softcores* hacia esta *cache* se hace usando el protocolo ACE que garantiza coherencia entre todos los dispositivos que la usan. Se conecta a memoria principal mediante el **Softcore AXI Controller** utilizando el protocolo AXI.

Esta *cache L2* es un *IP Core* provisto por Vivado y está optimizado para MicroBlaze.

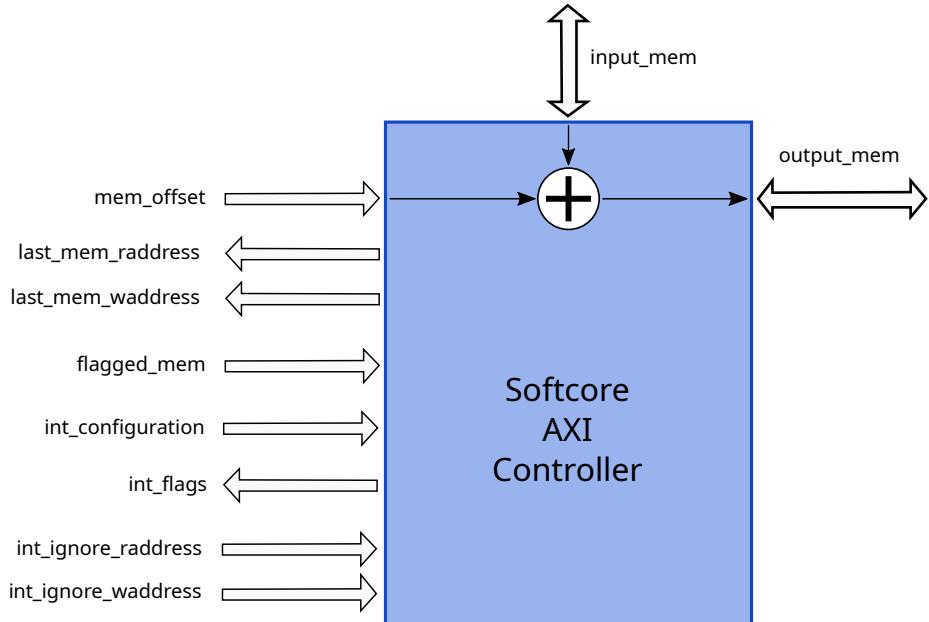

## 2.2.4. Softcore AXI Controller

El **Softcore AXI Controller** actúa principalmente como un *sniffer*. Se encarga de observar los accesos que realiza el **Sistema** a la **DDR** (en este caso, provenientes de la **L2**), así como de proveer información sobre estos al **Softcore Controller**.

Figura 2.5: Interfaz del componente **Softcore AXI Controller**.

Permite redireccionar los accesos a memoria sumándoles un *offset* (puerto `mem_offset`). En nuestro caso, este offset fue implementado como una constante no configurable por el **Softcore Controller** y equivale a 512 MB.

Además del *offset*, el *IP Core* guarda la última posición de memoria que fue leída/escrita en registros internos (expuestos a través de los puertos `last_mem_raddress` y `last_mem_waddress`). Ambos incluyen un bit que indica si la dirección es válida o no. Los registros son escritos de manera sincrónica con la modificación de `input_mem`.

En caso de un `reset`, ninguna posición será válida hasta la primera lectura/escritura.

Este *softcore* ofrece una forma de monitorear todos los accesos de memoria, ya sean lecturas o escrituras. En base a estos accesos, se modifican los *flags* R y W expuestos en `int_flags`, que señalan si se trata de una escritura o lectura respectivamente. Se pondrán en 1 cada una de estas señales, cuando se detecte que la señal de dirección de memoria sea válida y distinta a la anterior.

El **Softcore Controller** estará atento a los cambios de las señales `last_mem_raddress` y `last_mem_waddress`, y seteará las señales `int_ignore_raddress` e `int_ignore_waddress` copiando los valores de los arriba mencionados.

Luego, el **Softcore AXI Controller**, al identificar las modificaciones del registro de control `int_ignore_Xaddress` (donde X es `r` o `w`), seteará el *flag* indicado (R o W) en 0. Todo este proceso será explicado en detalle en la sección 2.2.5.

En términos generales, el *flag* será 1 cuando el último acceso a memoria sea válido y diferente de `int_ignore_Xaddress`, y será 0 en otro caso.

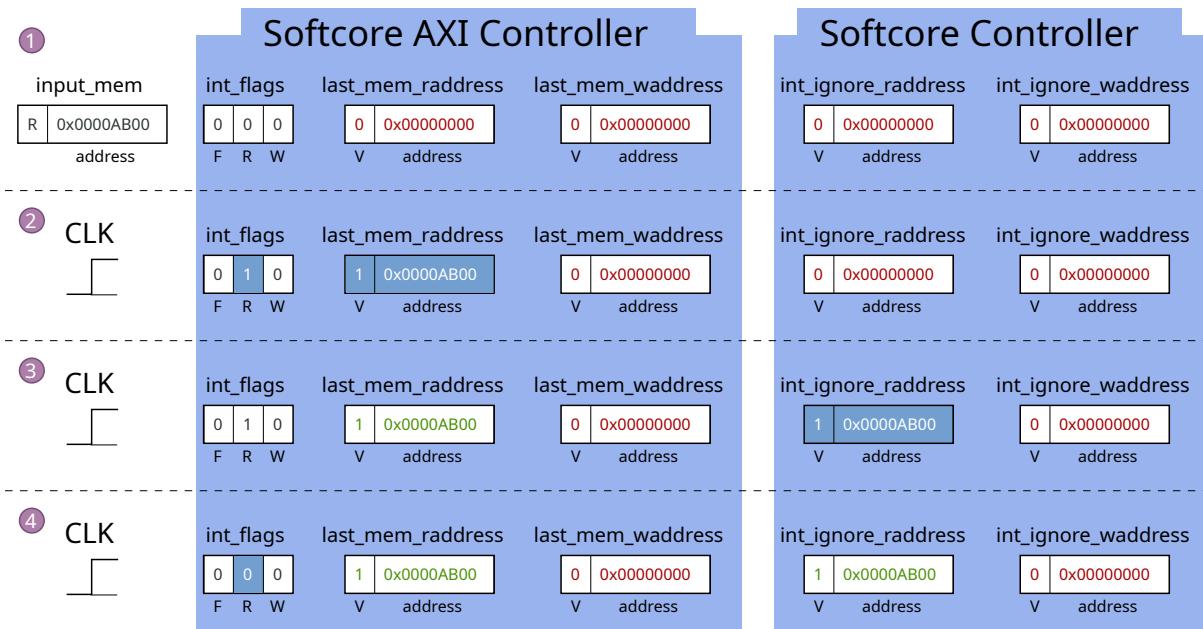

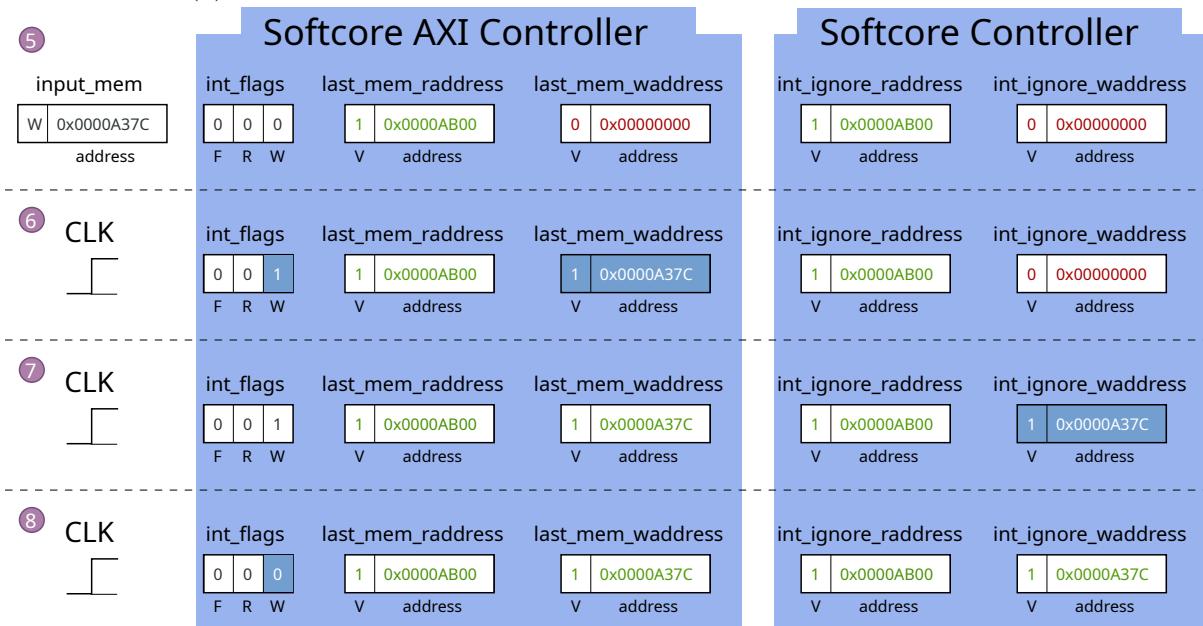

En la figura 2.6 podemos ver un ejemplo de una primera lectura a memoria, seguida por una primera escritura:

(a) Se detecta un pedido de lectura de memoria desde el **Sistema**.

(b) Se detecta un pedido de escritura de memoria desde el **Sistema**.

Figura 2.6: Un posible escenario post inicialización. Se indican los cambios que ocurren en las señales ante cada evento (lectura, escritura, **CLK**).

- 1 Post inicialización, todos los valores están en cero. Esto incluye los bits de validez de las direcciones. En algún momento, el **Sistema** hace un pedido de lectura a la posición 0x0000AB00, seteando la dirección en **input\_mem**.

- 2 Al recibir un pulso de *clock*, el **Softcore AXI Controller** se detecta el pedido en **input\_mem** y procede a copiar la dirección a **last\_mem\_raddress**, seteando su bit de validez en 1. Además, setea en 1 el flag R de **int\_flags**.

- 3 Durante el siguiente ciclo de *clock*, el **Softcore Controller** detecta el cambio en **last\_mem\_raddress** y setea **int\_ignore\_raddress**, copiando el valor del primero.

- ④ Un ciclo de *clock* más tarde, el **Softcore AXI Controller** verifica que `int_ignore_raddress` es la dirección actual de lectura según `input_mem` y procede a setear el flag R en 0.

- ⑤ En algún momento, el **Sistema** hace un pedido de escritura a la posición 0x0000A37C, seteando la dirección en `input_mem`.

- ⑥ Al recibir un pulso de *clock*, el **Softcore AXI Controller** se detecta el pedido en `input_mem` y procede a copiar la dirección a `last_mem_waddress`, seteando su bit de validez en 1. Además, setea en 1 el *flag* W de `int_flags`.

- ⑦ Durante el siguiente ciclo de *clock*, el **Softcore Controller** detecta el cambio en `last_mem_waddress` y setea `int_ignore_waddress`, copiando el valor del primero.

- ⑧ Un ciclo de *clock* más tarde, el **Softcore AXI Controller** verifica que `int_ignore_waddress` es la dirección actual de escritura según `input_mem` y procede a setear el flag W en 0.

El CLK del **Softcore Controller** es el mismo que el CLK del puerto `input_mem`, por lo cual estas señales se modifican de manera sincrónica.

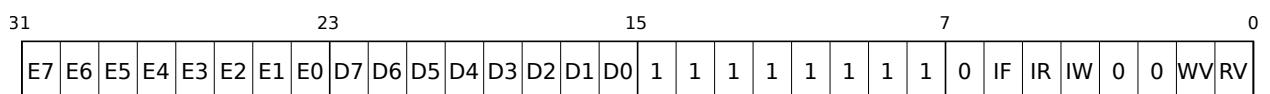

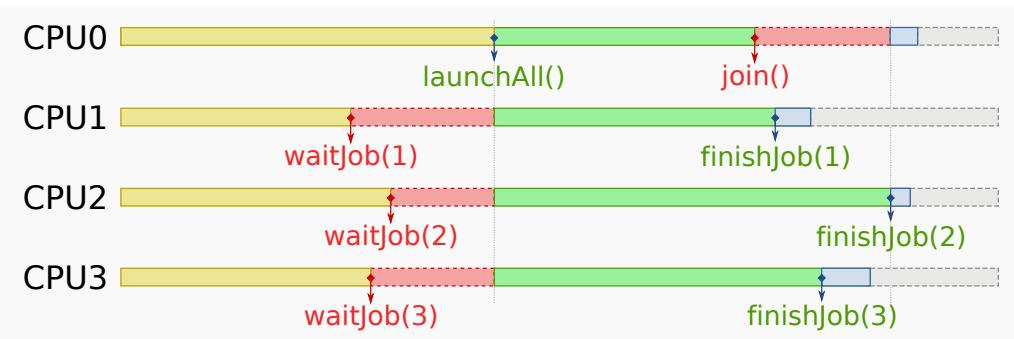

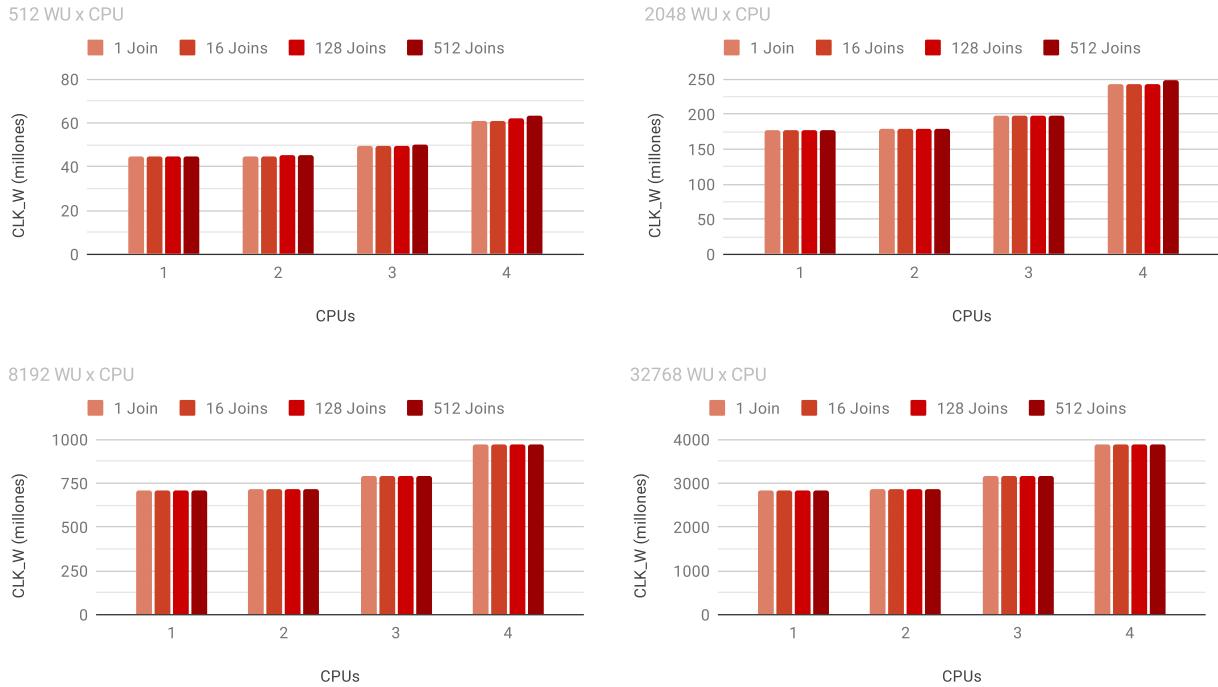

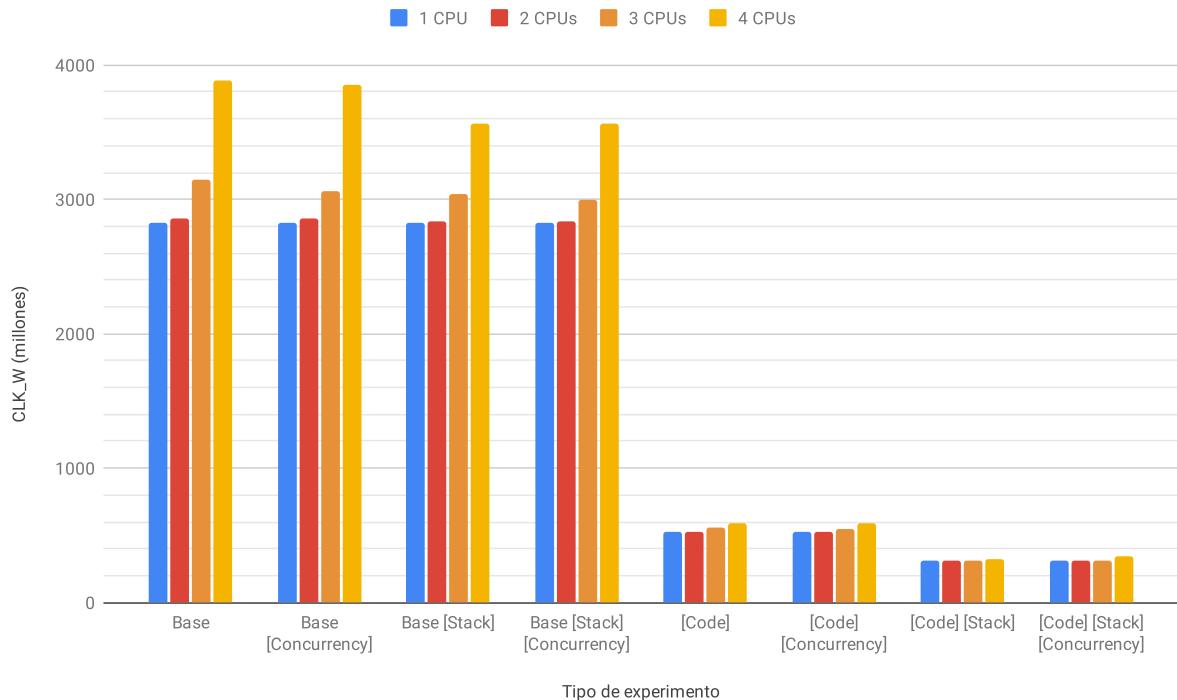

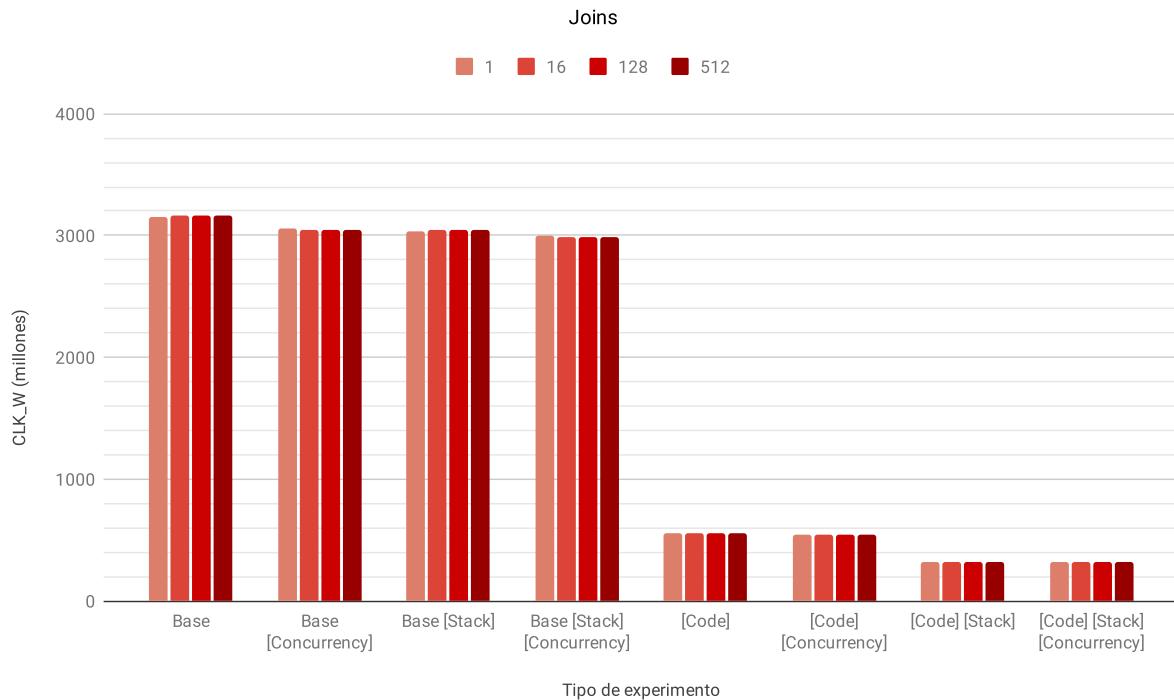

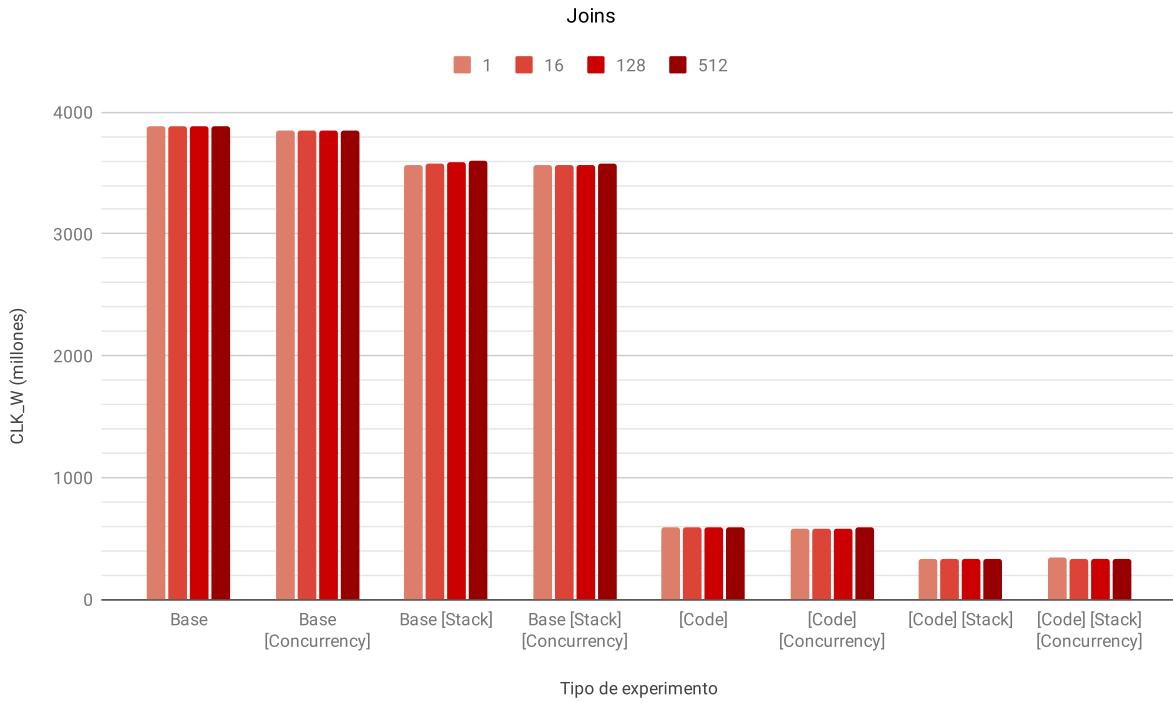

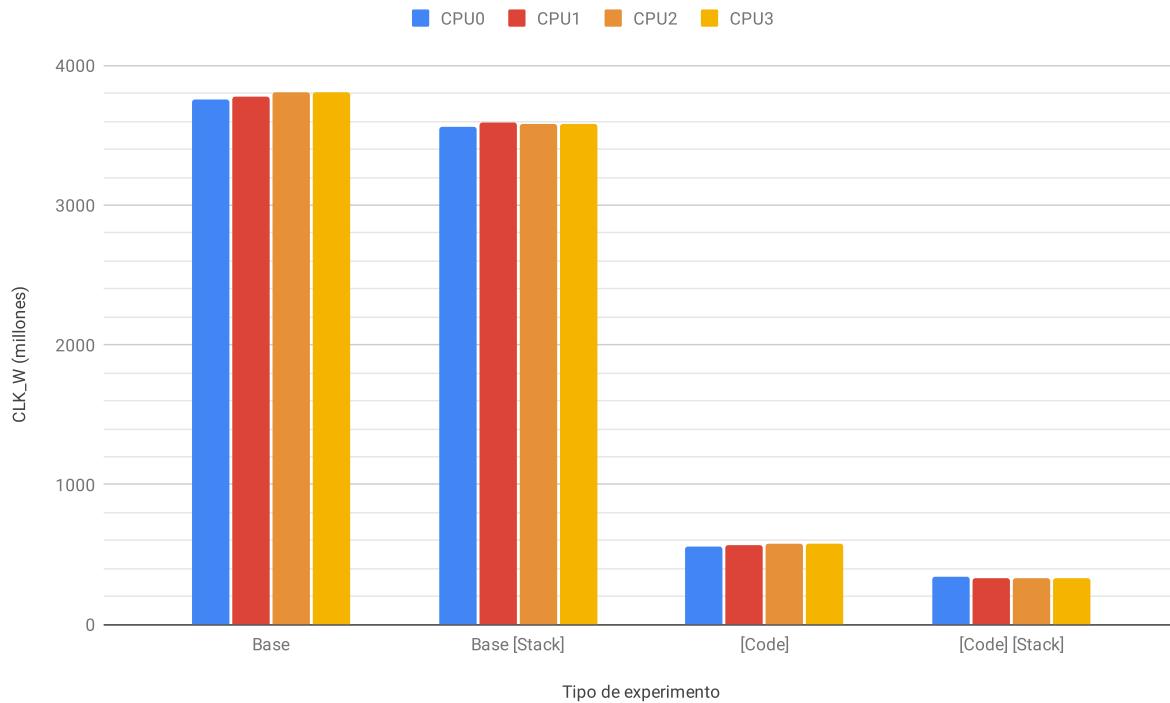

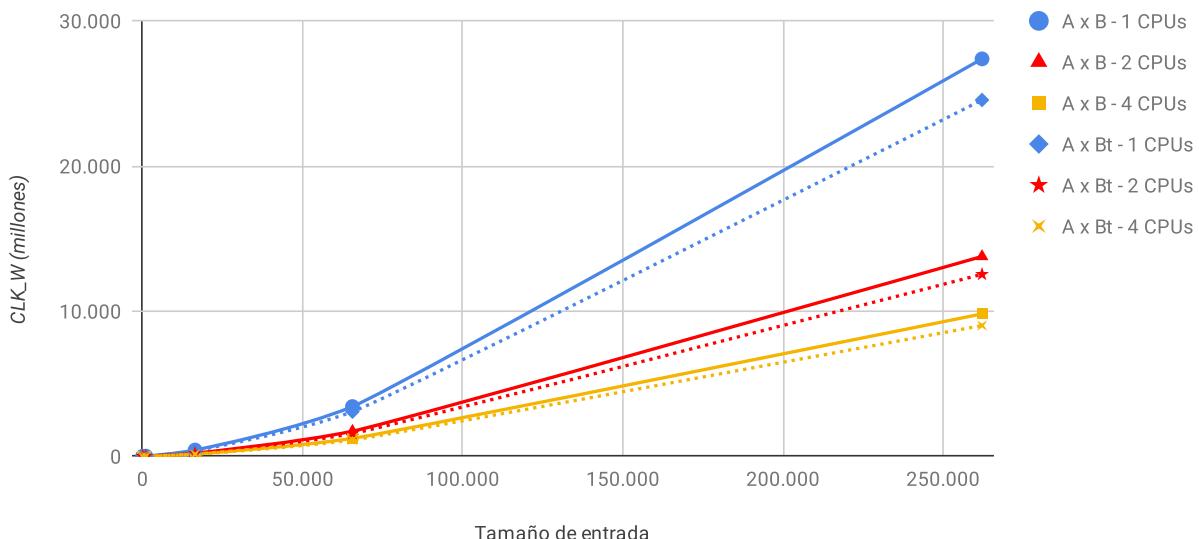

El **Sistema** implementado en este trabajo posee una *cache L2*. Esto significa que los valores que llegan por `input_mem` serán únicamente los *cache misses* y los *flushes* de la *L2*. En un **Sistema** sin *cache* sería posible utilizar esta información para *debuggear* los accesos a memoria hechos por la ejecución del programa.